Preview text:

CHỦ ĐỀ 6

MÁY TRẠNG THÁI HỮU HẠN (FSM) NỘI DUNG

❖ Máy trạng thái hữu hạn (Finite State Machine - FSM) là gì?

❖ Mô hình FSM trong thiết kế mạch số đồng bộ

❖ Sơ đồ máy trạng thái (State machine diagram) ❖ Tóm tắt

1. Máy trạng thái hữu hạn FSM là gì?

➢ Máy trạng thái hữu hạn FSM (Finite State Machine):

o Là mô hình mô tả hoạt động của mạch tuần tự (sử dụng

phổ biến trong thiết kế vi mạch số)

o Có số trạng thái hữu hạn

➢ Phân loại mô hình FSM: 02 loại o Mô hình Moore (Moore FSM) o Mô hình Mealy (Mealy FSM) 3

1. Máy trạng thái hữu hạn FSM là gì?

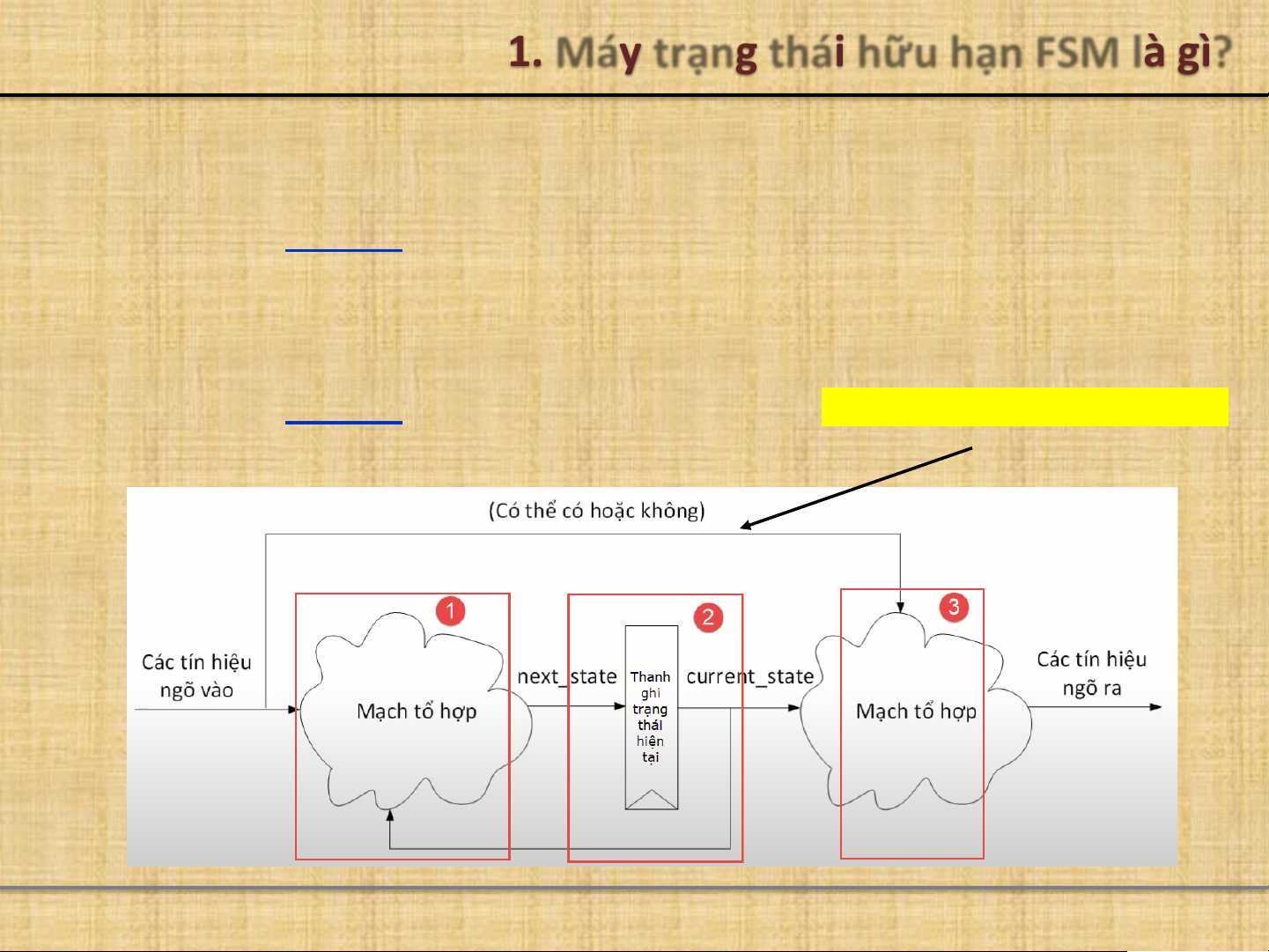

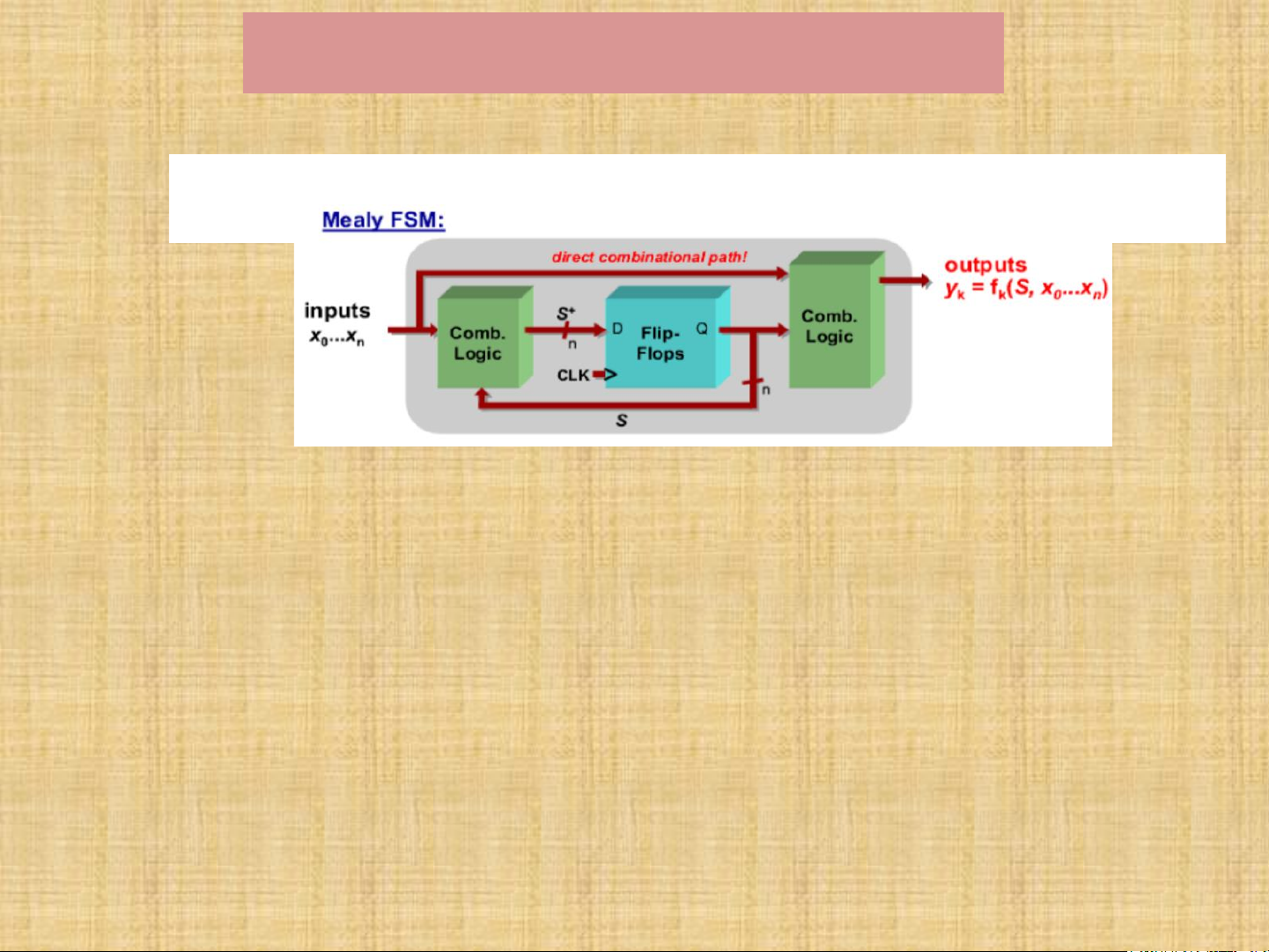

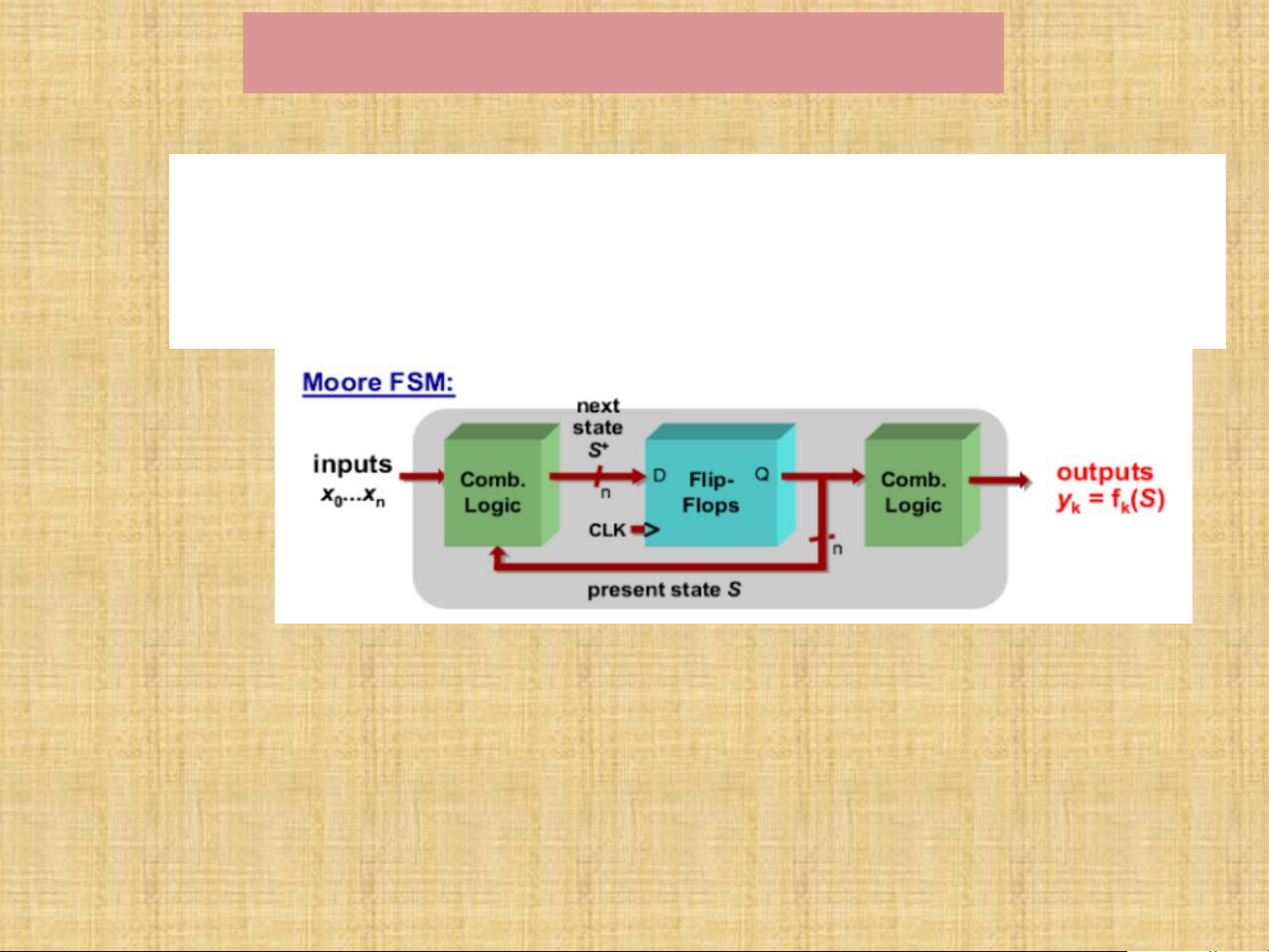

➢ FSM có 3 thành phần cơ bản:

o Mạch tổ hợp xác định trạng thái kế tiếp (next state)

o Thanh ghi trạng thái (các FF) lưu giữ trạng thái hiện tại (current state)

o Mạch tổ hợp xác định giá trị ngõ ra Đường này quyết định loại FSM 4

4.2. Mô hình của hệ tuần tự

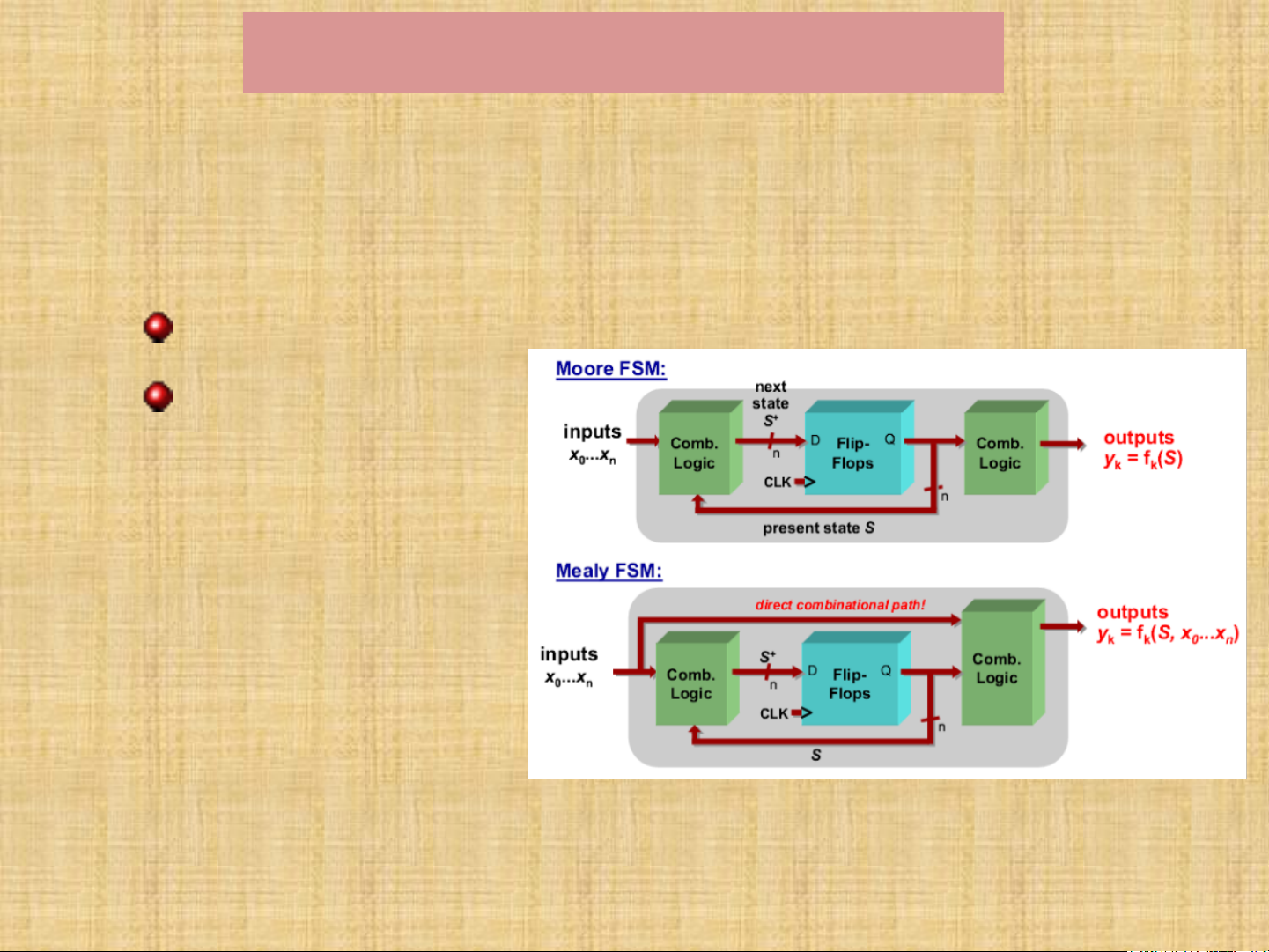

▪ Phân loại: Có 2 loại mô hình trạng thái (Finite State Machine- FSM) Mô hình Mealy Mô hình Moore

4.2. Mô hình của hệ tuần tự

▪ Mô hình Mealy: mô tả hệ dãy thông qua 5 tham số:

▪ X : tập hữu hạn các tín hiệu vào. Nếu hệ có n đầu vào

→ các tín hiệu vào tương ứng là x1,x2...,xn

▪ S : tập hữu hạn các trạng thái. Nếu hệ có n trạng thái

→ các trạng thái tương ứng là s1,s2...,sm

▪ Y: tập hữu hạn các tín hiệu ra. Nếu hệ có k đầu ra ta có các tín

hiệu ra tương ứng là y1,y2...,yk

▪ Fs: hàm trạng thái. →Fs = Fs(X,S)

▪ Fy : hàm ra. →Fy = Fy(X,S)

4.2. Mô hình của hệ tuần tự

▪ Mô hình Moore: cũng mô tả hệ dãy thông qua 5 tham số

nhưng khác ở chỗ là FY chỉ phụ thuộc vào S: ▪ FY = FY(S)

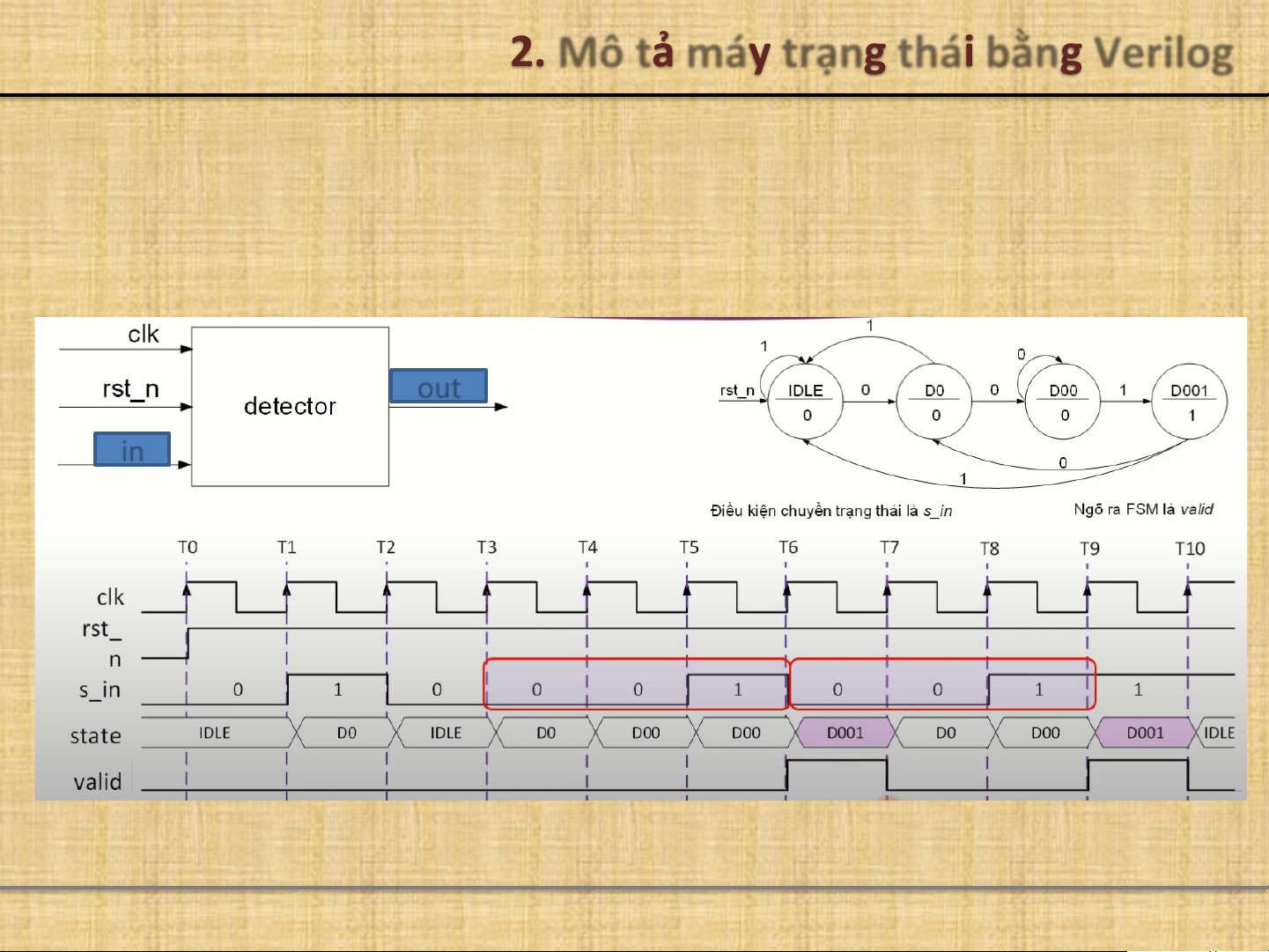

2. Mô tả máy trạng thái bằng Verilog ➢ Máy trạng thái FSM:

Thiết kế một bộ phát hiện và báo hiệu sự xuất hiện của một

chuỗi bit 001 liên tiếp (mô hình Moore). out in 8

2. Mô tả máy trạng thái bằng Verilog

➢ Các bước thực hiện:

o Mã hóa trạng thái: Gán một giá trị hằng số riêng biệt cho mỗi trạng thái.

o Viết RTL code cho mạch tạo trạng thái kế tiếp (mạch tổ hợp)

o Viết RTL code cho thanh ghi trạng thái (mạch tuần tự)

o Viết RTL code cho mạch tạo ngõ ra (mạch tổ hợp) 9

2. Mô tả máy trạng thái bằng Verilog

➢ Bước 1: Mã hóa trạng thái

▪ Mạch có 4 trạng thái là IDLE, D0, D00, D001 do đó có thể dùng

mã nhị phân 2 bit để mã hóa trạng thái. o IDLE = 0 (2’b00) o D0 = 1 (2’b01) o D00 = 2 (2’b10) o D001 = 3 (2’b11)

• RTL code: Dùng khai báo parameter hoặc localparam parameter IDLE = 2'b00; parameter D0 = 2'b01; parameter D00 = 2'b10; parameter D001 = 2'b11; 10

2. Mô tả máy trạng thái bằng Verilog

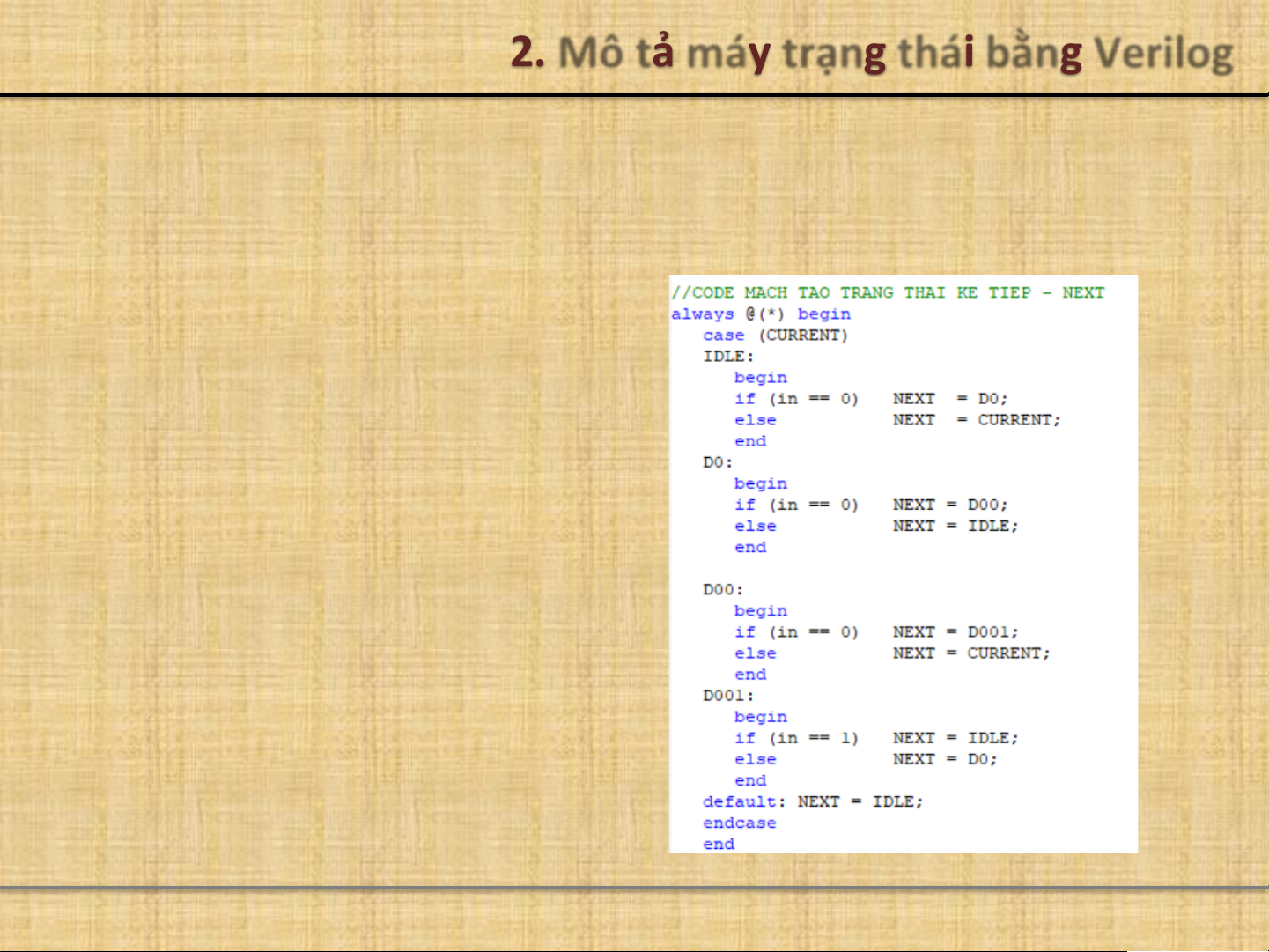

➢ Bước 2: Mạch tạo trạng thái kế tiếp

Dựa vào sơ đồ trạng thái để viết RTL code cho mạch tổ hợp

(thường dùng cấu trúc lệnh case) 11

2. Mô tả máy trạng thái bằng Verilog

➢ Bước 3: Thanh ghi trạng thái Chú ý đến chân reset 12

2. Mô tả máy trạng thái bằng Verilog

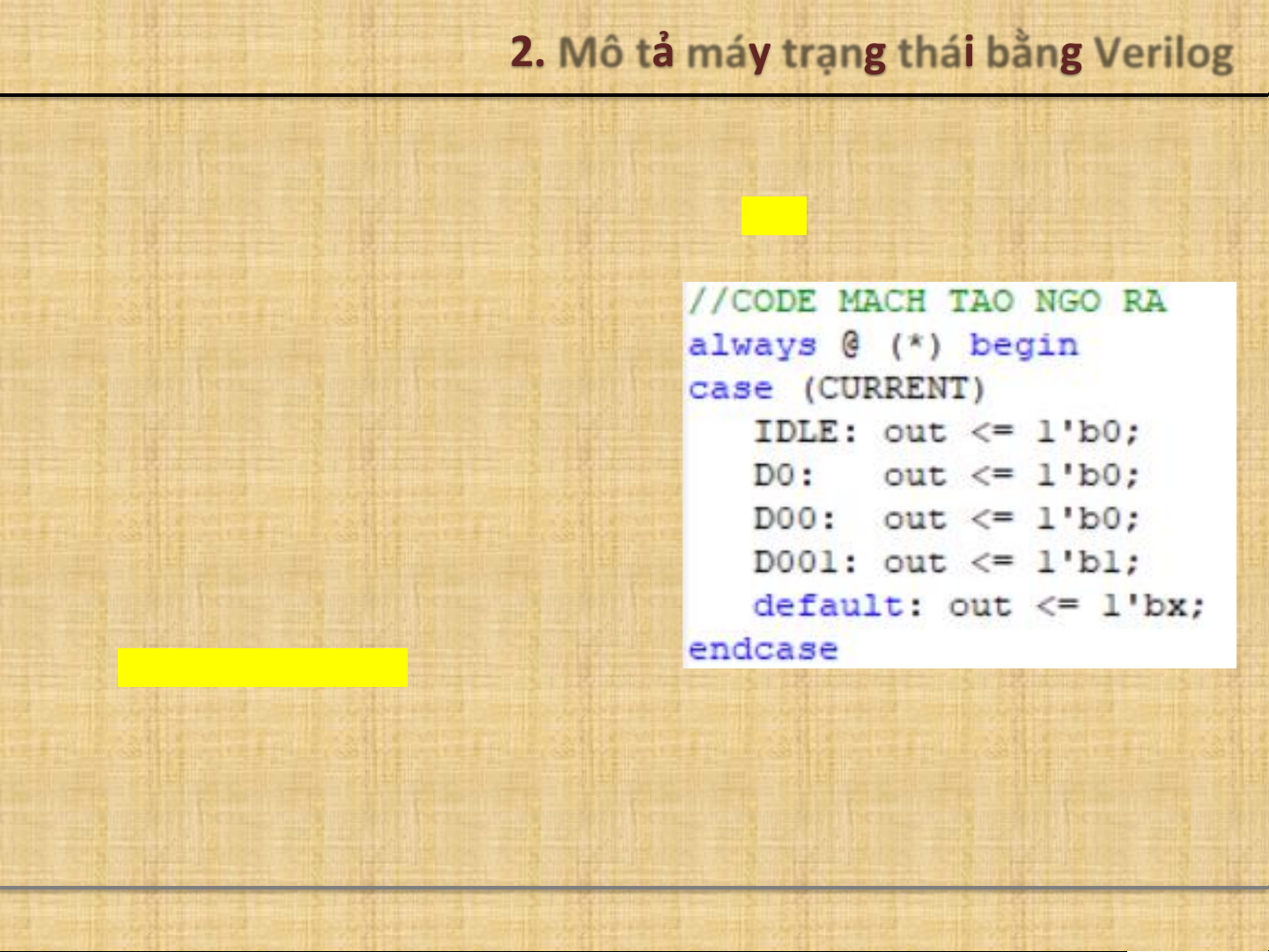

➢ Bước 4: Mạch tạo ngõ ra Hoặc always @ (*) begin if (CURRENT == D001) out = 1'b1; else out = 1'b0; end

Hoặc dùng lệnh assign

assign out = (CURRENT == D001) ? 1’b1 : 1’b0 ; 13

2. Mô tả máy trạng thái bằng Verilog

➢ RTL code hoàn chỉnh 14

Document Outline

- Slide 1: CHỦ ĐỀ 6

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14