Preview text:

Chương 1:

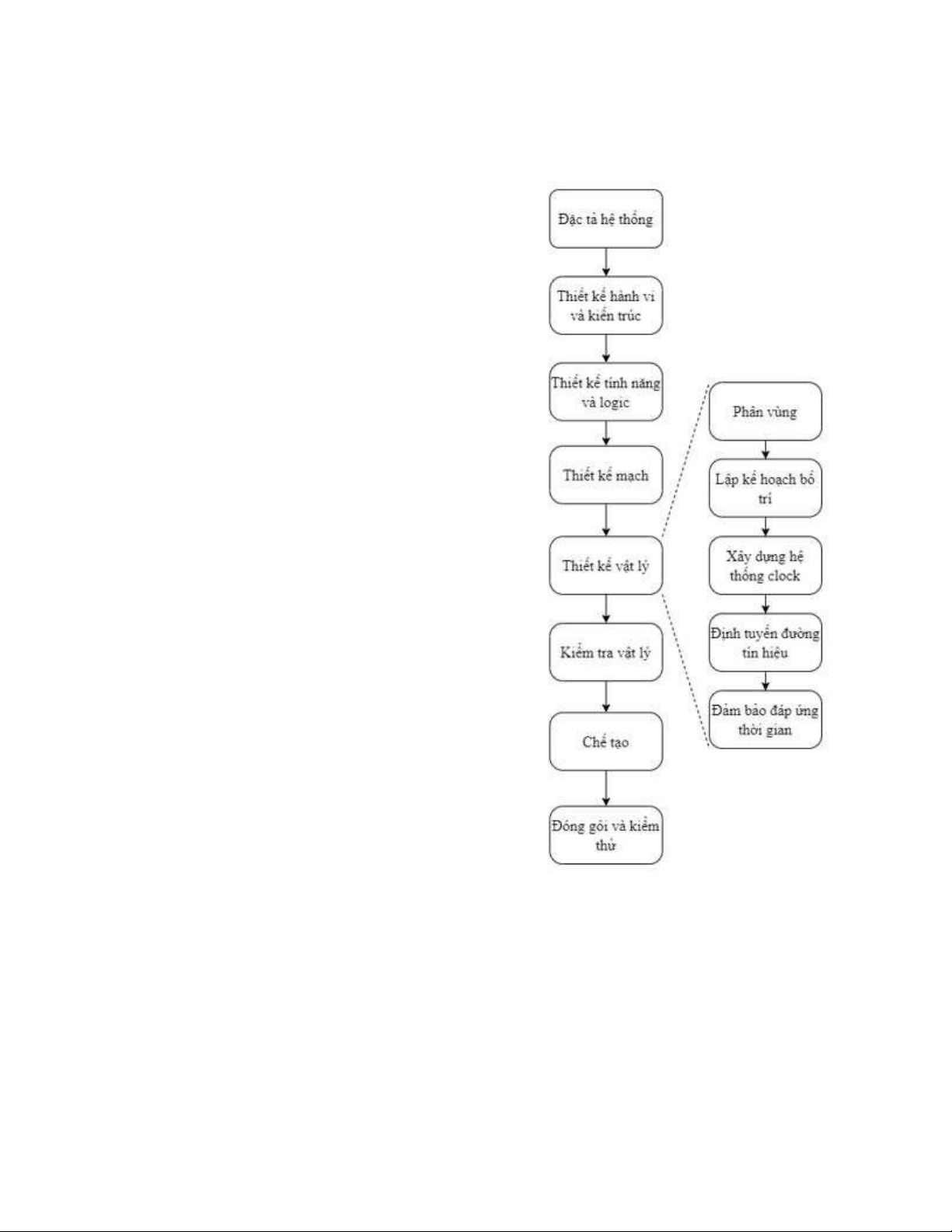

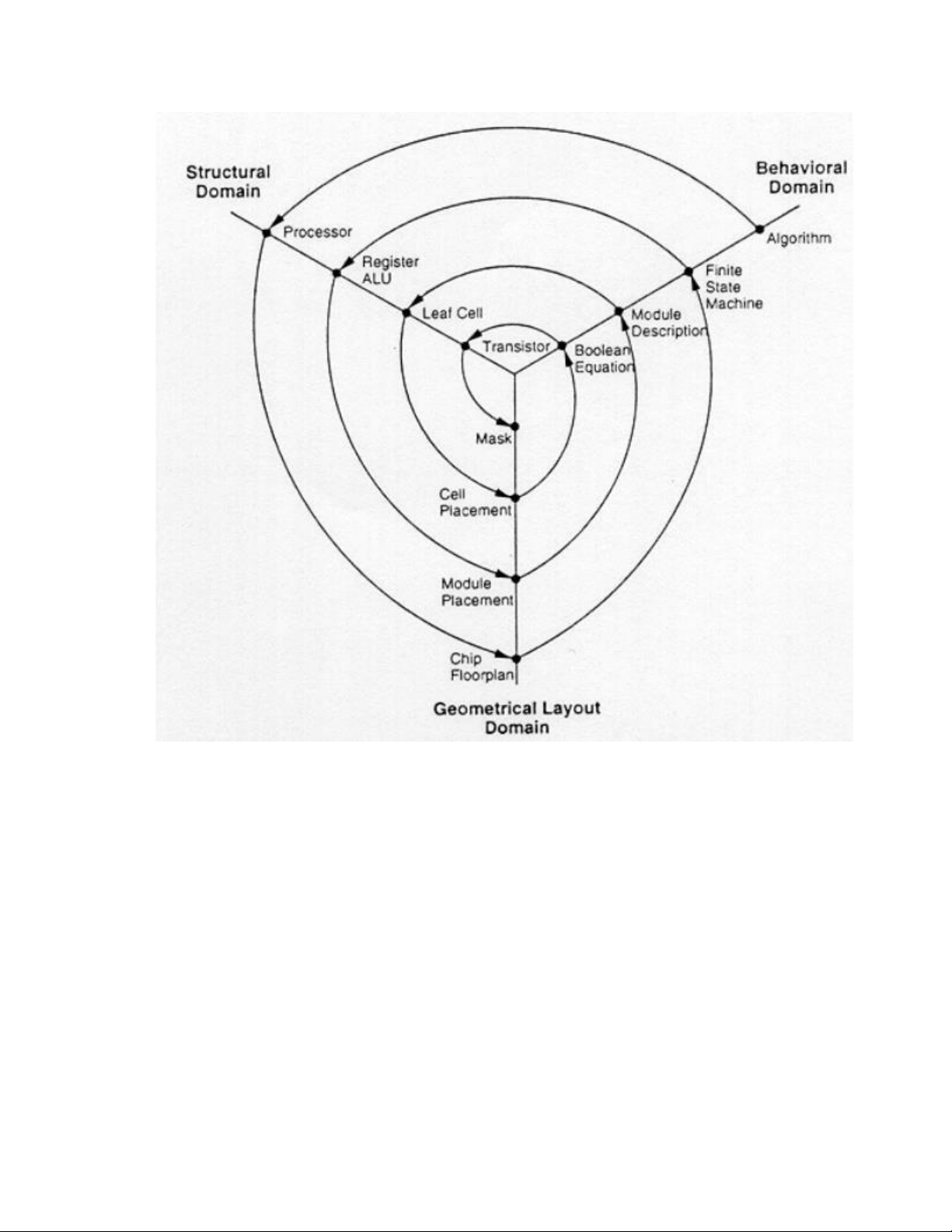

- Chu trình thiết kế VLSI: - Giản ồ chữ Y: + Vùng cấu trúc

+ Vùng thiết kế hình học + Vùng hành ộng

+ Luôn có sự tương tác chặt chẽ giữa 3 vùng theo hình xoắn ốc

- Các kiểu thiết kế VLSI: Có 3 kiểu thiết kế

+ Full custom design: dạng thức hình học và vị trí của mọi trans ược tìm kiếm và

xác ịnh tối ưu 1 cách ặc biệt, thiết kế theo yêu cầu khách hàng hoặc tùy chọn theo ý người thiết kế.

+ Semi custom design: dựa trên các cấu trúc cơ bản trên mỗi cell chuẩn / macro.

+ Programmable design: FPGA, ASIC, SoC/NoC.

+ Lựa chọn các thiết kế VLSI phụ thuộc vào yêu cầu chất lượng của thiết kế và

con người sử dụng, thời gian sử dụng, thời gian tung ra thị trường, chi phí sản xuất.

- Các phương pháp óng gói: DIP (Dual Inline Package), QFP (Quad Flat Package),

SOP (Small Outline Package), BGA (Ball Grid Array).

- Bài toán phân hoạch wafer chia theo chip ể có hiệu quả tối ưu nhất:

Số lượng die trên 1 tấm wafer: 𝐷 2 𝜋∗( 2 ) = 𝜋∗𝐷 NDPW = 𝐴 √ 2∗ 𝐴

A: là diện tích 1 miếng die

D: là ường kính tấm wafer, thường ược tạo từ phiến SOI kinh 20-30cm Sản

lượng tính trên 1 tấm wafer:

Y= 𝑆ố 𝑙ượ𝑛𝑔 𝑐ℎ𝑖𝑝 𝑡ố𝑡 𝑡ℎ𝑢 đượ𝑐 𝑡ừ 1 𝑡ấ𝑚 𝑤𝑎𝑓𝑒𝑟 x 100%

𝑇ổ𝑛𝑔 𝑠ố 𝑐ℎ𝑖𝑝 𝑡𝑟ê𝑛 1 𝑡ấ𝑚 𝑤𝑎𝑓𝑒𝑟 Giá thành 1 die: DC=

𝐺𝑖á 𝑡ℎà𝑛ℎ 1 𝑡ấ𝑚 𝑤𝑎𝑓𝑒𝑟 = f (diện tích 𝑑𝑖𝑎4) 𝑁𝐷𝑃𝑊∗𝑌 Sản lượng của die: DY= 𝐷

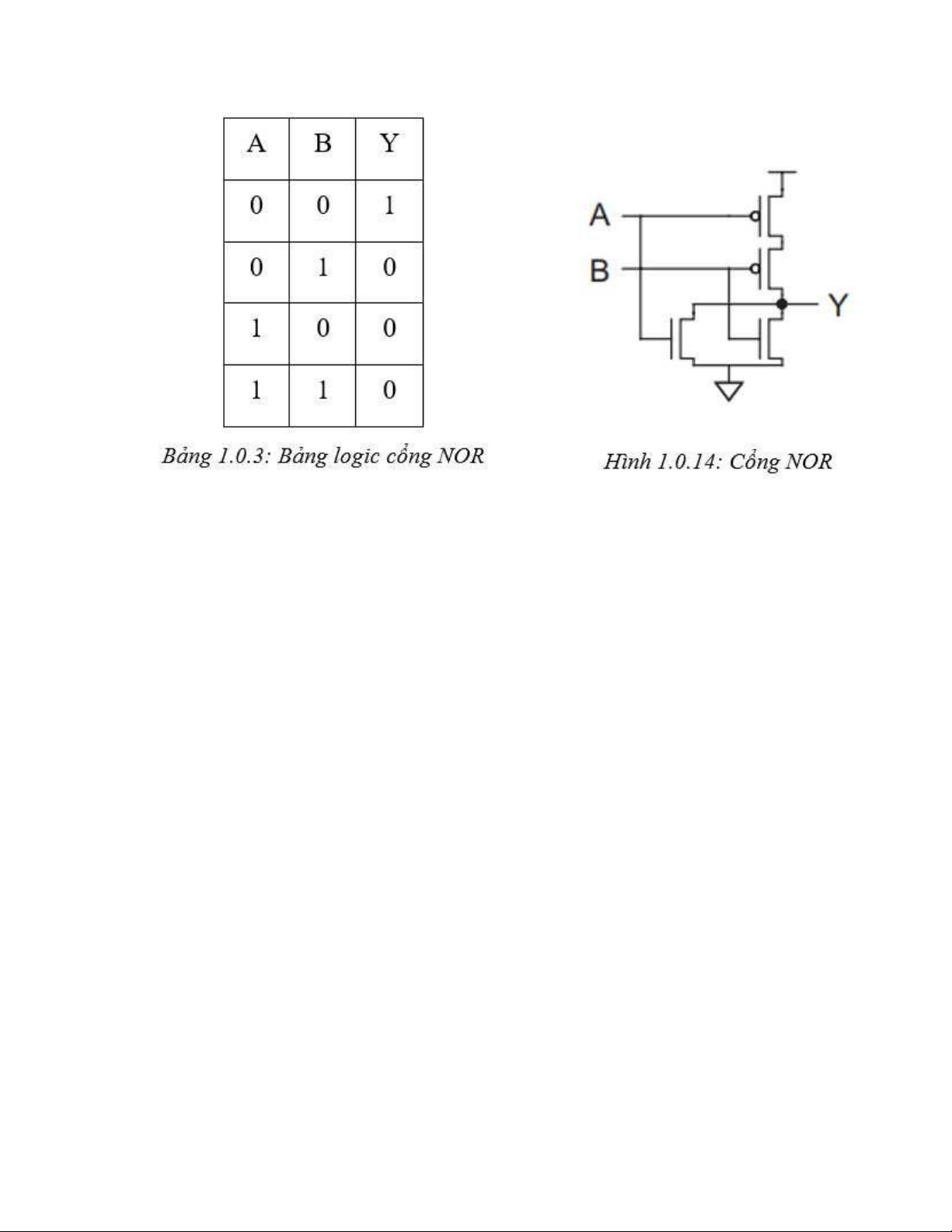

Ad: là dtich 1 miếng die α: là hệ số hiệu chỉnh thực nghiệm - Các cổng thiết kế: + Cổng ảo( Inverter): + Cổng NAND: + Cổng NOR:

- Nguyên lý tổng quát thiết kế mạch VLSI:

+ Nguyên lý thiết kế ảo: Luôn là thiết kể ảo ể có lợi về khuếch ại

Khuếch ại cho cả mức 0 và mức 1

Khi cấu trúc không ảo thì chỉ cần cho i qua cổng ảo.

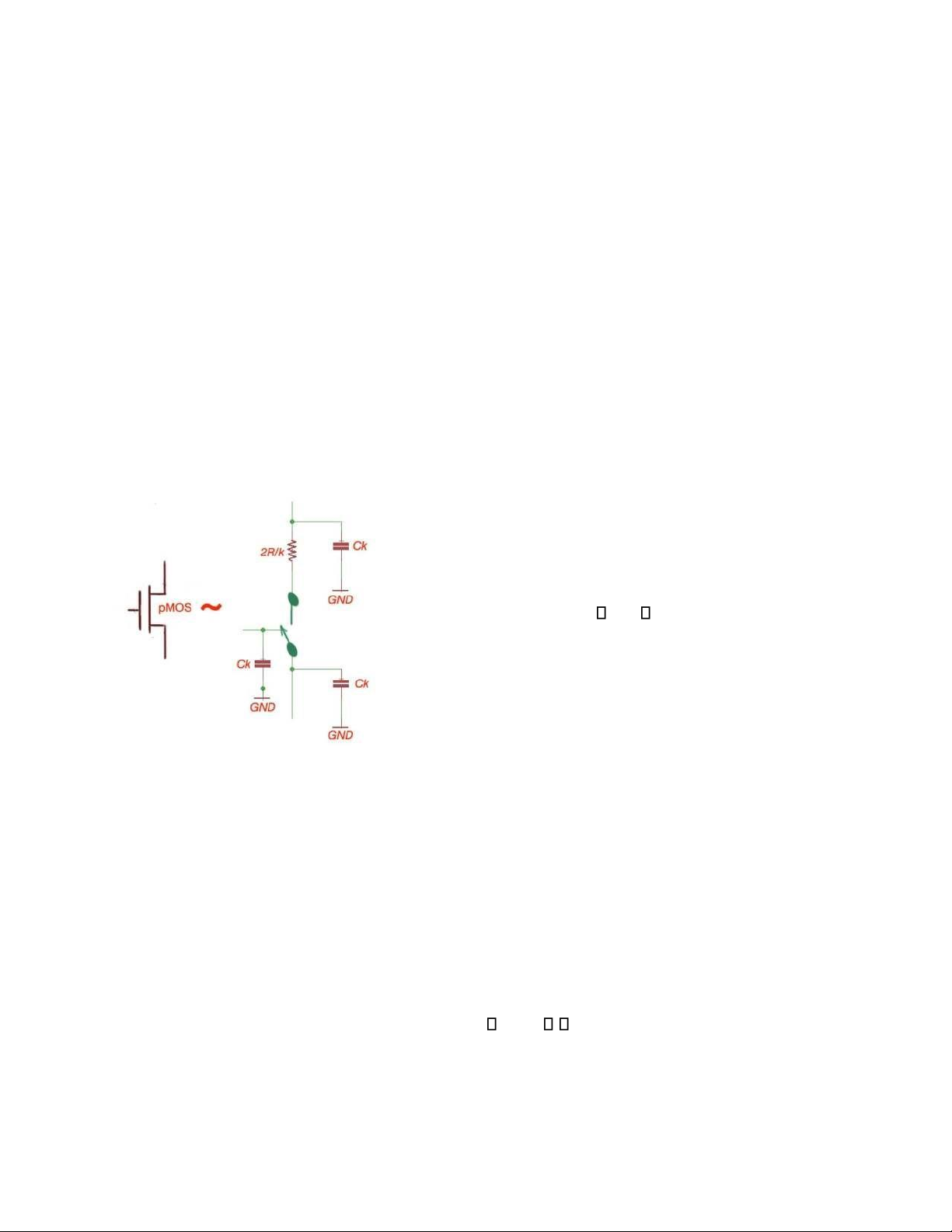

+ Nguyên lý 2 tầng pull up- pull down: Tầng pull up là chỉ gồm các transistor

pMOS và ấu với VDD, Tầng pull down chỉ gồm các transistor nMOS ấu với GND.

Cổng ra luôn lấy iểm giữa 2 tầng.

Tầng pull up và pull down luôn ngược nhau về tính nối tiếp, song song. VD: pull

up là nối tiếp thì pull down là song song và ngược lại.

Nguyên lý ẩy kéo cả trên xuống như vậy giúp mạch chạy ầy ủ, ổn ịnh, không bị

ấu tắt, rò, tiết kiệm năng lượng khi ở trạng thái nghỉ, khuếch ại cả mức 0,1.

- Các mạch tổ hợp và tuần tự cơ bản:

Mấy mạch còn lại ọc trong slide chương 2 cho dễ nhìn. Chương 2:

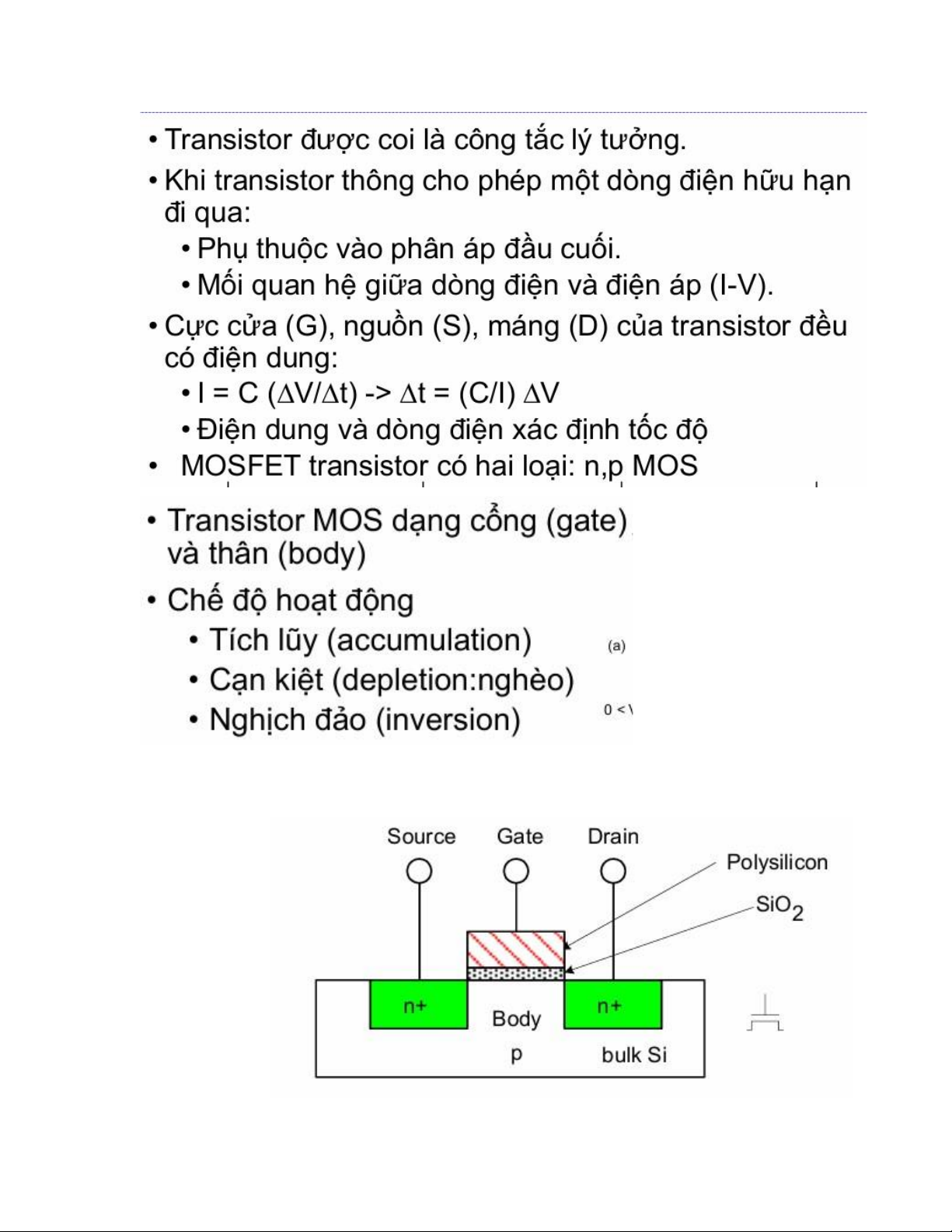

Các vấn ề cơ bản về lý thuyết transistor MOSFET và công nghệ CMOS: - nMos transistor:

4 ầu cuối: cổng, cực nguồn, cực máng, thân.

Cổng – oxit ngăn cách vai trò như tụ

Cổng và thân dẫn Sio2 (oxit) -> chất cách iện

Được gọi là bán dẫn kim loại

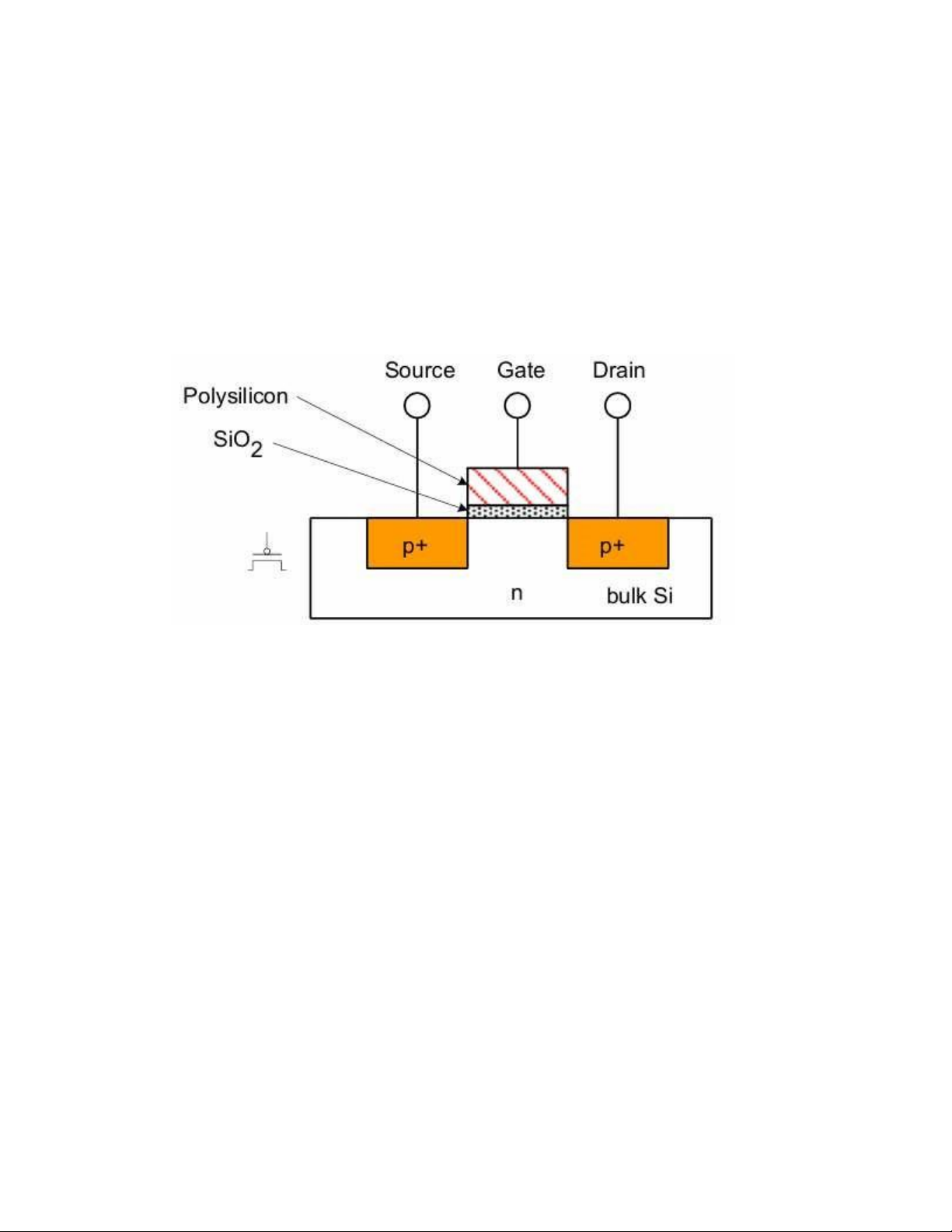

Mặc dù cổng ko còn ược làm = kim loại. Thân ược nối ất - pMos transistor:

Tương tự nhưng pha tạp và iện áp ảo ngược

Thân ược nối với iện áp cao Gate low: Transistor ON Gate high: Transistor OFF

Bóng biểu thị hành vi ảo ngược

- Các dạng rò rỉ: 1.

Rò rỉ dòng ngược (Subthreshold Leakage):

o Xảy ra khi Vgso Tăng ở nhiệt ộ cao hoặc khi LLL ngắn. 2.

Rò rỉ qua lớp oxide (Gate Oxide Leakage):

o Do xuyên hầm iện tử qua lớp oxide mỏng. 3.

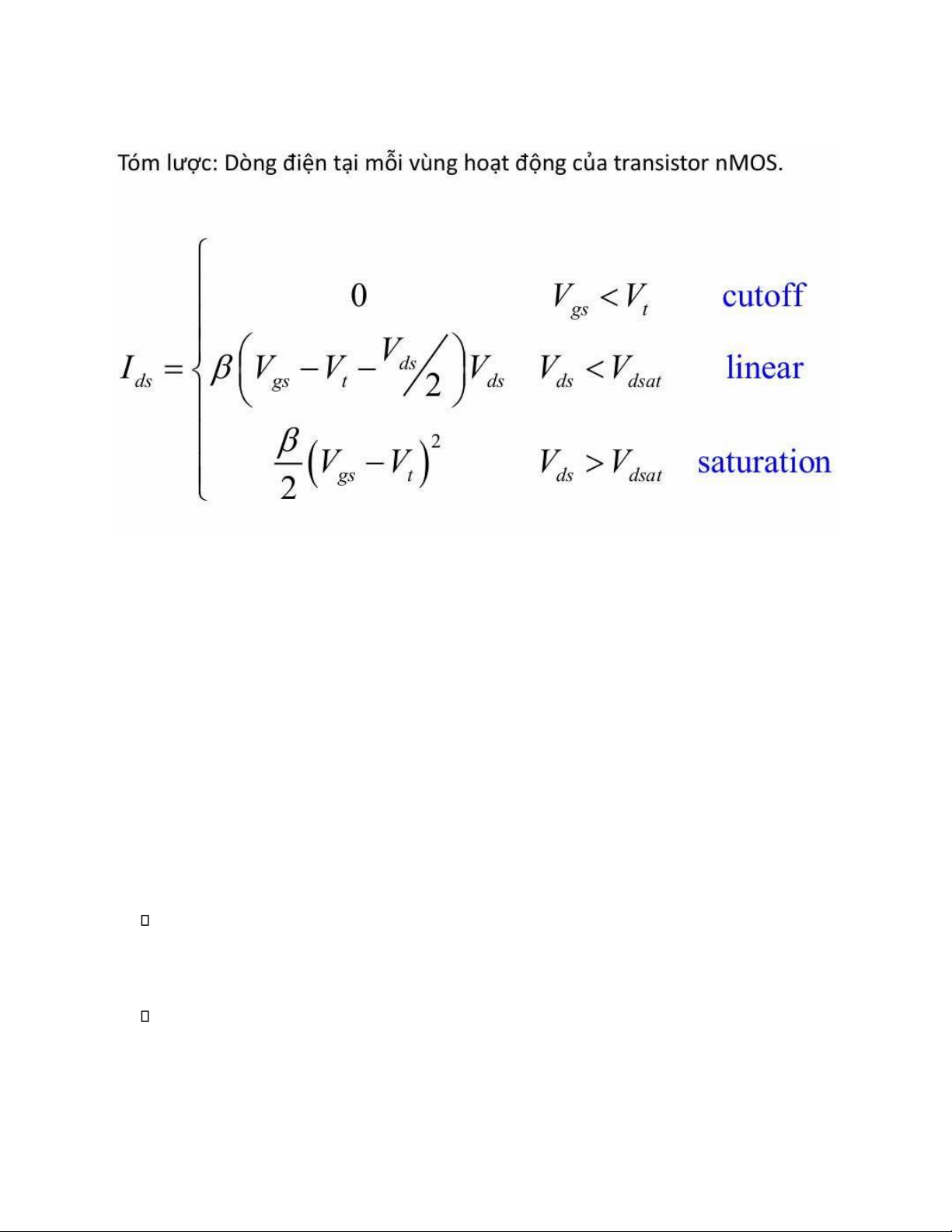

Rò rỉ giữa máng và nguồn (Junction Leakage): o Do dòng nhiệt hạt dẫn chảy qua vùng tiếp xúc PN. - Đặc tuyến I-V: Tuyến tính Bão hòa

- Đặc tuyến C-V: Điện dung cổng ảnh hưởng trực tiếp ến hiệu suất dẫn của

transistor, trong khi iện dung ký sinh là yếu tố không mong muốn cần ược kiểm

soát ể tối ưu hóa hiệu suất mạch.

- Kỹ thuật tạo phiến wafer Vật liệu:

o Wafer thường ược làm từ silicon (Si), ôi khi từ gallium arsenide (GaAs) hoặc vật liệu khác. Quy trình: 2.

Kéo tinh thể Czochralski (CZ):

▪ Silicon tinh khiết ược nung chảy và kéo thành khối tinh thể hình trụ. 3. Cắt lát:

▪ Khối tinh thể ược cắt thành lát mỏng (wafer) bằng dao kim cương. 4. Đánh bóng: ▪

Bề mặt wafer ược ánh bóng ể ạt ộ phẳng và mịn. 5. Làm sạch:

▪ Loại bỏ tạp chất và chuẩn bị cho các bước chế tạo tiếp theo.

- Phương pháp quang khắc bằng DUV Photolithography Nguyên lý:

o Dùng ánh sáng cực tím bước sóng ngắn (Deep Ultraviolet - DUV, ~193 nm)

chiếu qua mask ể khắc hình lên lớp nhạy sáng (photoresist) trên bề mặt wafer. Quy trình: 2.

Phủ lớp photoresist lên wafer. 3.

Chiếu ánh sáng DUV qua mask. 4.

Rửa lớp photoresist ể lộ các vùng cần khắc. 5.

Ăn mòn hóa học hoặc khắc plasma ể tạo cấu trúc. Ứng dụng:

o Được dùng phổ biến trong sản xuất CMOS với các kích thước dưới 7 nm.

1. Sự hình thành giếng và kênh Giếng (Well):

o N-well cho pMOS, P-well cho nMOS. o Được hình thành bằng cách khuếch tán

hoặc cấy ion (ion implantation) các tạp chất loại n hoặc p vào wafer silicon. • Kênh (Channel):

o Hình thành giữa cực nguồn và cực máng khi có iện trường từ cực cổng.

o Kênh dẫn nMOS ược tạo bởi các electron (loại n), còn kênh dẫn pMOS ược tạo

bởi lỗ trống (loại p).

2. Sự hình thành cực cổng • Quy trình:

1. Tạo lớp oxide cổng: SiO₂ mỏng ược mọc lên trên bề mặt wafer.

2. Tạo lớp cực cổng: Thường là polysilicon ược phủ lên lớp oxide và khắc ể ịnh hình. • Vai trò:

o Điều khiển dòng dẫn trong kênh qua iện trường.

3. Các tiếp xúc (Contacts) Chức năng: o Kết nối các vùng bán dẫn (nguồn,

máng) và kim loại liên kết. • Quy trình: 1.

Khắc mở lớp cách iện (oxide). 2.

Phủ kim loại (thường là tungsten hoặc titanium) vào vùng tiếp xúc.

Quy tắc về transistor •

Mask vật lý: Gồm active, n-select, p-select, và polysilicon. •

Cực transistor: Xác ịnh tại giao iểm của polysilicon và vùng active. • Loại khuếch tán:

o nMOS: Khuếch tán n trong p-well. o pMOS: Khuếch tán p trong n-well. •

Quy tắc thiết kế:

o Polysilicon phải mở rộng ra khỏi active (phần mở rộng cổng). o Giãn cách cần

thiết giữa active và polysilicon.

Quy tắc về tiếp iểm • Loại tiếp iểm:

o Kim loại ến n-active, p-active, polysilicon, hoặc giếng. • Kết nối giếng:

o n-well: Nối VDD. o p-well: Nối GND. • Quy tắc:

o Đặt vùng hoạt ộng pha tạp cao dưới tiếp iểm.

o Dùng nhiều tiếp iểm ể cải thiện ộ tin cậy.

Quy tắc về kim loại •

Quy ịnh: o Fat-metal: Khoảng cách tăng theo chiều rộng dây. o Chiều rộng tối a:

Dây lớn chia thành các dây song song nhỏ. o Dây song song gần nhau phải ảm

bảo khoảng cách tối thiểu. •

Quy trình hiện ại:

o Duy trì quy tắc chiều rộng và khoảng cách nhưng không bị ảnh hưởng bởi cấu trúc liên kết cũ.

Quy tắc về lối i (Wirebonding) Lối i xếp chồng:

o Có thể ặt trên vùng polysilicon hoặc khuếch tán. • Ranh giới:

o Tránh lối i ngoài ranh giới polysilicon hoặc khuếch tán trong quy trình cũ. •

Hiện ại: Cho phép lối i xếp chồng, giảm diện tích truyền kim loại giữa các lớp. 9. Luật Lambda • Mục tiêu:

o Đơn giản hóa thiết kế bằng cách chuẩn hóa kích thước và khoảng cách. • Quy tắc:

o Kích thước và khoảng cách ược biểu diễn dưới dạng bội số của một ơn vị chuẩn

hóa λ (lambda). o Ví dụ: Độ rộng tối thiểu =2λ, khoảng cách tối thiểu =λ

- Các phần tử trong mạch vlsi: Tụ iện, iện trở, cuộn cảm, ường truyền, tran lưỡng

cực, DRAM, bộ nhớ tĩnh, Đề bài Chương 3

Nêu về trễ, mô hình trễ RC, mô hình trễ tuyến tính, trễ trong các phần tử mạch

và mạng kết nối cổng logic, các nhánh

Nêu về các họ mạch CMOS tĩnh, các kiểu ẩy bọt, hiệu ứng trễ ầu vào, quy

tắc nonoverlapping, hiện tượng skewed trong mạch, mạch tổ hợp ộng

Thiết kế mạch tổ hợp, tính trễ, vẽ layout biểu diễn và khai báo verilog, VHDL

cho mạch tổ hợp Chương 4:

Nêu về trình tự mạch tĩnh và ràng buộc về ộ trễ, thời gian chờ

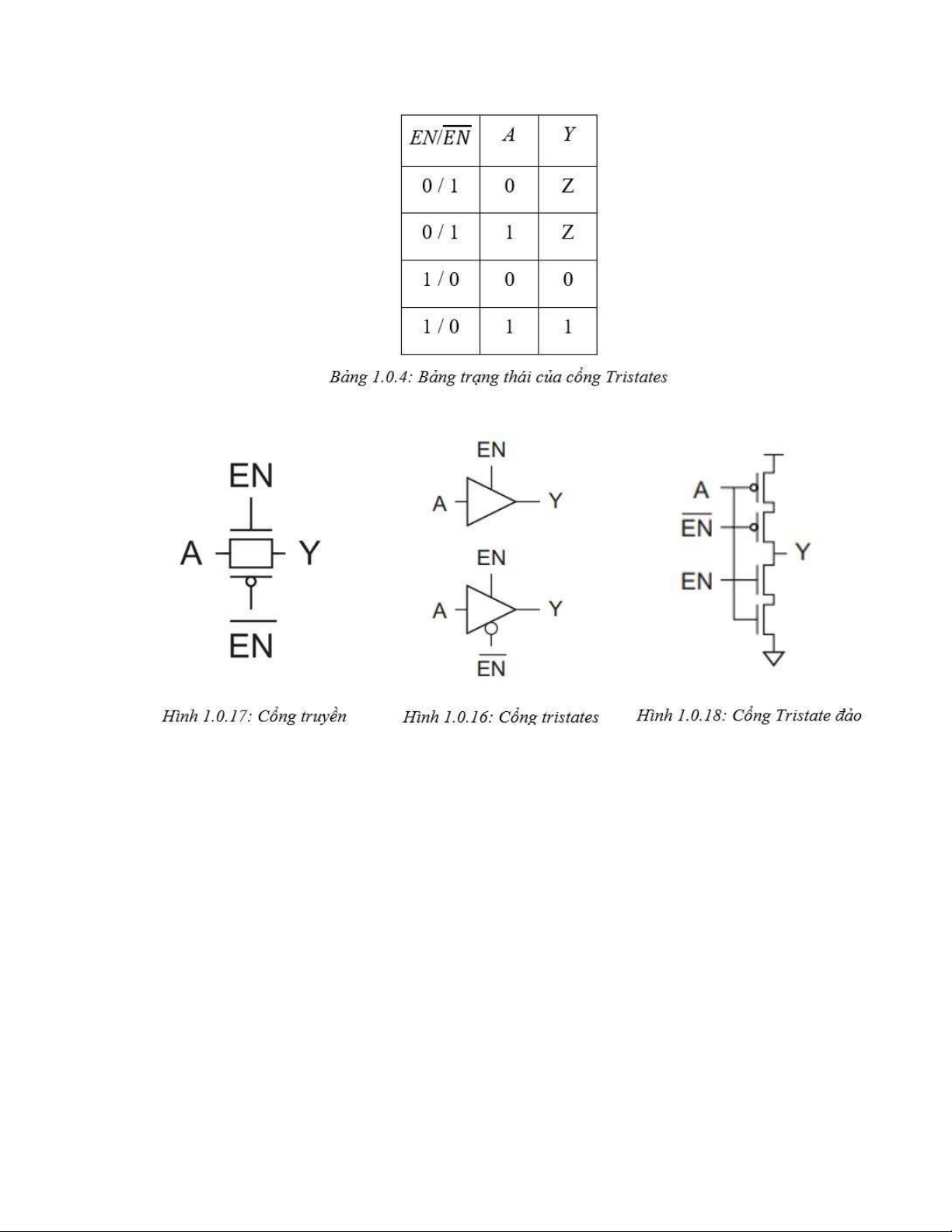

Thiết kế các mạch tristate, D-mux, D-latch, D flip-flop với dạng sóng Q, Q ảo theo CLK và D (data)

Nêu lý thuyết về ộng bộ hóa Chương 3:

Trễ (Delay) trong thiết kế VLSI ược ịnh nghĩa là khoảng thời gian cần thiết ể

tín hiệu lan truyền từ ầu vào ến ầu ra của một mạch logic hoặc một thành phần trong mạch tích hợp

Mô hình trễ rc: -mô hình trễ RC (RC Delay Model) là một phương pháp ược

sử dụng ể phân tích và ước tính thời gian trễ của tín hiệu khi truyền qua các ường

liên kết hoặc qua các phần tử trong mạch.

-Mô hình này dựa trên cá tham số iện trở và ddienj dung của mạch.

Công thức : tRC R C ( 𝑅: Điện trở của ường truyền (Ohm).

C: Điện dung ký sinh tại ầu ra (Fara))

Mô hình trễ tuyến tính là một phương pháp ơn giản nhưng hiệu quả ể ước

tính thời gian trễ của tín hiệu trong các mạch logic và liên kết , nó giả ịnh rằng trễ

có mối quan hệ tuyến tính với 1 số yếu tố chính như iện dung tải , iện trở và dòng

iều khiển .Hỗ trợ trong việc ảm bảo tín hiệu ến ồng bộ thời gian trong hệ thống

lớn, nơi thời gian trễ không ồng nhất có thể gây ra lỗi iều này giúp ồng bộ hóa tín hiệu.

Công thức: tp k R C L R: Điện trở tương ương của

transistor hoặc ường liên kết.

CL: Điện dung tải tổng tại ầu ra.

k: Hệ số tỷ lệ phụ thuộc vào ặc tính thiết kế, công nghệ, và bố trí mạch.

Ưu iểm chính của mô hình này là sự ơn giản, giúp các kỹ sư nhanh chóng

phân tích và dự oán trễ tín hiệu mà không cần mô phỏng phức tạp

Hạn chế : ộ chính xác của mô hình bị ảnh hưởng trong các thiết kế công

nghệ tiên tiến , mô hình không tính ến sự thay ổi ộng của các thông số iện Trễ

trong mạng kết nối cổng logic, các nhánh: Biểu thức tính trễ trong một ơn vị ộc lập tiến trình là: d dabs , 3RC

60 ps với tiến trình 600nm và 3ps với 65nm D=f+p

F: trễ nỗ lực(effort delay) f=g.h( g: logical effort, h:tỷ số của iện dung ầu ra/ ầu vào )

P : trễ kí sinh(parasitic delay)

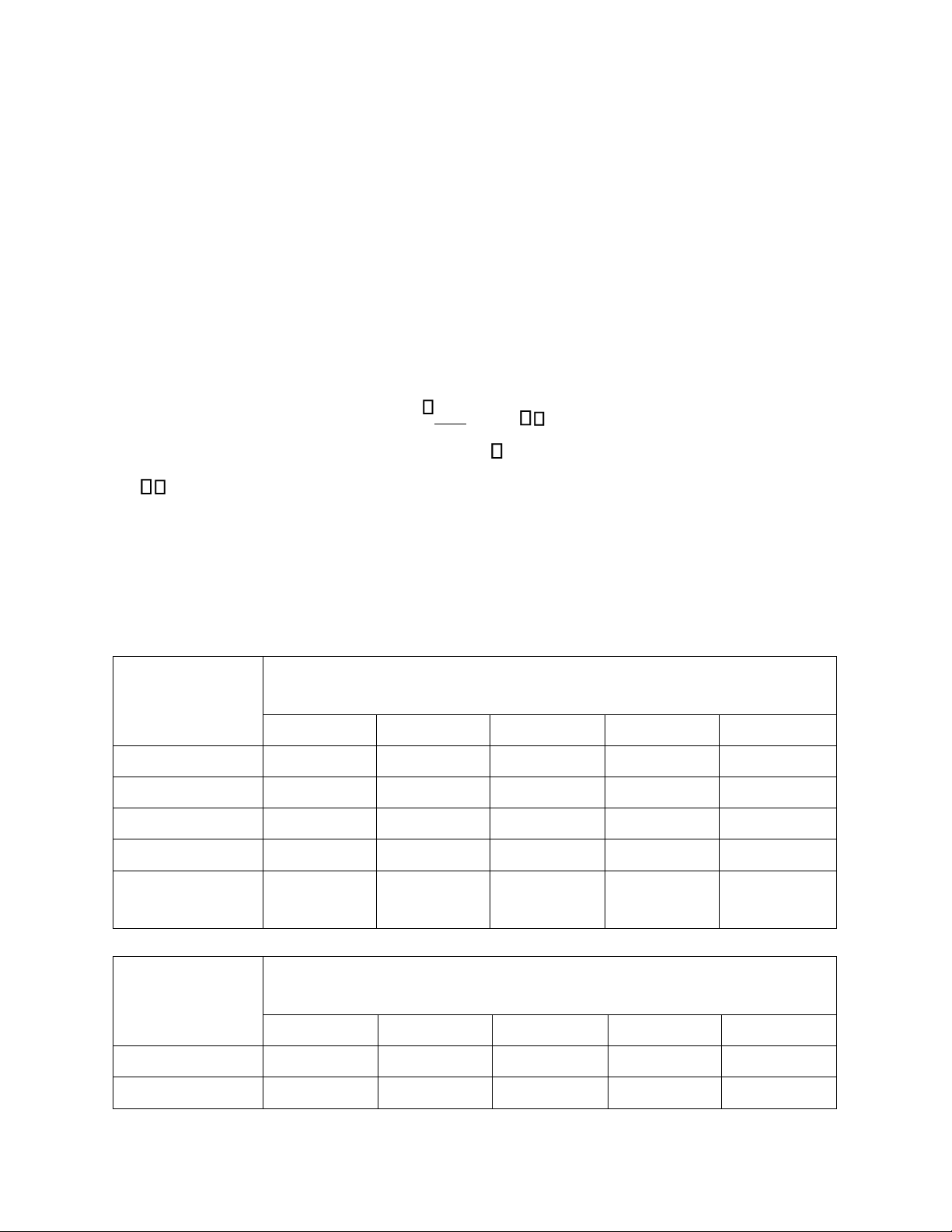

Bảng 3.1. Nỗ lực logic (g) của các cổng chung Kiểu cổng Số ầu vào 1 2 3 4 n Inverter 1 NAND 4/3 5/3 6/3 (n+2)/3 NOR 5/3 7/3 9/3 (2n+1)/3 Tristate/Mux 2 2 2 2 2 XOR, 4,4 6,12 8,16 2n, 4n XNOR

Bảng 3.2. Trễ ký sinh của các cổng chung Kiểu cổng Số ầu vào 1 2 3 4 n Inverter 1 NAND 2 3 4 n NOR 2 3 4 n Tristate/Mux 2 4 6 8 2n XOR, 4 6 8 2n XNOR

một tuyến của mạng nhiều chặng (N chặng): G iN 1gi F

iN 1 fi iN 1g hii : C out path H Cin path C b C on path off path F BGH . . Con path B iN 1bi , 1

Trễ nhỏ nhất khi mỗi chặng chịu 1 nỗi lực như nhàu : f g hi i F N 1

trễ tối thiểu của tuyến có N chặng là: Dmin N F. N P Các họ mạch CMOS tĩnh:

• Các họ mạch CMOS tĩnh với mạng nMOS kéo mức thấp và pMOS kéo mức cao

ược sử dụng cho phần lớn các cổng logic trong mạch tích hợp,, chúng có biên ộ

nhiễu tốt , nhanh , công suất thấp , ko nhạy cảm với cá biến thẻ của thiết bị , dễ

thiết kế , và ược các công cụ hỗ trợ rộng rãi.

• Sử dụng các hàm NOR VÀ NAND

• Sử dụng bubble pushing ể thiết kế mạch thử công

• Sử dụng cổng kết hợp ặc biệt và tối ưu hóa ầu vào

• Xây dựng các cổng có ộ trễ lên xuống bằng nhau và sử dụng pmos nhỏ hơn

• Nếu có nhiều iện áp ngưỡn , thì cổng có sự cần bằng tốc ộ , công suất rò rỉ khác nhau .

Đẩy bọt : +Các giai oạn CMOS vốn có tính ảo ngược, vì vậy các hàm AND

và OR phải ược xây dựng từ các cổng NAND và NOR Luật của DeMorgan giúp

thực hiện chuyển ổi này: 𝐴. 𝐵 = 𝐴 + 𝐵 𝐴 + 𝐵 = 𝐴. 𝐵

Hiệu ứng trễ ầu vào : trong thiết kế mạch số là hiện tượng mà ộ trễ truyền

qua một cổng logic (hoặc một thành phần mạch) bị ảnh hưởng bởi thứ tự kích hoạt

của các tín hiệu ầu vào. Điều này thường xảy ra trong các cổng logic kết hợp (như

NAND, NOR, XOR), khi thời gian truyền tín hiệu không chỉ phụ thuộc vào cấu

trúc cổng mà còn vào thứ tự và thời iểm tín hiệu ầu vào thay ổi.

Quy tắc non-overlapping (không chồng chéo) là một nguyên tắc thiết kế

quan trọng trong mạch số và hệ thống ồng bộ. Nguyên tắc này ảm bảo rằng hai

hoặc nhiều tín hiệu không ược kích hoạt (hoặc có giá trị "cao") cùng lúc, nhằm

tránh các vấn ề như nhiễu tín hiệu, ua tín hiệu (race condition), hoặc trạng thái

không xác ịnh. Sử dụng trong thiết kê mạch xung 2 pha , flip-flop hoặc latch,dynamic logic .

Hiện tượng skewed trong mạch:

Khi một ầu vào quan trọng hơn các ầu vào khác, cổng CMOS ối xứng có thể

ược thiết kế bất ối xứng ể giảm ộ trễ cho ầu vào quan trọng:

• Mạng nối tiếp: Đầu vào quan trọng ược kết nối với transistor bên ngoài và

transistor này ược làm rộng hơn, giảm iện trở nối tiếp.

• Mạng song song : ầu vào sớm ược kết nối với 1 transistor hẹp hơn ể giảm iện dung ký sinh

Đặc tính dòng iện và kích thước transistor:

• Trong CMOS, dòng iện qua các transistor nối tiếp lớn hơn so với dự oán từ mô

hình kênh dài do hiệu ứng bão hòa vận tốc.Dòng iện có thể dự oán bằng cách thu

gọn ngăn xếp nối tiếp thành 1 transistor tương ương.

• Với cổng không ối xứng, chiều rộng transistor tương ương ược xác ịnh bởi

transistor bên trong (hẹp hơn), trong khi chiều dài tương ương tăng theo tổng

nghịch ảo của chiều rộng tương ối.

Mạch tổ hợp ộng :

Mạch ộng là họ mạch ược sử dụng phổ biến nhanh nhất vì chúng có iện dung

ầu vào thấp hơn và không có tranh chấp trong quá trình chuyển trạng thái. Chúng

cũng có khả năng tiêu tán công suất tĩnh bằng không. Tuy nhiên, chúng yêu cầu

xung nhịp cẩn thận, tiêu thụ năng lượng ộng áng kể và nhạy cảm với nhiễu trong quá trình evaluate. Chương 4:

Nêu về trình tự mạch tĩnh :

1. Phương pháp tuần tự với flip-flops: •

Sử dụng flip-flop ể phân chia chu kỳ ồng hồ, trong ó mỗi flip-flop giữ dữ liệu ở

ầu ra ến chu kỳ tiếp theo. •

Dữ liệu ược ghi lại trên cạnh ồng hồ tăng hoặc giảm (thường là cạnh tăng). •

Nếu dữ liệu ến quá sớm, nó phải chờ tại flip-flop ến chu kỳ tiếp theo. •

Ràng buộc ộ trễ tối a:

Chu kỳ ồng hồ phải ủ lớn ể dữ liệu từ flip-flop trước ến flip-flop sau thông qua logic tổ hợp: Tc ≥ tpcq + tpd + tsetup

2. Phương pháp tuần tự với chốt hai pha: •

Chốt hai pha sử dụng hai tín hiệu ồng hồ không trùng lặp (ϕ1 và ϕ2). •

Dữ liệu ược truyền qua các chốt và logic tổ hợp trong mỗi pha. •

Độ trễ logic tổ hợp ược chia thành hai giai oạn, tăng hiệu quả tính toán so với flip-flops. •

Ràng buộc ộ trễ tối a: tpd1 + tpd2 ≤ Tc – 2tpdq

3. Phương pháp tuần tự với chốt xung: •

Chốt xung sử dụng một xung ồng hồ ngắn ể truyền dữ liệu. •

Xung ồng hồ phải rộng hơn thời gian thiết lập, nhưng ngắn hơn ộ trễ logic.

Ràng buộc ộ trễ tối a: tpd ≤ Tc – max(tpdq, tpcq + tsetup – t_

Rang buộc về ộ trễ tối a: toàn bộ chu kỳ clock sẽ có sẵn ể tính toán theo logic

tổ hợp.. Nếu ộ trễ logic tổ hợp quá lớn, phần tử nhận sẽ bỏ lỡ thời gian thiết lập và

lấy mẫu sai giá trị. Đây ược gọi là lỗi thời gian thiết lập hoặc lỗi thời gian trễ tối a •

Với flip-flop: Tc ≥ tpcq + tpd + tsetup •

Với chốt 2 pha: Tc ≥ tpdq1 + tpd1 + tpd2và tpd = tpd1 + tpd2 ≤ (Tc – 2tpdq) •

với chốt xung : Tc ≥ max(tpdq + tpd, tpcq + tpd + tsetup – 𝑡𝑝𝜔) và tpd ≤ Tc – max(tpdq, tpcq +

tsetup – 𝑡𝑝𝜔)

rang buộc về thời gian tối thiểu : các phần tử trình tự có thể ược ặt liền nhau

mà không can thiệp vào logic tổ hợp và vẫn hoạt ộng chính xác. , nếu thời gian lưu

giữ lớn và ộ trễ nhỏ, dữ liệu có thể chuyển ổi sai thông qua hai phần tử liên tiếp

trên một cạnh ồng hồ, làm hỏng trạng thái của hệ thống. Đây ược gọi là thời gian tối thiểu •

với flip-flop : tcd ≥ thold - tccq •

với chốt 2 pha : tcd1, tcd2 ≥ thold – tccq - tnonovarlap thời gian chờ : trong 1 flop cơ bản : •

dữ liệu khởi chạy trên một sường lên •

phải thiết lập trước khi sường lên tiếp theo •

nếu trễ , hệ thống sẽ lỗi •

nếu nó ến sớm , thời gian sẽ lãng phí flops có cạnh cứng trong mạch latch cơ bản •

dữ liệu có thể thông qua mạch latch •

chu kì logic dài có thể muownjj thời gian tiếp tục miễn là mỗi vòng lặp hoàn thành trong một chu kì chốt 2 pha : tborrow

𝑇𝑐 – (tsetup + tnonoverlap) chốt xung : tborrow ≤ 𝑡𝑝𝜔- tsetup

Lý thuyết về bộ ồng hóa: •

Chốt và trạng thái ổn ịnh: Bộ chốt là thiết bị bistable với hai trạng thái ổn ịnh (0

và 1). Khi bị nhiễu, nó có thể chuyển sang trạng thái không xác ịnh

(di căn), nhưng sẽ chuyển về một trong hai trạng thái ổn ịnh khi có tác ộng. •

Bộ ồng bộ hóa: Chấp nhận ầu vào không ồng bộ và ồng bộ hóa với ồng hồ. Nó có

khẩu ộ xác ịnh bởi thời gian thiết lập và giữ. Nếu dữ liệu thay ổi trong khẩu ộ, ầu

ra có thể không hợp lệ. •

Giao tiếp giữa các miền ồng hồ không ồng bộ: Bộ ồng bộ hóa thường dùng ể

truyền dữ liệu giữa các hệ thống không chia sẻ ồng hồ chung. Các tín hiệu yêu

cầu và xác nhận (Req và Ack) giúp ồng bộ hóa việc truyền dữ liệu giữa hai hệ thống. •

Giao thức bắt tay: Giao tiếp không ồng bộ sử dụng các giao thức bắt tay hai pha

và bốn pha. Bộ ồng bộ hóa có thể ược sử dụng ể giải quyết yêu cầu xác nhận. •

Lỗi bộ ồng bộ hóa: Các lỗi thường gặp bao gồm lỗi di căn, thu thập dữ liệu không

nhất quán và ồng bộ hóa từ nhiều bit. Để tránh lỗi, cần thiết kế chặt chẽ và kiểm

tra kỹ các giao diện không ồng bộ. •

Bộ ồng bộ hóa và hiệu suất: Bộ ồng bộ hóa có thể làm giảm thông lượng truyền

thông không ồng bộ, vì nó thêm ộ trễ vào quá trình ồng bộ hóa dữ liệu. Chương 5:

Nguyên lý thiết kế SRAM

SRAM (Static Random-Access Memory) ược sử dụng ể lưu trữ dữ liệu tạm

thời trong các thiết bị iện tử. Trong thiết kế SRAM, các tế bào nhớ (memory cell)

ược cấu tạo từ các transistor và hoạt ộng dựa trên các nguyên lý cơ bản sau:

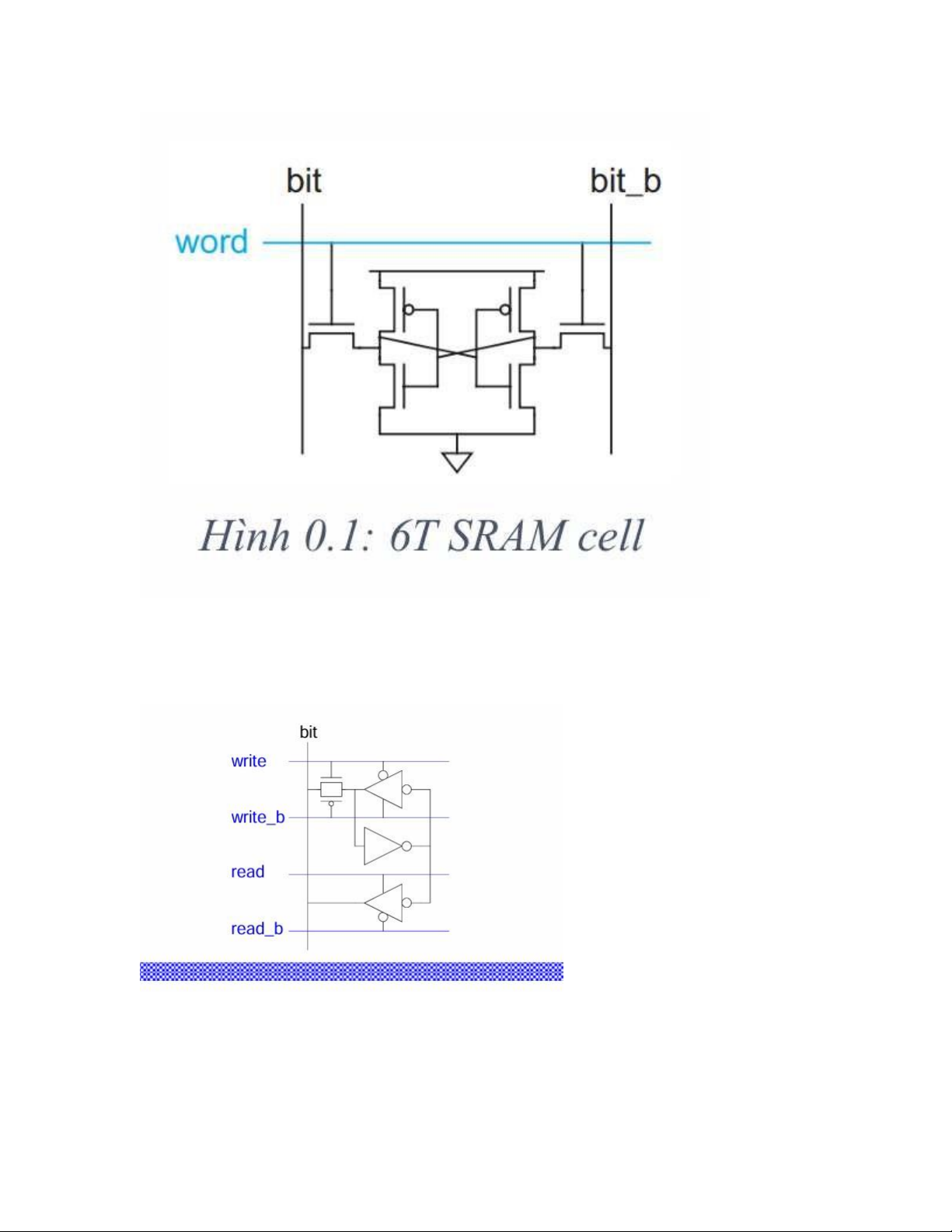

1. SRAM kiểu 6T (6 Transistor): Sơ ồ mạch: •

Hai transistor pull-up và pull-down tạo thành một flip-flop ể lưu trữ một bit dữ liệu. •

Hai transistor pass-gate kết nối flip-flop với các ường bit line (BL) và bit line bổ sung (BL̅ ). •

2. SRAM kiểu 12T (12 Transistor):

Kiến trúc cơ bản: •

SRAM 12T bổ sung thêm transistor ể cải thiện ộ ổn ịnh và khả năng chống nhiễu.