Preview text:

Bộ nhớ cache

Mặc dù về mặt khái niệm có vẻ đơn giản, bộ nhớ máy tính có lẽ thể hiện phạm

vi rộng nhất về loại, công nghệ, tổ chức, hiệu suất và giá thành của bất kỳ tính

năng nào của hệ thống máy tính. Không có công nghệ đơn lẻ nào là tối ưu trong

việc đáp ứng các yêu cầu về bộ nhớ cho một hệ thống máy tính. Kết quả là, hệ

thống máy tính điển hình được trang bị một hệ thống phân cấp bộ nhớ con, một

số bên trong hệ thống (bộ xử lý có thể truy cập trực tiếp) và một số bên ngoài (bộ

xử lý có thể truy cập thông qua mô-đun I/O). Chúng ta xem xét một yếu tố thiết

yếu của tất cả các hệ thống máy tính hiện đại: bộ nhớ cache.

1. TỔNG QUAN VỀ HỆ THỐNG BỘ NHỚ MÁY TÍNH

Đặc điểm của hệ thống bộ nhớ

Chủ đề phức tạp của bộ nhớ máy tính sẽ trở nên dễ quản lý hơn nếu

chúng ta phân loại các hệ thống bộ nhớ theo các đặc điểm chính của chúng.

Điều quan trọng nhất trong số này được liệt kê trong Bảng 4.1.

Thuật ngữ vị trí trong Bảng 4.1 đề cập đến việc bộ nhớ ở bên trong hay bên

ngoài máy tính. Bộ nhớ trong thường được đánh đồng với bộ nhớ chính, nhưng có

những dạng bộ nhớ trong khác. Bộ xử lý yêu cầu bộ nhớ cục bộ của riêng nó, ở dạng

thanh ghi. Hơn nữa, như chúng ta sẽ thấy, phần đơn vị điều khiển của bộ xử lý cũng

có thể yêu cầu bộ nhớ trong của chính nó. Chúng ta sẽ hoãn thảo luận về hai loại bộ

nhớ trong này ở các chương sau. Bộ nhớ đệm là một dạng khác của bộ nhớ trong. Bộ

nhớ ngoài bao gồm các thiết bị lưu trữ ngoại vi, chẳng hạn như đĩa và băng, mà bộ xử

lý có thể truy cập thông qua bộ điều khiển I/O.

Một đặc điểm rõ ràng của bộ nhớ là dung lượng của nó. Đối với bộ nhớ

trong, điều này thường được thể hiện dưới dạng byte (1 byte = 8 bit) hoặc từ.

Độ dài từ phổ biến là 8, 16 và 32 bit. Dung lượng bộ nhớ ngoài thường được biểu thị bằng byte.

Bảng 4.1 Các đặc điểm chính của hệ thống bộ nhớ máy tính

Một khái niệm liên quan là đơn vị chuyển giao. Đối với bộ nhớ trong, đơn vị

truyền bằng số lượng đường dây điện vào và ra khỏi mô-đun bộ nhớ. Điều này

có thể bằng độ dài từ, nhưng thường lớn hơn, chẳng hạn như 64, 128 hoặc 256

bit. Để làm rõ điểm này, hãy xem xét ba khái niệm liên quan cho bộ nhớ trong:

Từ ngữ: Đơn vị "tự nhiên" của tổ chức bộ nhớ. Kích thước của một từ

thường bằng số bit được sử dụng để biểu diễn một số nguyên và độ dài

lệnh. Thật không may, có nhiều trường hợp ngoại lệ. Ví dụ: CRAY C90

(một siêu máy tính CRAY kiểu cũ hơn) có độ dài từ 64 bit nhưng sử dụng

biểu diễn số nguyên 46 bit. Kiến trúc Intel x86 có nhiều độ dài lệnh khác

nhau, được biểu thị dưới dạng bội số byte và kích thước từ là 32 bit.

Đơn vị địa chỉ: Trong một số hệ thống, đơn vị địa chỉ là từ. Tuy nhiên,

nhiều hệ thống cho phép giải quyết ở cấp độ byte. Trong mọi trường

hợp, mối quan hệ giữa độ dài tính bằng bit A của một địa chỉ và số N

của các đơn vị địa chỉ là 2A = N.

Đơn vị chuyển nhượng: Đối với bộ nhớ chính, đây là số bit được đọc

ra hoặc ghi vào bộ nhớ tại một thời điểm. Đơn vị chuyển nhượng

không cần phải bằng một từ hoặc một đơn vị địa chỉ. Đối với bộ nhớ

ngoài, dữ liệu thường được truyền theo đơn vị lớn hơn nhiều so với

một từ và chúng được gọi là khối.

Một điểm khác biệt giữa các loại bộ nhớ là phương pháp truy cập các đơn vị

dữ liệu. Chúng bao gồm những điều sau đây:

Truy cập tuần tự: Bộ nhớ được tổ chức thành các đơn vị dữ liệu, được

gọi là bản ghi. Truy cập phải được thực hiện theo một trình tự tuyến tính

cụ thể. Thông tin địa chỉ được lưu trữ được sử dụng để tách các bản ghi và

hỗ trợ trong quá trình truy xuất. Một cơ chế đọc-ghi được chia sẻ được sử

dụng và cơ chế này phải được di chuyển từ vị trí hiện tại của nó đến vị trí

mong muốn, vượt qua và từ chối từng bản ghi trung gian. Do đó, thời gian

để truy cập một bản ghi tùy ý rất khác nhau.

Truy cập trực tiếp: Cũng như truy cập tuần tự, truy cập trực tiếp

liên quan đến cơ chế đọc-ghi được chia sẻ. Tuy nhiên, các khối hoặc

bản ghi riêng lẻ có một địa chỉ duy nhất dựa trên vị trí thực tế. Truy

cập được thực hiện bằng cách truy cập trực tiếp để đến vùng lân cận

chung cộng với tìm kiếm, đếm hoặc chờ đợi tuần tự để đến vị trí

cuối cùng. Một lần nữa, thời gian truy cập có thể thay đổi.

Truy cập ngẫu nhiên: Mỗi vị trí địa chỉ trong bộ nhớ có một cơ chế

định địa chỉ duy nhất, có dây vật lý. Thời gian để truy cập một vị trí

nhất định độc lập với chuỗi truy cập trước đó và không đổi. Do đó,

bất kỳ vị trí nào cũng có thể được chọn ngẫu nhiên và được giải

quyết và truy cập trực tiếp. Bộ nhớ chính và một số hệ thống bộ nhớ

cache là truy cập ngẫu nhiên.

Liên kết: Đây là một loại bộ nhớ truy cập ngẫu nhiên cho phép

người ta so sánh các vị trí bit mong muốn trong một từ cho một kết

quả phù hợp cụ thể và thực hiện việc này cho tất cả các từ đồng thời.

Do đó, một từ được truy xuất dựa trên một phần nội dung của nó chứ

không phải địa chỉ của nó. Như với bộ nhớ truy cập ngẫu nhiên

thông thường, mỗi vị trí có cơ chế định địa chỉ riêng và thời gian

truy xuất không đổi độc lập với vị trí hoặc các mẫu truy cập trước

đó. Bộ nhớ cache có thể sử dụng quyền truy cập kết hợp.

Từ quan điểm của người dùng, hai đặc điểm quan trọng nhất của bộ nhớ là

dung lượng và hiệu suất. Ba thông số hiệu suất được sử dụng:

Thời gian truy cập (độ trễ): Đối với bộ nhớ truy cập ngẫu nhiên,

đây là thời gian cần thiết để thực hiện thao tác đọc hoặc ghi, nghĩa là

thời gian từ thời điểm một địa chỉ được hiển thị vào bộ nhớ đến tức

thì dữ liệu đó đã được lưu trữ hoặc cung cấp để sử dụng. Đối với bộ

nhớ truy cập không ngẫu nhiên, thời gian truy cập là thời gian cần

thiết để định vị cơ chế đọc-ghi tại vị trí mong muốn.

Thời gian chu kỳ bộ nhớ: Khái niệm này chủ yếu được áp dụng cho bộ

nhớ truy cập ngẫu nhiên và bao gồm thời gian truy cập cộng với bất kỳ

thời gian bổ sung nào cần thiết trước khi truy cập thứ hai có thể bắt đầu.

Thời gian bổ sung này có thể được yêu cầu để quá độ chết

trên các đường tín hiệu hoặc tái tạo dữ liệu nếu chúng được đọc

một cách phá hủy. Lưu ý rằng thời gian chu kỳ bộ nhớ liên quan

đến bus hệ thống, không phải bộ xử lý.

Tốc độ truyền: Đây là tốc độ mà dữ liệu có thể được truyền vào

hoặc ra khỏi một đơn vị bộ nhớ. Đối với bộ nhớ truy cập ngẫu

nhiên, nó bằng 1 / (thời gian chu kỳ). Đối với bộ nhớ truy cập

không ngẫu nhiên, mối quan hệ sau đây giữ: Trong đó:

Tn = Thời gian trung bình để đọc hoặc ghi n

bit TA = Thời gian truy cập trung bình n = Số bit

R = Tốc độ truyền, tính bằng bit trên giây (bps)

Một loạt các loại bộ nhớ vật lý đã được sử dụng. Phổ biến nhất hiện nay là

bộ nhớ bán dẫn, bộ nhớ bề mặt từ, được sử dụng cho đĩa và băng, và quang học và quang học.

Một số đặc điểm vật lý của lưu trữ dữ liệu là quan trọng. Trong một bộ nhớ dễ

bay hơi, thông tin phân rã tự nhiên hoặc bị mất khi tắt nguồn điện. Trong một bộ

nhớ không bay hơi, thông tin một khi được ghi lại vẫn không bị suy giảm cho đến

khi cố tình thay đổi; không cần nguồn điện để lưu giữ thông tin. Ký ức bề mặt từ

tính là không bay hơi. Bộ nhớ bán dẫn (bộ nhớ trên các mạch tích hợp) có thể dễ bay

hơi hoặc không bay hơi. Bộ nhớ không thể thay đổi, ngoại trừ bằng cách phá hủy

đơn vị lưu trữ. Bộ nhớ bán dẫn loại này được gọi là bộ nhớ chỉ đọc (ROM). Điều

cần thiết, một bộ nhớ không thể thay đổi thực tế cũng phải không bay hơi.

Đối với bộ nhớ truy cập ngẫu nhiên, tổ chức là một vấn đề thiết kế quan

trọng. Trong bối cảnh này, tổ chức đề cập đến sự sắp xếp vật lý của các bit để tạo thành các từ.

Hệ thống phân cấp bộ nhớ:

Các ràng buộc thiết kế trên bộ nhớ của máy tính có thể được tóm tắt bằng ba

câu hỏi: Bao nhiêu? Nhanh như thế nào? Đắt như thế nào?

Câu hỏi bao nhiêu là phần nào mở đã kết thúc. Nếu dung lượng ở đó, các ứng

dụng có thể sẽ được phát triển để sử dụng nó. Câu hỏi về tốc độ nhanh như thế nào,

theo một nghĩa nào đó, dễ trả lời hơn. Để đạt được hiệu suất cao nhất, bộ nhớ phải có

khả năng theo kịp bộ xử lý. Có nghĩa là, khi bộ xử lý đang thực thi các lệnh, chúng tôi

sẽ không muốn nó phải tạm dừng chờ lệnh hoặc toán hạng. Câu hỏi cuối

cùng cũng phải được xem xét. Đối với một hệ thống thực tế, chi phí của bộ

nhớ phải hợp lý trong mối quan hệ với các thành phần khác.

Đúng như dự đoán, có một sự đánh đổi giữa ba đặc điểm chính của bộ nhớ:

dung lượng, thời gian truy cập và chi phí. Một loạt các công nghệ được sử dụng

để triển khai các hệ thống bộ nhớ và trên phạm vi công nghệ này, các mối quan hệ sau đây được giữ:

Thời gian truy cập nhanh hơn, chi phí cho mỗi bit lớn

hơn; Dung lượng lớn hơn, chi phí mỗi bit nhỏ hơn;

Dung lượng lớn hơn, thời gian truy cập chậm hơn.

Vấn đề nan giải mà nhà thiết kế phải đối mặt là rõ ràng. Nhà thiết kế muốn

sử dụng các công nghệ bộ nhớ cung cấp bộ nhớ dung lượng lớn, cả vì dung

lượng là cần thiết và vì chi phí cho mỗi bit thấp. Tuy nhiên, để đáp ứng yêu cầu

về hiệu suất, nhà thiết kế cần sử dụng bộ nhớ đắt tiền, dung lượng tương đối thấp

hơn với thời gian truy cập ngắn.

Cách thoát khỏi tình huống khó xử này không phải là dựa vào một thành

phần hoặc công nghệ bộ nhớ duy nhất, mà là sử dụng hệ thống phân cấp bộ nhớ.

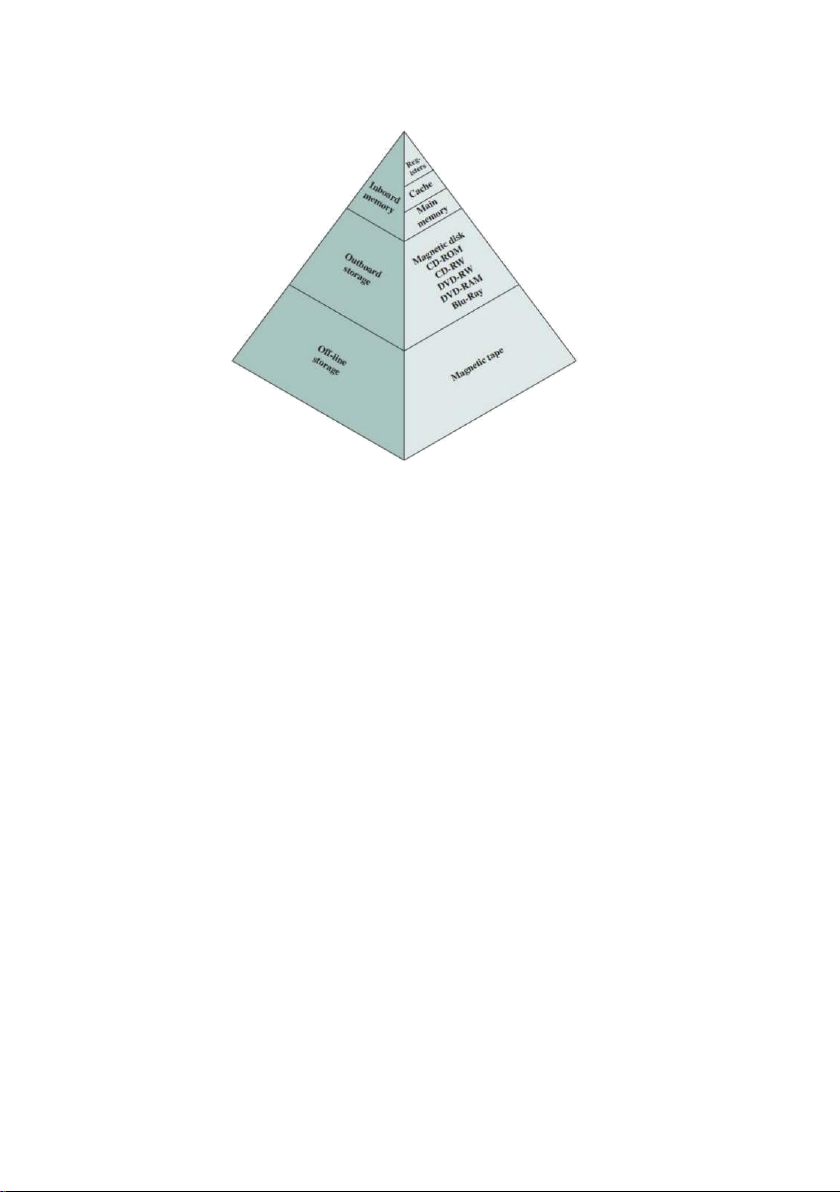

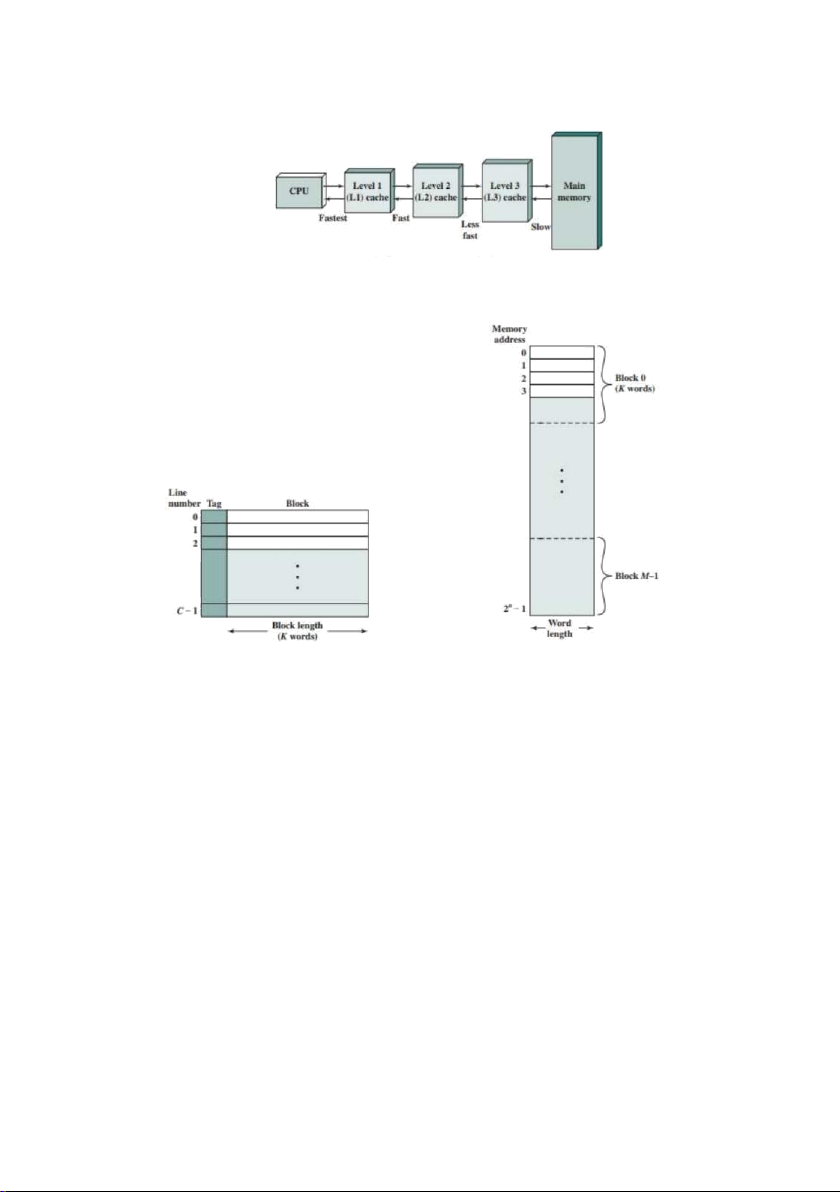

Một hệ thống phân cấp điển hình được minh họa trong Hình 4.1. Khi một người

đi xuống hệ thống phân cấp, điều sau đây xảy ra: a. Giảm chi phí mỗi bit; b. Tăng công suất;

c. Tăng thời gian truy cập;

d. Giảm tần suất truy cập bộ nhớ của bộ xử lý.

Do đó, bộ nhớ nhỏ hơn, đắt hơn, nhanh hơn được bổ sung bởi những ký ức

lớn hơn, rẻ hơn, chậm hơn. Chìa khóa thành công của mục tổ chức này (d):

giảm tần suất truy cập.

Hình 4.1 Hệ thống phân cấp bộ nhớ

Cơ sở cho tính hợp lệ của điều kiện (d) là một nguyên tắc được gọi là địa phương

tham chiếu [DENN68]. Trong quá trình thực thi chương trình, các tham chiếu bộ nhớ

của bộ xử lý, cho cả lệnh và dữ liệu, có xu hướng cụm. Các chương trình thường

chứa một số vòng lặp lặp và chương trình con. Khi một vòng lặp hoặc chương trình

con được nhập, có các tham chiếu lặp đi lặp lại đến một tập hợp nhỏ các hướng dẫn.

Tương tự, các hoạt động trên bảng và mảng liên quan đến quyền truy cập vào một tập

hợp các từ dữ liệu được nhóm lại. Trong một khoảng thời gian dài, các cụm được sử

dụng thay đổi, nhưng trong một khoảng thời gian ngắn, bộ xử lý chủ yếu hoạt động

với các cụm tham chiếu bộ nhớ cố định.

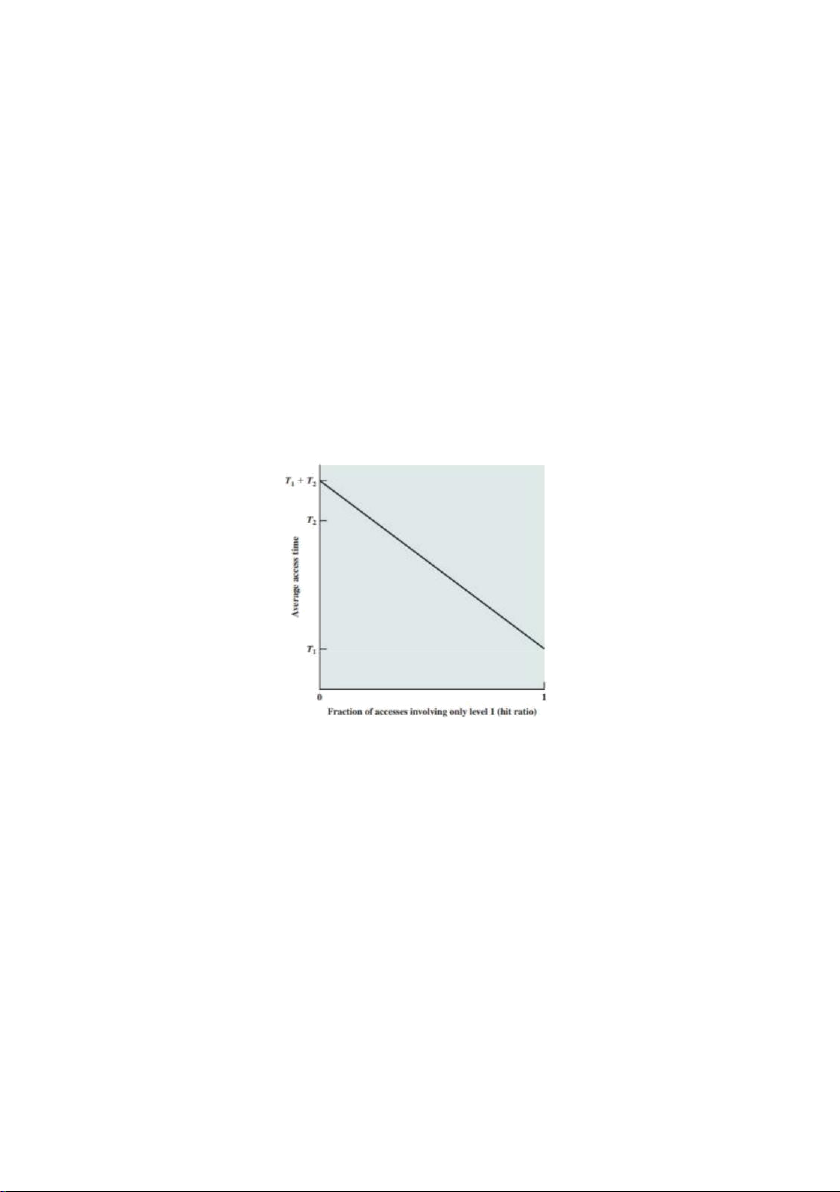

VÍ DỤ 4.1 Giả sử rằng bộ xử lý có quyền truy cập vào hai cấp độ bộ nhớ. Cấp

độ 1 chứa 1000 từ và có thời gian truy cập là 0.01 ms; Cấp độ 2 chứa 100,000 từ và có

thời gian truy cập là 0.1 ms. Giả sử rằng nếu một từ cần truy cập ở cấp độ 1, thì bộ xử

lý sẽ truy cập trực tiếp vào từ đó. Nếu nó ở cấp độ 2, thì từ đầu tiên được chuyển đến

cấp độ 1 và sau đó được bộ xử lý truy cập. Để đơn giản, chúng tôi bỏ qua thời gian

cần thiết để bộ xử lý xác định xem từ đó ở cấp độ 1 hay cấp độ 2. Hình 4.2 cho thấy

hình dạng chung của đường cong bao gồm tình huống này. Hình vẽ cho thấy thời gian

truy cập trung bình vào bộ nhớ hai cấp như một hàm của tỷ lệ truy cập H, trong đó H

được định nghĩa là phần nhỏ của tất cả các truy cập bộ nhớ được tìm thấy trong bộ

nhớ nhanh hơn (ví dụ: bộ nhớ cache), T1 là thời gian truy cập đến cấp độ 1 và T2 là

thời gian truy cập đến cấp độ 2. Có thể thấy, đối với tỷ lệ

truy cập cấp độ 1 cao, tổng thời gian truy cập trung bình gần với thời gian của

cấp độ 1 hơn nhiều so với cấp độ 2.

Trong ví dụ của chúng tôi, giả sử 95% quyền truy cập bộ nhớ được tìm thấy

ở cấp độ 1. Sau đó, thời gian trung bình để truy cập một từ có thể được thể hiện dưới dạng:

(0.95)(0.01 ms) + (0.05)(0.01 ms + 0.1 ms) = 0.0095 + 0.0055 = 0.015 ms

Thời gian truy cập trung bình gần 0.01 ms hơn nhiều so với 0.1 ms, như mong muốn.

Theo đó, có thể tổ chức dữ liệu trên hệ thống phân cấp sao cho tỷ lệ truy

cập vào mỗi cấp thấp hơn liên tiếp ít hơn đáng kể so với cấp trên. Hãy xem xét

ví dụ hai cấp độ đã được trình bày. Hãy để bộ nhớ cấp 2 chứa tất cả các hướng

dẫn và dữ liệu của chương trình. Các cụm hiện tại có thể được đặt tạm thời ở cấp

độ 1. Thỉnh thoảng, một trong những cụm ở cấp độ 1 sẽ được hoán đổi trở lại

cấp độ 2 để nhường chỗ cho một cụm mới sắp lên cấp 1. Tuy nhiên, trung bình,

hầu hết các tài liệu tham khảo sẽ là các hướng dẫn và dữ liệu có trong cấp độ 1.

Hình 4.2 Hiệu suất truy cập chỉ liên quan đến cấp độ 1 (tỷ lệ truy cập)

Nguyên tắc này có thể được áp dụng trên nhiều hơn hai cấp độ bộ nhớ, như được

đề xuất bởi hệ thống phân cấp được hiển thị trong Hình 4.1. Loại bộ nhớ nhanh nhất,

nhỏ nhất và đắt nhất bao gồm các thanh ghi bên trong bộ xử lý. Thông thường, một

bộ xử lý sẽ chứa vài chục thanh ghi như vậy, mặc dù một số máy chứa hàng trăm

thanh ghi. Bộ nhớ chính là hệ thống bộ nhớ trong chính của máy tính. Mỗi vị trí trong

bộ nhớ chính có một địa chỉ duy nhất. Bộ nhớ chính thường được mở rộng với bộ nhớ

đệm nhỏ hơn, tốc độ cao hơn. Bộ nhớ cache thường không hiển thị cho lập trình viên

hoặc, thực sự, với bộ xử lý. Nó là một thiết bị để dàn

dựng sự chuyển động của dữ liệu giữa bộ nhớ chính và các thanh ghi bộ xử lý

để cải thiện hiệu suất.

Ba dạng bộ nhớ vừa được mô tả, thông thường, dễ bay hơi và sử dụng công

nghệ bán dẫn. Việc sử dụng ba cấp độ khai thác thực tế là bộ nhớ bán dẫn có

nhiều loại khác nhau, khác nhau về tốc độ và chi phí. Dữ liệu được lưu trữ vĩnh

viễn hơn trên các thiết bị lưu trữ khối lượng bên ngoài, trong đó phổ biến nhất là

đĩa cứng và phương tiện lưu động, chẳng hạn như đĩa từ di động, băng từ và lưu

trữ quang. Bộ nhớ ngoài, không bay hơi còn được gọi là bộ nhớ phụ hoặc bộ nhớ

phụ. Chúng được sử dụng để lưu trữ các tệp chương trình và dữ liệu và thường

chỉ hiển thị cho lập trình viên về các tệp và bản ghi, trái ngược với các byte hoặc

từ riêng lẻ. Đĩa cũng được sử dụng để cung cấp một phần mở rộng cho bộ nhớ

chính được gọi là bộ nhớ ảo.

Các dạng bộ nhớ khác có thể được bao gồm trong hệ thống phân cấp. Ví

dụ, các máy tính lớn của IBM bao gồm một dạng bộ nhớ trong được gọi là bộ

nhớ mở rộng. Điều này sử dụng công nghệ bán dẫn chậm hơn và ít tốn kém hơn

so với bộ nhớ chính. Nói đúng ra, bộ nhớ này không phù hợp với hệ thống phân

cấp mà là một nhánh bên: Dữ liệu có thể được di chuyển giữa bộ nhớ chính và bộ

nhớ mở rộng nhưng không phải giữa bộ nhớ mở rộng và bộ nhớ ngoài. Các dạng

bộ nhớ thứ cấp khác bao gồm đĩa quang và đĩa quang magneto. Cuối cùng, các

cấp độ bổ sung có thể được thêm vào hệ thống phân cấp trong phần mềm một

cách hiệu quả. Một phần của bộ nhớ chính có thể được sử dụng làm bộ đệm để

lưu giữ dữ liệu tạm thời sẽ được đọc ra đĩa. Một kỹ thuật như vậy, đôi khi được

gọi là bộ đệm đĩa cải thiện hiệu suất theo hai cách:

Ghi đĩa được nhóm lại. Thay vì nhiều lần truyền dữ liệu nhỏ,

chúng tôi có một vài lần truyền dữ liệu lớn. Điều này cải thiện

hiệu suất đĩa và giảm thiểu sự tham gia của bộ xử lý.

Một số dữ liệu dành cho ghi ra có thể được tham chiếu bởi một

chương trình trước khi kết xuất tiếp theo vào đĩa. Trong trường

hợp đó, dữ liệu được truy xuất nhanh chóng từ bộ đệm phần mềm thay vì từ đĩa.

2. NGUYÊN TẮC BỘ NHỚ CACHE

Bộ nhớ cache được thiết kế để kết hợp thời gian truy cập bộ nhớ của bộ nhớ đắt

tiền, tốc độ cao kết hợp với kích thước bộ nhớ lớn của bộ nhớ tốc độ thấp hơn, ít tốn

kém hơn. Khái niệm này được minh họa trong Hình 4.3a. Có một bộ nhớ chính tương

đối lớn và chậm cùng với bộ nhớ đệm nhỏ hơn, nhanh hơn. Bộ đệm ẩn chứa một bản

sao của các phần của bộ nhớ chính. Khi bộ xử lý cố gắng đọc một từ bộ nhớ, một

kiểm tra được thực hiện để xác định xem từ đó có trong bộ đệm ẩn hay

không. Nếu vậy, từ được gửi đến bộ xử lý. Nếu không, một khối bộ nhớ chính,

bao gồm một số từ cố định, được đọc vào bộ đệm và sau đó từ được gửi đến bộ

xử lý. Do hiện tượng địa phương của tham chiếu, khi một khối dữ liệu được tìm

nạp vào bộ nhớ cache để thỏa mãn một tham chiếu bộ nhớ duy nhất, có khả

năng sẽ có các tham chiếu trong tương lai đến cùng một vị trí bộ nhớ đó hoặc các từ khác trong khối.

Hình 4.3b mô tả việc sử dụng nhiều cấp độ bộ nhớ cache. Bộ đệm L2 chậm

hơn và thường lớn hơn bộ đệm L1 và bộ đệm L3 chậm hơn và thường lớn hơn bộ đệm L2.

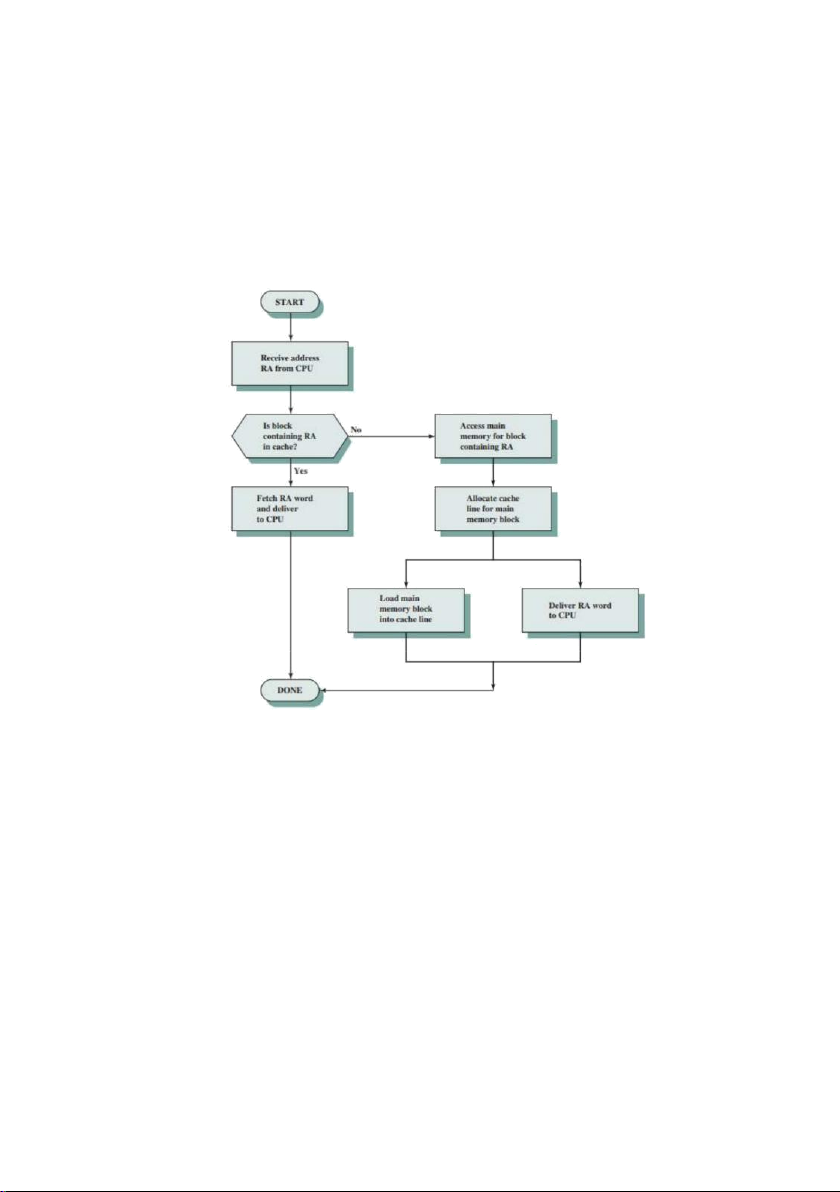

Hình 4.4 mô tả cấu trúc của hệ thống bộ nhớ cache / bộ nhớ chính. Bộ nhớ chính

bao gồm tối đa 2n từ có thể định địa chỉ, với mỗi từ có một địa chỉ n-bit duy nhất. Đối

với mục đích lập bản đồ, bộ nhớ này được coi là bao gồm một số khối từ K có độ dài

cố định. Nghĩa là, có các khối M = 2n / K trong bộ nhớ chính. Bộ nhớ cache bao gồm

các khối m, được gọi là các dòng, mỗi dòng chứa các từ K, cộng với một thẻ gồm một

vài bit. Mỗi dòng cũng bao gồm các bit điều khiển (không được hiển thị), chẳng hạn

như bit để cho biết liệu dòng đã được sửa đổi kể từ khi được tải vào bộ nhớ cache. Độ

dài của một dòng, không bao gồm thẻ và bit điều khiển, là kích thước dòng. Kích

thước dòng có thể nhỏ tới 32 bit, với mỗi "từ" là một byte duy nhất; Trong trường hợp

này, kích thước dòng là 4 byte. Số lượng dòng ít hơn đáng kể so với số lượng khối bộ

nhớ chính (m V M). Bất cứ lúc nào, một số tập hợp con của các khối bộ nhớ nằm

trong các dòng trong bộ đệm. Nếu một từ trong một khối bộ nhớ được đọc, khối đó

được chuyển đến một trong các dòng của bộ nhớ cache. Bởi vì có nhiều khối hơn

dòng, một dòng riêng lẻ không thể được dành riêng duy nhất và vĩnh viễn cho một

khối cụ thể. Do đó, mỗi dòng bao gồm một thẻ xác định khối cụ thể nào hiện đang

được lưu trữ. Thẻ thường là một phần của địa chỉ bộ nhớ chính, như được mô tả sau trong phần này.

(a) Bộ nhớ cache duy nhất

(b) Tổ chức bộ nhớ đệm ba cấp

Hình 4.3 Bộ nhớ cache và bộ nhớ chính (a) Bộ nhớ cache (b) Bộ nhớ chính

Hình 4.4 Cấu trúc bộ nhớ cache / bộ nhớ chính

Hình 4.5 minh họa hoạt động đọc. Bộ xử lý tạo địa chỉ đọc (RA) của một từ cần

đọc. Nếu từ được chứa trong bộ đệm, nó sẽ được gửi đến bộ xử lý. Mặt khác, khối

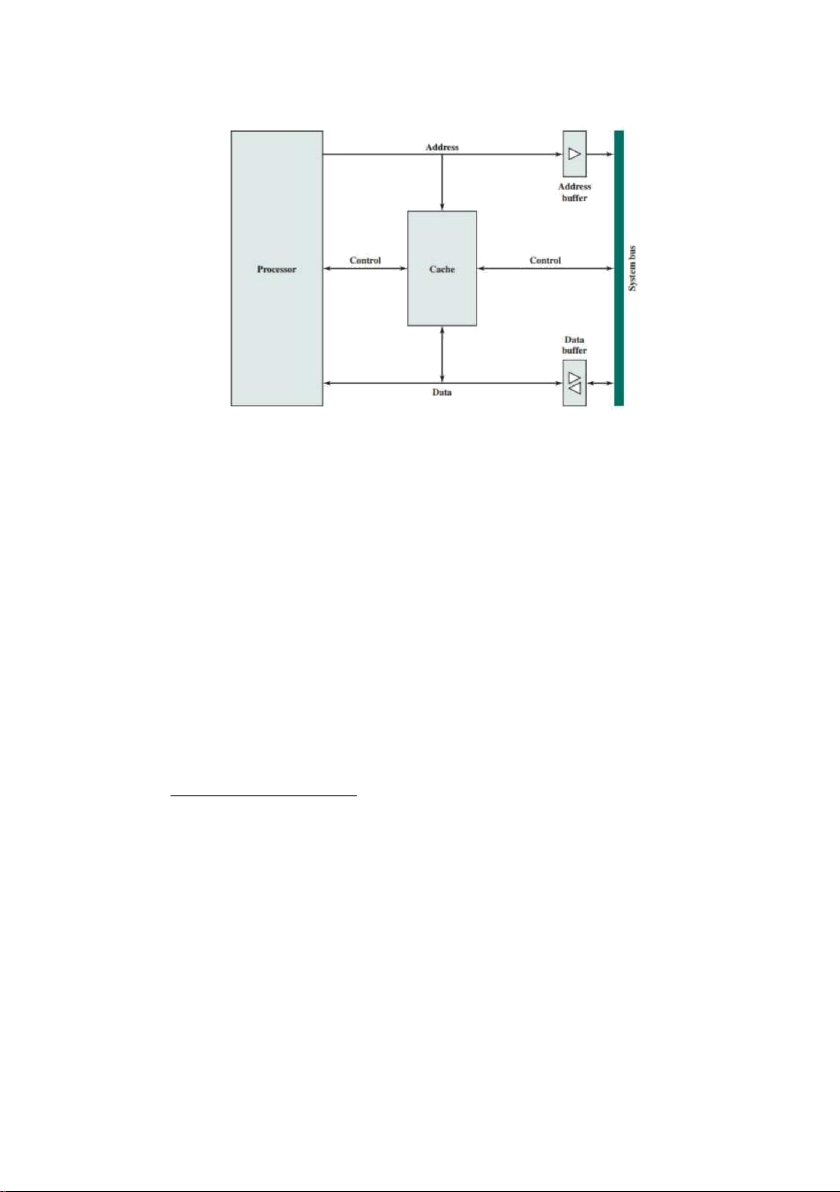

chứa từ đó được tải vào bộ đệm ẩn và từ được gửi đến bộ xử lý. Hình 4.5 cho thấy hai

hoạt động cuối cùng này xảy ra song song và phản ánh tổ chức được thể hiện trong

Hình 4.6, điển hình của các tổ chức bộ nhớ cache hiện đại. Trong tổ chức này, bộ đệm

kết nối với bộ xử lý thông qua dữ liệu, điều khiển và dòng địa chỉ. Các dòng dữ liệu

và địa chỉ cũng gắn vào bộ đệm dữ liệu và địa chỉ, gắn vào bus hệ thống mà từ đó bộ

nhớ chính được truy cập. Khi xảy ra lần truy cập bộ nhớ cache,

bộ đệm dữ liệu và địa chỉ bị vô hiệu hóa và giao tiếp chỉ giữa bộ xử lý và bộ nhớ

cache, không có hệ thống giao thông xe buýt. Khi xảy ra sự cố bỏ lỡ bộ nhớ

cache, địa chỉ mong muốn được tải lên bus hệ thống và dữ liệu được trả về thông

qua bộ đệm dữ liệu cho cả bộ đệm và bộ xử lý. Trong các tổ chức khác, bộ đệm

được xen kẽ vật lý giữa bộ xử lý và bộ nhớ chính cho tất cả dữ liệu, địa chỉ và

dòng điều khiển. Trong này trường hợp thứ hai, đối với một bộ nhớ cache, từ

mong muốn trước tiên được đọc vào bộ nhớ cache và sau đó chuyển từ bộ nhớ cache sang bộ xử lý.

Hình 4.5 Hoạt động đọc bộ nhớ cache

Hình 4.6 Tổ chức bộ nhớ cache điển hình

3. CÁC YẾU TỐ CỦA THIẾT KẾ BỘ NHỚ CACHE

Phần này cung cấp tổng quan về các tham số thiết kế bộ nhớ cache và báo

cáo một số kết quả điển hình. Đôi khi chúng tôi đề cập đến việc sử dụng bộ nhớ

đệm trong điện toán hiệu năng cao (HPC). HPC liên quan đến siêu máy tính và

phần mềm của chúng, đặc biệt là đối với các ứng dụng khoa học liên quan đến

một lượng lớn dữ liệu, vectơ và tính toán ma trận và sử dụng các thuật toán song

song. Thiết kế bộ nhớ cache cho HPC khá khác biệt so với các nền tảng và ứng

dụng phần cứng khác. Thật vậy, nhiều nhà nghiên cứu đã phát hiện ra rằng các

ứng dụng HPC hoạt động kém trên các kiến trúc máy tính sử dụng bộ nhớ cache

[BAIL93]. Các nhà nghiên cứu khác kể từ đó đã chỉ ra rằng hệ thống phân cấp bộ

nhớ cache có thể hữu ích trong việc cải thiện hiệu suất nếu phần mềm ứng dụng

được điều chỉnh để khai thác bộ nhớ cache [WANG99, PRES01].

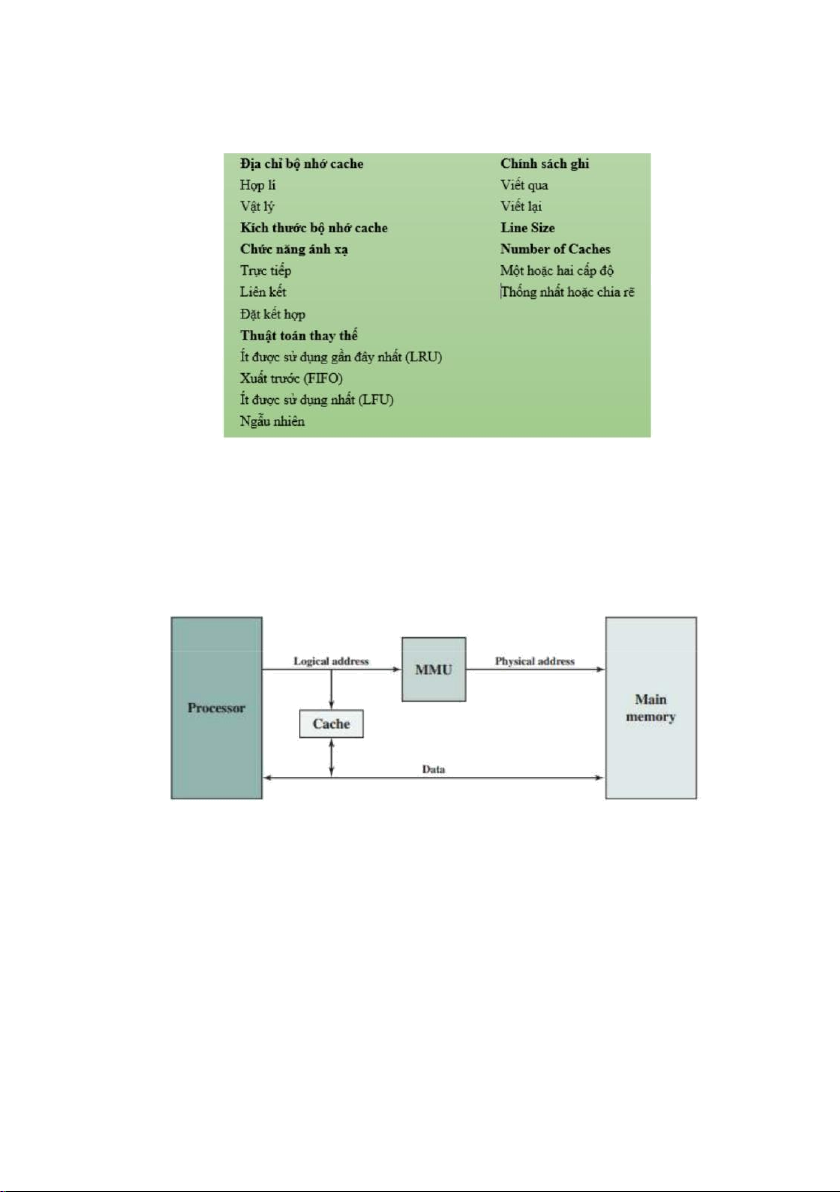

Mặc dù có một số lượng lớn các triển khai bộ nhớ cache, có một vài yếu tố

thiết kế cơ bản phục vụ để phân loại và phân biệt kiến trúc bộ nhớ cache. Bảng

4.2 liệt kê các yếu tố chính. Địa chỉ bộ nhớ cache

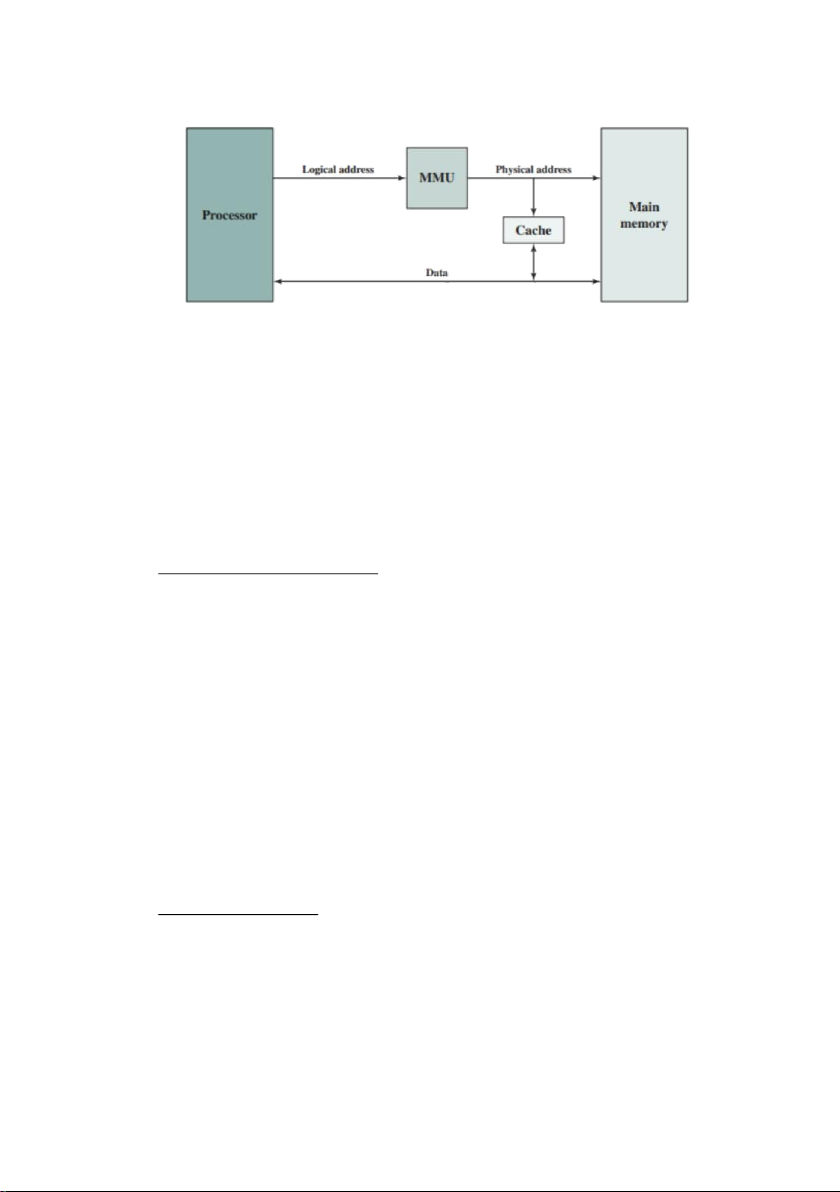

Hầu như tất cả các bộ xử lý không nhúng và nhiều bộ xử lý nhúng đều hỗ trợ bộ

nhớ ảo. Về bản chất, bộ nhớ ảo là một cơ sở cho phép các chương trình giải quyết bộ

nhớ từ quan điểm logic, mà không liên quan đến số lượng bộ nhớ chính có sẵn về mặt

vật lý. Khi bộ nhớ ảo được sử dụng, các trường địa chỉ của hướng dẫn máy chứa địa

chỉ ảo. Để đọc và ghi từ bộ nhớ chính, đơn vị quản lý bộ nhớ phần cứng (MMU) dịch

từng địa chỉ ảo thành một địa chỉ vật lý trong bộ nhớ chính.

Bảng 4.2 Các yếu tố của thiết kế bộ nhớ cache

Khi địa chỉ ảo được sử dụng, nhà thiết kế hệ thống có thể chọn đặt bộ đệm

giữa bộ xử lý và MMU hoặc giữa MMU và bộ nhớ chính (Hình 4.7). Bộ đệm

logic, còn được gọi là bộ đệm ảo, lưu trữ dữ liệu bằng địa chỉ ảo. Bộ xử lý truy

cập trực tiếp vào bộ đệm mà không cần thông qua MMU. Bộ đệm vật lý lưu trữ

dữ liệu bằng cách sử dụng địa chỉ vật lý bộ nhớ chính. (a) Logical cache (b) Physical cache

Hình 4.7 Bộ nhớ đệm logic và vật lý

Một ưu điểm rõ ràng của bộ đệm logic là tốc độ truy cập bộ nhớ cache nhanh

hơn so với bộ đệm vật lý, vì bộ đệm có thể phản hồi trước khi MMU thực hiện

dịch địa chỉ. Nhược điểm liên quan đến thực tế là hầu hết các hệ thống bộ nhớ ảo

cung cấp cho mỗi ứng dụng cùng một không gian địa chỉ bộ nhớ ảo. Đó là, mỗi

ứng dụng sẽ thấy một bộ nhớ ảo bắt đầu từ địa chỉ 0. Do đó, cùng một địa chỉ ảo

trong hai ứng dụng khác nhau đề cập đến hai địa chỉ vật lý khác nhau. Do đó, bộ

nhớ cache phải được hoàn toàn tuôn ra với mỗi chuyển đổi ngữ cảnh ứng dụng

hoặc các bit bổ sung phải được thêm vào mỗi dòng của bộ đệm ẩn để xác định

không gian địa chỉ ảo mà địa chỉ này đề cập đến.

Kích thước bộ nhớ cache

Mục thứ hai trong Bảng 4.2, kích thước bộ nhớ cache, đã được thảo luận. Chúng tôi

muốn kích thước của bộ nhớ đệm đủ nhỏ để chi phí trung bình tổng thể cho mỗi bit

gần bằng kích thước của bộ nhớ chính và đủ lớn để thời gian truy cập trung bình tổng

thể gần bằng thời gian truy cập của bộ nhớ cache. Có một số động lực khác để giảm

thiểu kích thước bộ nhớ cache. Bộ nhớ cache càng lớn, số lượng cổng liên quan đến

việc giải quyết bộ nhớ cache càng lớn. Kết quả là các bộ nhớ đệm lớn có xu hướng

chậm hơn một chút so với bộ nhớ đệm nhỏ — ngay cả khi được xây dựng với cùng

một công nghệ mạch tích hợp và đặt ở cùng một vị trí trên chip và bảng mạch. Khu

vực chip và bo mạch có sẵn cũng giới hạn kích thước bộ nhớ cache. Bởi vì hiệu suất

của bộ đệm rất nhạy cảm với bản chất của khối lượng công việc, nên không thể đạt

được kích thước bộ đệm "tối ưu" duy nhất. Bảng 4.3 liệt kê kích thước bộ nhớ cache

của một số bộ xử lý hiện tại và quá khứ. Chức năng ánh xạ