Preview text:

lOMoAR cPSD| 45740153

BỘ BÀI TẬP, CÂU HỎI TRẮC NGHIỆM

THẢO LUẬN MÔN KIẾN TRÚC MÁY TÍNH

BÀI THẢO LUẬN SỐ 1 CHƯƠNG 1

I. Câu hỏi trắc nghiệm

1. Bộ xử lý trung tâm CPU có chức năng:

A. Lấy chỉ thị từ bộ nhớ chính, giải mã và điều khiển ALU.

B. Thi hành các chương trình được chứa trong bộ nhớ chính.

C. Thực hiện các thao tác đơn giản.

D. Chứa các kết quả tạm thời và thông tin điều khiển nhất định.

2. Bộ xử lý trung tâm CPU gồm có:

A. Khối điều khiển và bộ nhớ trong.

B. Khối tính toán số học, Logic và bộ nhớ trong.

C. Khối điều khiển, khối tính toán số học và Logic, tập các Thanh ghi.

D. Tập các Thanh ghi và bộ nhớ.

3. Bộ xử lý trung tâm CPU là bộ phận: A. Thi hành lệnh. B. Lưu trữ lệnh. C. Giải mã lệnh. D. Biên dịch lệnh.

4. BUS nối bộ xử lý với Bộ nhớ có đặc điểm:

A. Có chiều dài ngắn và thường rất chậm.

C. Có chiều dài dài và thường rất nhanh.

B. Có chiều dài dài và thường rất chậm.

D. Có chiều dài ngắn và thường rất nhanh.

5. BUS nối bộ xử lý với bộ nhớ thuộc loại BUS nào sau đây: A. BUS rẻ tiền.

B. BUS đồng bộ. C. BUS chất lượng cao. D. BUS không đồng bộ.

6. Cấu trúc máy tính là thuật ngữ:

A. Là một môn học về việc thiết kế các chức năng của hệ thống. Nghiên cứu tính khả thi, giá thành, tốc độ

và các yếu tố kỹ thuật khác liên quan đến việc thiết kế. B. Nó liên quan đến ngôn ngữ lập trình máy tính. C.

Nó liên quan đến các khía cạnh lý thuyết cao cấp của việc thiết kế máy tính. D.

Quan tâm đến các đơn vị vận hành và sự kết nối giữa chúng nhằm hiện thực hóa những đặc tả

về kiến trúc, chẳng hạn như tín hiệu điều khiển, giao diện giữa máy tính với các thiết bị ngoại vi,... 7. Cấu

trúc phần cứng của máy tính

A. CPU, ALU, Bộ nhớ trong.

C. CPU, hệ thống vào ra, Bộ nhớ trong. B. CPU, CU, ALU. D. CPU, CU, Bộ nhớ trong.

8. Chức năng của BUS địa chỉ?

A. Vận chuyển địa chỉ để xác định ngăn nhớ hay cổng vào ra.

B. Vận chuyển lệnh từ bộ nhớ đến CPU.

C. Vận chuyển các tín hiệu điều khiển.

D. Vận chuyển dữ liệu giữa CPU, các Modul nhớ và Modul vào ra với nhau.

9. Chức năng của BUS điều khiển?

A. Vận chuyển lệnh từ bộ nhớ đến CPU. lOMoAR cPSD| 45740153

B. Vận chuyển dữ liệu giữa CPU, các Modul nhớ và Modul vào ra với nhau.

C. Vận chuyển các tín hiệu điều khiển.

D. Vận chuyển địa chỉ để xác định ngăn nhớ hay cổng vào ra.

10. Chức năng của BUS dữ liệu?

A. Vận chuyển địa chỉ để xác định ngăn nhớ hay cổng vào ra.

B. Vận chuyển lệnh từ bộ nhớ đến CPU và vận chuyển dữ liệu giữa CPU, các Modul nhớ và Modul vào ra với nhau.

C. Vận chuyển các tín hiệu điều khiển.

D. Vận chuyển dữ liệu giữa CPU, các Modul nhớ và Modul vào ra với nhau. II. Bài tập

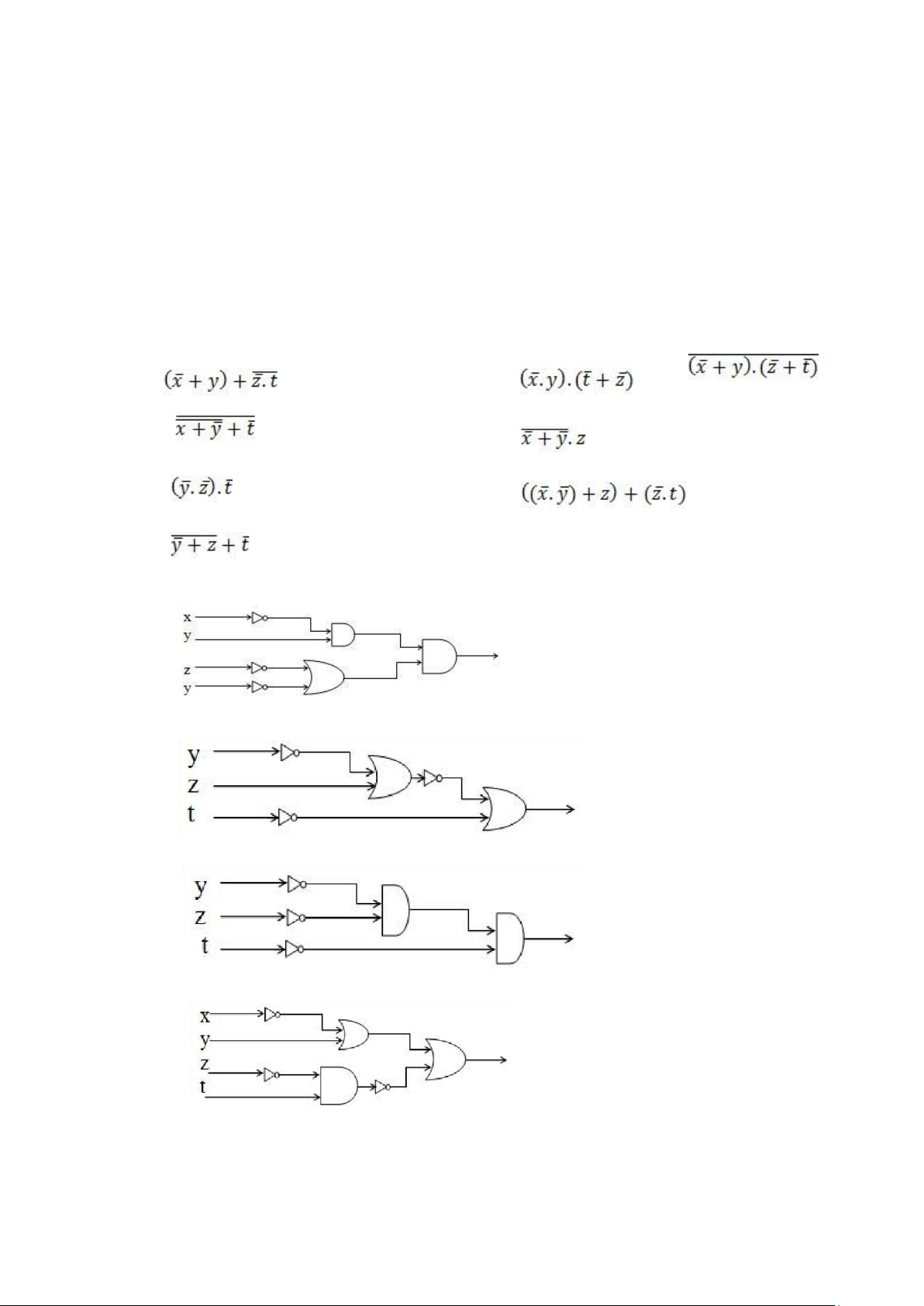

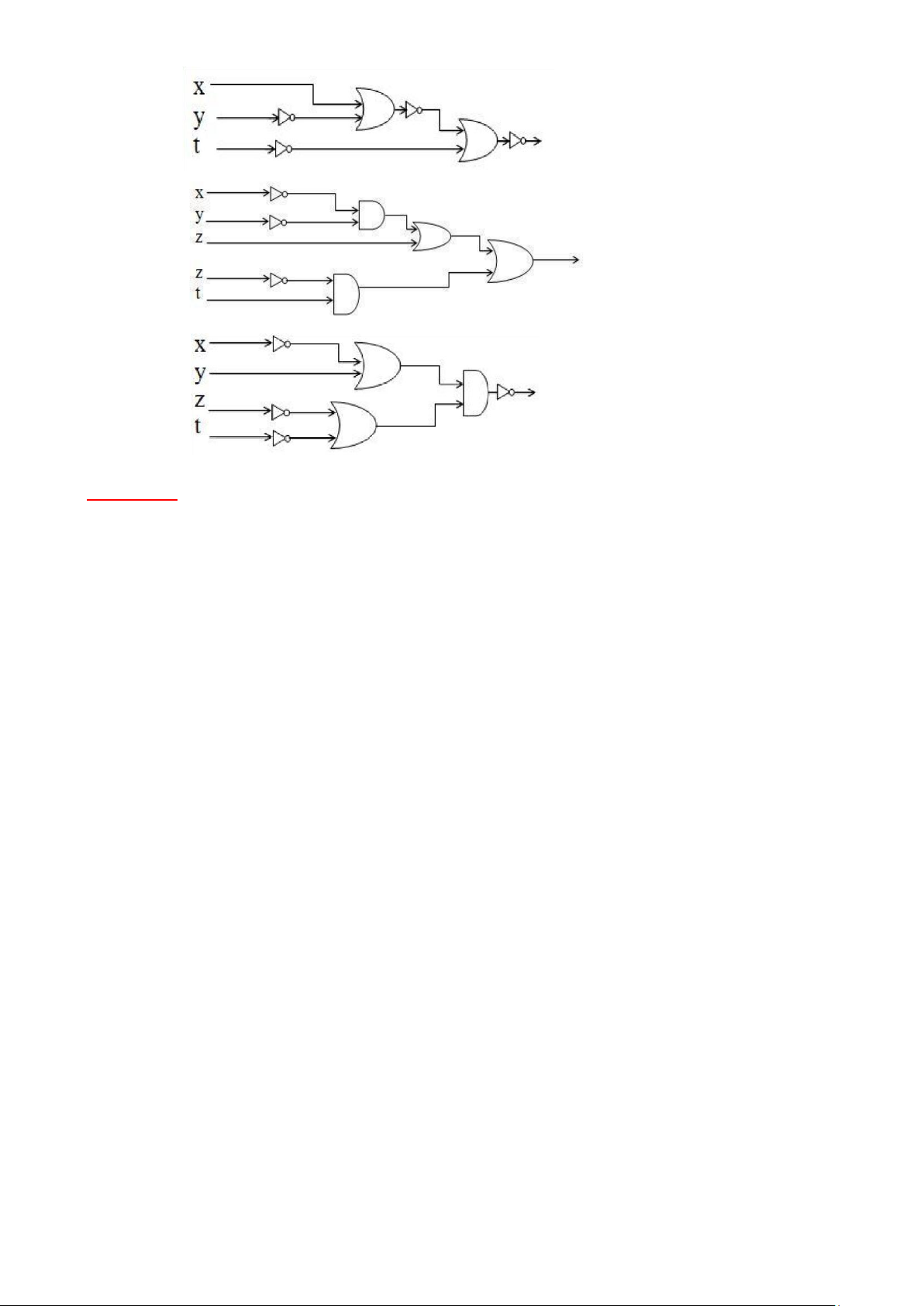

1. Dựng mạch Logic để tạo các hàm đầu ra sau: e. a. b. f. c. g. d. h.

2. Hãy chọn hàm đầu ra cho mạch Logic sau: a. b. c. d. lOMoAR cPSD| 45740153 e. f. g. CHƯƠNG 2

I. Câu hỏi trắc nghiệm

1. Cấu trúc chung của một mã lệnh gồm: A. Mã toán, Toán hạng

C. Toán hạng, Địa chỉ trực tiếp

B. Tiền tố, Mã toán, Toán hạng

D. Tiền tố, Mã toán, Toán hạng, Địa chỉ trực tiếp

2. Có mấy phương pháp xác định địa chỉ? A. 4 B. 5 C. 6 D. 7

3. Bộ đếm chương trình PC có nhiệm vụ: A.

Giữ địa chỉ của lệnh tiếp theo sẽ được nhận vào C. Chứa địa chỉ của ngăn nhớ dữ liệu B.

Chứa địa chỉ của ngăn nhớ đỉnh ngăn xếp

D. Giữ địa chỉ của lệnh đã thực hiện 4. Thanh ghi IR có nhiệm vụ: A.

Chứa lệnh hiện đang thi hành C. Trỏ tới lệnh tiếp theo sẽ được thi hành B.

Đếm số chương trình đang thực thi trong máy tính

D. Chứa các kết quả trung gian 5. Dãy các bước

dùng để thi hành chỉ thị gọi là chu kỳ:

A. Lấy lệnh - thi hành lệnh - lưu trữ kết quả

C. Thi hành lệnh - giải mã lệnh - lấy lệnh

B. Lấy lệnh - giải mã lệnh - thi hành lệnh

D. Lấy lệnh - thi hành lệnh - giải mã lệnh 6.

7. Việc thi hành một lệnh mã máy có thể chia làm mấy giai đoạn? A. 3 B. 4 C. 6 D. 5

8. Các giai đoạn thi hành một lệnh mã máy theo thứ tự thực hiện là:

A. Lấy lệnh - Giải mã lệnh - thi hành lệnh - lưu trữ kết quả - thâm nhập bộ nhớ trong

B. Lấy lệnh - Giải mã lệnh - thâm nhập bộ nhớ trong - thi hành lệnh - lưu trữ kết quả

C. Lấy lệnh - Giải mã lệnh - thi hành lệnh - thâm nhập bộ nhớ trong - lưu trữ kết quả

D. Lấy lệnh - thâm nhập bộ nhớ trong - Giải mã lệnh - thi hành lệnh - lưu trữ kết quả lOMoAR cPSD| 45740153

9. Chức năng của thanh ghi con trỏ dữ liệu DP là:

A. Trỏ vào đỉnh ngăn xếp C. Giữ địa chỉ của lệnh tiếp theo

B. Trỏ vào đáy ngăn xếp D. Chứa địa chỉ của ngăn nhớ dữ liệu mà CPU muốn truy cập

10. Ngăn xếp (stack) là vùng nhớ có cấu trúc: A. LILO B. FIFO C. FILO D. LIFO II. Bài tập

1. Hãy viết đoạn chương trình để tính giá trị biểu thức c = a + b bằng hệ lệnh 0, 1, 2, 3 toán hạng.

2. Hãy viết đoạn chương trình để tính giá trị biểu thức f = (a + b)/c-(d*e) bằng hệ lệnh 0, 1, 2, 3 toán hạng.

3. Hãy viết đoạn chương trình để tính giá trị biểu thức f = (a - b) / (c + d * e) bằng hệ lệnh 0, 1, 2, 3 toán hạng.

4. Hãy viết đoạn chương trình để tính giá trị biểu thức (a * b / c) + (d - e * g) bằng hệ lệnh 0, 1, 2, 3 toán hạng.

5. Hãy cho biết câu lệnh sau các toán hạng được xác định bởi chế độ địa chỉ nào? MOV AX,BX CHƯƠNG 3

I. Câu hỏi trắc nghiệm

Câu 1. Bộ xử lý trung tâm CPU gồm có:

A. Khối điều khiển và bộ nhớ trong.

B. Khối tính toán số học, Logic và bộ nhớ trong.

C. Khối điều khiển, khối tính toán số học và Logic, tập các Thanh ghi.

D. Tập các Thanh ghi và bộ nhớ Câu 2. Cấu trúc phần cứng của máy tính

A. CPU, ALU, Bộ nhớ trong.

C. CPU, hệ thống vào ra, Bộ nhớ trong. B. CPU, CU, ALU. D. CPU, CU, Bộ nhớ trong.

Câu 3. Đơn vị điều khiển (CU) có nhiệm vụ:

A. Làm các phép tính trên các số liệu.

B. Lấy chỉ thị từ bộ nhớ chính, giải mã và điều khiển ALU.

C. Thi hành các chương trình được chứa trong bộ nhớ chính.

D. Tác động vào các mạch điện để thi hành các lệnh.

Câu 4. Đơn vị tính toán số học và Logic (ALU) có nhiệm vụ;

A. Làm phép tính trên các số liệu

B. Đảm bảo thi hành các lệnh một cách tuần tự

C. Tác động vào các mạch điện để thi hành các lệnh

D. Lấy lệnh từ bộ nhớ trong

Câu 5. Kỹ thuật ống dẫn có đặc điểm:

A. Làm giảm tốc độ thực hiện các lệnh

B. Làm tăng tốc độ thực hiện các lệnh

C. Có ít thanh ghi khác nhau dùng cho các tác vụ đọc viết

D. Tất cả các giai đoạn của lệnh không được thi hành cùng một lúc. lOMoAR cPSD| 45740153 II. Bài tập

1. Nêu cấu tạo, chức năng của đơn vị tính toán số học và logic ALU?

2. Vẽ hình để mô tả kỹ thuật đường ống. Kỹ thuật đường ống làm tăng tốc độ CPU lên bao nhiêu lần (theo lý

thuyết)? Tại sao trên thực tế sự gia tăng này lại ít hơn? lOMoAR cPSD| 45740153

BÀI THẢO LUẬN SỐ 2 CHƯƠNG 4

I. Câu hỏi trắc nghiệm

1. Chọn đáp án sai về qui tắc phân cấp bộ nhớ. Qui tắc chung của hệ thống phân cấp bộ nhớ dựa trên :

A. Mối quan hệ về không gian B. Mối quan hệ logic

C. Mối quan hệ về thời gian

D. Mối quan hệ tuần tự

2. Người ta đã thống kê được rằng các lệnh trong chương trình hầu hết được thực hiện một cách tuần tự chiếm: A. 50-60 % B. 40-50% C. 30-40% D. 70-80%

3. Mô hình phân cấp bộ nhớ hai cấp:

A. Processor – Secondarymemory - Mainmemory C. Secondarymemory - Mainmemory - Processor

B. Mainmemory - Processor –Secondarymemory D. Processor - Mainmemory – Secondarymemory

4. Qui trình xây dựng bộ nhớ gồm A. 4 bước B. 5 bước C. 6 bước D. 7 bước

5. Khi xây dựng bộ nhớ có dung lượng 1MB * 8bit từ IC 256KB * 8bit thì số IC cần để xây dựng bộ nhớ là A. 8 B. 4 C. 6 D. 7

6. Khi xây dựng bộ nhớ có dung lượng 1MB * 8bit từ IC 256KB * 8bit thì số lượng đường địa chỉ cần sử dụng cho bộ nhớ là A. 20 B. 8 C. 10 D. 12

7. Khi xây dựng bộ nhớ có dung lượng 1MB * 8bit từ IC 256KB * 8bit thì số lượng đường địa chỉ cần sử dụng cho IC nhớ là A. 20 B. 14 C. 18 D. 23

8. Khi xây dựng bộ nhớ có dung lượng 1MB * 8bit từ IC 256KB * 8bit thì số lượng IC mở đồng thời là A. 1 B. 2 C. 3 D. 4

9. Khi xây dựng bộ nhớ có dung lượng 1MB * 32bit từ IC 256KB * 8bit thì số IC cần để xây dựng bộ nhớ là A. 18 B. 16 C. 12 D. 8 10.

Khi xây dựng bộ nhớ có dung lượng 1MB * 32bit từ IC 256KB * 8bit thì số lượng đường địa chỉ cần sử dụng cho bộ nhớ là A. 22 B. 24 C. 20 D. 18 II. Bài tập

1. Tính tỷ suất lỗi trang (PF) cho một tiến trình truy nhập bộ nhớ theo các trang như sau: 1, 1, 3, 2, 5, 3, 6, 1, 5,

3, 4, 5, 6. Biết bộ nhớ có 3 khung trang, thay thế dữ liệu theo phương pháp FIFO

2. Tính tỷ suất lỗi trang (PF) cho một tiến trình truy nhập bộ nhớ theo các trang như sau: 1, 1, 3, 2, 5, 3, 6, 1, 5,

3, 4, 5, 6. Biết bộ nhớ có 3 khung trang, thay thế dữ liệu theo phương pháp FIFO

3. Tính tỷ suất lỗi trang (PF) cho một tiến trình truy nhập bộ nhớ theo các trang như sau: 1, 1, 3, 2, 5, 3, 3, 1, 5,

2, 4, 3, 1, 1 Biết bộ nhớ có 3 khung trang, thay thế dữ liệu theo phương pháp FIFO

4. Tính tỷ suất lỗi trang (PF) cho một tiến trình truy nhập bộ nhớ theo các trang như sau: 1, 1, 3, 2, 5, 3, 3, 1, 5,

2, 4, 3, 1, 1. Biết bộ nhớ có 3 khung trang, thay thế dữ liệu theo phương pháp LRU

5. Cho Thời gian truy nhập bộ nhớ chính là 100ns. Thời gian truy nhập bộ nhớ Cache là 10ns. Tỷ số trúng cache

là = 90%. Truy cập bộ nhớ 10 lần. Tỷ lệ thời gian không cache/ thời gian có cache là lOMoAR cPSD| 45740153 A. 4.2 lần B. 7.3 lần C. 5.3 lần D. 6.2 lần

6. Cho Thời gian truy nhập bộ nhớ chính là 100ns. Thời gian truy nhập bộ nhớ Cache là 20ns. Tỷ số trúng cache

là = 80%. Truy cập bộ nhớ 10 lần. Tỷ lệ thời gian không cache/ thời gian có cache là CHƯƠNG 5 Câu hỏi trắc nghiệm

1. Màn hình có chức năng A. Xử lý thông tin

B. Hiển thị thông tin C. In thông tin D. Nhập thông tin

2. Card màn hình có chức năng A. Xử lý thông tin

B. Hiển thị thông tin C. Xử lý đồ họa D. Nhập thông tin

3. Bàn phím là được gọi là thiết bị

A. Nhập chuẩn B. In thông tin C. Xuất thông tin D. Xem thông tin

4. Bàn phím sử dụng phương pháp truyền A. Song song B. Đồng bộ C. Bất đồng bộ D. Nối tiếp

5. Quá trình vào ra dữ liệu giữa thiết bị ngoại vi và bộ nhớ theo phương thức DMA là:

A. Truy cập bộ nhớ gián tiếp qua CPU B. Vào ra

dữ liệu theo ngắt cứng.

C. Truy cập bộ nhớ trực tiếp.

D. Vào ra dữ liệu theo ngắt mềm.

6. Viết chương trình cho bộ xử lý:

A. Chương trình ngắn, có ít lệnh trợ giúp ngôn ngữ cấp cao.

B. Chương trình dài, có ít lệnh trợ giúp ngôn ngữ cấp cao.

C. Chương trình ngắn, có nhiều lệnh trợ giúp ngôn ngữ cấp cao.

D. Chương trình dài, có nhiều lệnh trợ giúp ngôn ngữ cấp cao.

7. SIMD thuộc loại máy tính:

A. Một dòng lệnh, một dòng số liệu.

C. Một dòng lệnh, nhiều dòng số liệu.

B. Nhiều dòng lệnh, một dòng số liệu.

D. Nhiều dòng lệnh, nhiều dòng số liệu. 8. Máy tính RISC là máy

A. Reduce instruction set computer B.

C. Redundance instruction set computer

Máy tính có tập chỉ thị rút gọn rất nhỏ D. a và b đúng

9. MIMD thuộc loại máy tính:

A. Nhiều dòng lệnh, nhiều dòng số liệu.

C. Nhiều dòng lệnh, một dòng số liệu.

B. Một dòng lệnh, nhiều dòng số liệu.

D. Một dòng lệnh, một dòng số liệu.

10. MISD thuộc loại máy tính:

A. Nhiều dòng lệnh, nhiều dòng số liệu.

C. Nhiều dòng lệnh, một dòng số liệu.

B. Một dòng lệnh, nhiều dòng số liệu.

D. Một dòng lệnh, một dòng số liệu.

11. SISD thuộc loại máy tính:

A. Nhiều dòng lệnh, nhiều dòng số liệu.

C. Nhiều dòng lệnh, một dòng số liệu.

B. Một dòng lệnh, nhiều dòng số liệu.

D. Một dòng lệnh, một dòng số liệu. lOMoAR cPSD| 45740153 CHƯƠNG 6 Câu hỏi trắc nghiệm

1. Vi mạch DMA được dùng để điều khiển việc trao đổi dữ liệu giữa A. CPU và Memory B. CPU và Disk C. Memory và Disk D. cả A,B,C

2. Giao tiếp song song(Parallel) thường được phục vụ cho thiết bị nào sau đây A. Keyboard B. Printer C. Mouse D. Monitor

3. Phương pháp truyền nối tiếp(Serial) đồng bộ là

A. có thêm đường tín hiệu đồng bộ với đường dữ liệu C. có thêm bít đồng bộ với đường dữ liệu

B. có thêm bít đồng bộ ở hai đầu đoạn bít dữ liệu D. cả A,B,C

4. Phương pháp truyền nối tiếp(Serial) bất đồng bộ là:

C. có bít start ở đầu đoạn bít dữ liệu và bít stop ở cuối

A. có thêm đường tín hiệu đồng bộ với đường dữ liệu đoạn dữ liệu

B. có thêm các bít đồng bộ ở hai đầu đoạn bít tín hiệu D. cả B,C

5. Bít chẵn lẻ được thêm vào khung của đoạn dữ liệu nối tiếp để

A. Làm chỉ số cho đoạn B. Đánh dấu đoạn

C. Để phát hiện lỗi đoạn dữ liệu D. mã hóa đoạn dữ liệu dữ liệu dữ liệu

6. Trong chuyền dữ liệu nối tiếp, một đoạn SDU thường có

A. 1 bit start, 7 bits số liệu, 1 bit chẵn lẻ và 1 bit stop C. 1 bit start, 8 bits số liệu, 2 bit chẵn lẻ và 1 bit stop

B. 1 bit start, 8 bits số liệu, 1 bit chẵn lẻ và 1 bit stop D. cả A,B,C

7. Chuẩn ghép nối RS-232 có các phương thức nối ghép là

A. Đơn công (simplex connection): dữ liệu chỉ được truyền theo 1 hướng.

B. Bán song công (half-duplex): dữ liệu truyền theo 2 hướng, nhưng mỗi thời điểm chỉ được truyền theo 1 hướng

C. Song công (full-duplex): số liệu được truyền đồng thời theo 2 hướng D. cả A,B,C

8. Màn hình CRT là màn hình hiển thị hình ảnh qua phương pháp sử dụng A. ống phóng tia âm cực B. ma trận tia âm cực C. chùm tia âm cực D. cả A,B,C

9. Màn hình có chức năng A. Xử lý thông tin B. Hiển thị thông tin C. In thông tin D. cả A,B,C

10. Card màn hình có chức năng A. Xử lý thông tin B. Hiển thị thông tin C. Xử lý đồ họa D. cả A,B,C

11. Bàn phím là được gọi là thiết bị A. nhập chuẩn B. nhập C. xuất D. cả A,B,C

12. Bàn phím sử dụng phương pháp truyền A. song song B. đồng bộ C. bất đồng bộ D. nối tiếp

13. Bàn phím sử dụng phương pháp truyền A. song song B. nối tiếp đồng bộ

C. nối tiếp bất đồng bộ D. cả A, B, C lOMoAR cPSD| 45740153

14. Phương pháp truyền nối tiếp bất đồng bộ của bàn phím sử dụng A. 6 bit dữ liệu B. 8 bit dữ liệu C. 7 bit dữ liệu D. 9 bit dữ liệu

15. Bít nào sau đây trong chế độ chuyền nối tiếp bất đồng bộ luôn có giá trị bằng 0 A. Start B. Stop C. Party D. cả A,B,C

16. Chuẩn giao tiếp AT của bàn phím có số chân được sử dụng là A. 3 B. 4 C. 6 D. 5

17. Chân clock của chuẩn giao tiếp AT cho bàn phím là chân số A. 3 B. 4 C. 2 D. 1

18. Chân dữ liệu của chuẩn giao tiếp AT cho bàn phím là chân số A. 3 B. 4 C. 2 D. 1

19. Chân Reset của chuẩn giao tiếp AT cho bàn phím là chân số A. 3 B. 4 C. 2 D. 1

20. Chuẩn giao tiếp PS2 của bàn phím có số chân là A. 4 B. 6 C. 5 D. 7

21. Chân dữ liệu của chuẩn giao tiếp PS2 cho bàn phím là chân số A. 4 B. 1 C. 3 D. 2

22. Chân clock của chuẩn giao tiếp PS2 cho bàn phìm là chân số A. 2 B. 3 C. 5 D. 4

23. Hai chân tín hiệu nào không dùng trong chuẩn giao tiếp PS2 cho bàn phím? A. 2 và 3 B. 2 và 4 C. 2 và 5 D. 2 và 6 24. Đĩa từ là đĩa

A. lưu trữ thông tin trên đĩa từ

C. không bị mất thông tin khi mất điện

B. sử dụng kĩ thuật từ hóa và khủ từ để ghi và xóa dữ liệu D. cả A,B,C

25. Các đường tròn đồng tâm trên đĩa từ được gọi là

A. các rãnh từ B. các track C. các cung D. cả A, B

26. Các cung từ trên đĩa từ được gọi là A. các sector B. các track

C. các cluster D. cả A, B, C

27. Tập hợp nhiều hơn từ 2 sector được gọi là 1 A. track B. cluster C. group sectors D. cả A, B, C

28. Tập hợp các track có cùng số hiệu nhưng nằm trên các đĩa cứng khác nhau được gọi là A. group tracks B. partion tracks C. cylinder D. cả A, B, C

29. Thiết bị được dùng để gắn các đĩa từ lên nó, chúng được nối trực tiếp với động cơ quay đĩa cứng là

A. trục quay B. đầu đọc ghi C. mạch điều khiển D. cả A, B, C

30. Thiết bị được sử dụng để di chuyển đầu đọc ghi được gọi là lOMoAR cPSD| 45740153 A. trục quay

B. cần di chuyển đầu đọc ghi C. mô tơ di chuyển D. cả A, B, C

31. Thiết bị nào được sử dụng để điều khiển mọi hoạt động của ổ đĩa cứng A. trục quay B. Mô tơ quay

C. Mạch điều khiển (PCB) D. cả A, B, C

32. Tốc độ quay của các đĩa cứng trên ổ đĩa cứng khoảng từ A. 3600rmp đến 15000rmp B. 7200rmp đến 15000rmp C. 12000rmp đến 15000rmp D. cả A, B, C

33. Ngày nay để tăng tốc cho các ổ đĩa cứng người thường được tích hợp cho ổ đĩa cứng thêm A. bộ nhớ đệm(cache)

B. mạch tích hợp cao cấp (APCB) C. L3 cache D. cả A, B, C

33. Ngày nay để tăng tốc cho các ổ đĩa cứng người thường được tích hợp cho ổ đĩa cứng thêm A. bộ nhớ đệm(cache)

B. mạch tích hợp cao cấp (APCB) C. L3 cache D. cả A, B, C

34. Để đọc và ghi dữ liệu, đầu từ của ổ đĩa được thường được chuyển từ

A. tâm đĩa ra ngoài mép đĩa

B. từ mép đĩa về tâm đĩa C. xung quanh đĩa D. cả A, B

35. Các chuẩn giao tiếp với ổ đĩa cứng ngày nay hay được sử dụng là A. ATA B. SATA1 C. SATA2 D. cả A, B, C

36. Trong ổ đĩa quang thiết bị nào được dùng để phân tách tia laser thành 3 tia tán xạ A. Kính tán xạ

B. Thấu kính chuẩn trực C. Lăng kính phân xạ D. Gương quay

37. Trong ổ đĩa quang thiết bị nào được dùng để biến chùm tia tán xạ thành chùm tia song song A. Gương quay

B. Thấu kính chuẩn trực C. Lăng kính phân xạ D. cả A, B, C

38. Trong ổ đĩa quang, thiết bị nào được sử dụng để thu tia phản xạ từ bề mặt đĩa A. Bộ xử lý tín hiệu B. Diode cảm quang C. Gương quay D. Bộ điều khiển

39. Trong ổ đĩa quang, thiết bị nào có nhiều chức năng như điều khiển hội tụ tia laser, quay bàn quay và xử lý các lệnh điều khiển từ máy tính A. Bộ xử lý tín hiệu B. Bàn quay đĩa C. Bộ điều khiển D. cả A,B,C

40. Trong ổ đĩa quang, thiết bị nào được sử dụng để điều chỉnh kích thước tia laser lên bề mặt đĩa A. Thấu kính cầu B. Thấu kính trụ C. Thấu kính hội tụ D. cả A,B,C

41. Các giao thức cache kết hợp được thiết kế để giải quyết cho hệ thống nào sau đây A. Symmetric Multiprocesors B. Cluster C. Nonunifrom Memory Access D. cả A,B,C

42. Mạng tốc độ cao Fast Ethernet hay Gigabit được sử dụng cho hệ thống nào sau đây A. Symmetric Multiprocesors B. Cluster C. Nonunifrom Memory Access D. cả A,B,C

43. Khả năng mở rộng cao, độ tin cậy cao, tốc độ xử lý nhanh và chi phí đầu tư thấp là những đặc trưng của hệ thống nào sau đây A. Symmetric Multiprocesors B. Cluster C. Nonunifrom Memory Access D. cả A,B,C

44. Mô hình nào sau đây có thời gian truy cập các vùng nhớ khác nhau trong hệ thống là như nhau A. Symmetric Multiprocesors B. Cluster C. NUMA D. cả A,B,C

45. Mô hình nào sau đây có thời gian truy cập các vùng nhớ khác nhau trong hệ thống là khác nhau A. Symmetric B. Cluster C. Nonunifrom Memory D. cả B và C lOMoAR cPSD| 45740153 Multiprocesors Access

46. Mạng liên kết trong có mấy tiêu chuẩn để đánh giá A. 1 B. 2 C. 3 D. 4

47. Đường kính của mạng (M) liên kết trong là

A. đường ngắn nhất kết nối giữa P1 và P2 C. đường dài nhất kết nối giữa P1 và P2

B. đường ngắn nhất kết nối giữa P1 và P2 với P1,P2 thuộc M D. cả A,B,C

48. Trong hệ thống sử dụng mạng liên kết trong, số các liên kết tới bộ xử lý được gọi là

A. Đường kính của mạng C. Bậc của bộ xử lý

B. Thông lượng giữa hai tập hợp các bộ xử lý của mạng D. cả A,B,C

49. Một mạng liên kết M là tốt nếu nó có đặc tính nào sau đây A. Đường kính nhỏ

C. Bậc của bộ xử lý nhỏ

B. Thông lượng giữa hai tập bất kỳ của mạng lớn D. cả A,B,C

50. Mạng liên kết tuyến tính node đầu có bậc bằng mấy A. 1 B. 2 C. 3 D. 4

51. Bất lợi cuả đĩa bán dẫn (flash disk) là: A. Khó chế tạo.

B. Khó điều khiển. C. Giá tiền còn cao.

D. Tất cả các câu trên đều đúng.

52. Đĩa quang có đặc điểm gì?

A. Khó lấy rời khỏi ổ đĩa và giá tiền rẽ.

C. Có thể lấy rời khỏi ổ đĩa dễ dàng và giá thành còn cao.

B. Có thể lấy rời khỏi ổ đĩa dễ dàng và giá thành rẻ.

D. Khó lấy rời khỏi ổ đĩa và giá tiền còn cao.

53. Bus vào/ra thuộc loại bus nào sau đây: A. Bus đồng bộ. B. Bus không đồng bộ. C. Bus chất lượng cao. D. Bus rẻ tiền.

54. Các loại BUS nào sử dụng trong kiến trúc vào/ra của máy tính số là: A. BUS địa chỉ

C. Cả 3 loại BUS: Dữ liệu, địa chỉ, điều khiển. B. BUS điều khiển D. BUS dữ liệu.

55. Quá trình vào ra dữ liệu giữa thiết bị ngoại vi và bộ nhớ theo phương thức DMA là:

A. Truy cập bộ nhớ gián tiếp qua CPU C. Truy cập bộ nhớ trực tiếp.

B. Vào ra dữ liệu theo ngắt cứng.

D. Vào ra dữ liệu theo ngắt mềm.

56. Tín hiệu RD/WR trong BUS điều khiển của CPU có chức năng:

A. Điều khiển việc treo CPU

C. Điều khiển việc giải mã dữ liệu

B. Điều khiển việc đếm lệnh

D. Điều khiển việc đọc/ghi dữ liệu.

57. Bus vào/ra có đặc điểm:

A. Có thể có chiều dài nhỏ và có khả năng kết nối với nhiều loại ngoại vi.

B. Có thể có chiều dài nhỏ và có khả năng kết nối với 1 loại ngoại vi.

C. Có thể có chiều dài lớn và có khả năng kết nối vớI 1 loại ngoại vi.

D. Có thể có chiều dài lớn và có khả năng kết nối với nhiều loại ngoại vi.