Preview text:

!""

Chương 1: Gi i thi u chung v b vi x lý.

Trư ng ðH Công nghi p Tp.HCM. CHƯƠNG 1 GI I THI U CHUNG V B VI X LÝ

I. S PHÁT TRI N C A CÁC B VI X LÝ: 1. Th! h" 1 (1971 $ 1973):

ð c ñi m chung c a các vi x lý th h này: • Bus d li u: 4 bit. • Bus ñ"a ch#: 12 bit. • Công ngh ch t(o: PMOS. •

T/c ñ0 th1c hi n l nh: 10 – 60 5s/l nh v7i fCLOCK = 0,1 – 0,8 MHz.

M0t s/ b0 vi x lý ñ c trưng cho th h này: 4040 (Intel), PPSD4 (Rockwell International), … 2. Th! h" 2 (1974 $ 1977):

ð c ñi m chung c a các vi x lý th h này: • Bus d li u: 8 bit. • Bus ñ"a ch#: 16 bit. •

Công ngh ch t(o: NMOS ho c CMOS. •

T/c ñ0 th1c hi n l nh: 1 – 8 5s/l nh v7i fCLOCK = 1 – 5 MHz.

M0t s/ b0 vi x lý ñ c trưng cho th h này: 6502 (Mos Technology), 6800/6809 (Motorola),

8080/8085 (Intel), Z80 (Zilog), … 3. Th! h" 3 (1978 $ 1982):

ð c ñi m chung c a các vi x lý th h này: • Bus d li u: 16 bit. • Bus ñ"a ch#: 20 D 24 bit. • Công ngh ch t(o: HMOS. •

T/c ñ0 th1c hi n l nh: 0,1 – 1 5s/l nh v7i fCLOCK = 5 – 10 MHz.

M0t s/ b0 vi x lý ñ c trưng cho th h này: 68000 / 68010 (Motorola), 8086 / 80186 / 80286 (Intel), … 4. Th! h" 4 (1983 $ nay):

ð c ñi m chung c a các vi x lý th h này: • Bus d li u: 32 D 64 bit. • Bus ñ"a ch#: 32 bit. • Công ngh ch t(o: HCMOS. •

T/c ñ0 th1c hi n l nh: 0,01 – 0,1 5s v7i fCLOCK = 20 – 100 MHz.

M0t s/ b0 vi x lý ñ c trưng cho th h này: 68020 / 68030 / 68040 / 68060 (Motorola), 80386 / 80486 / Pentium (Intel), …

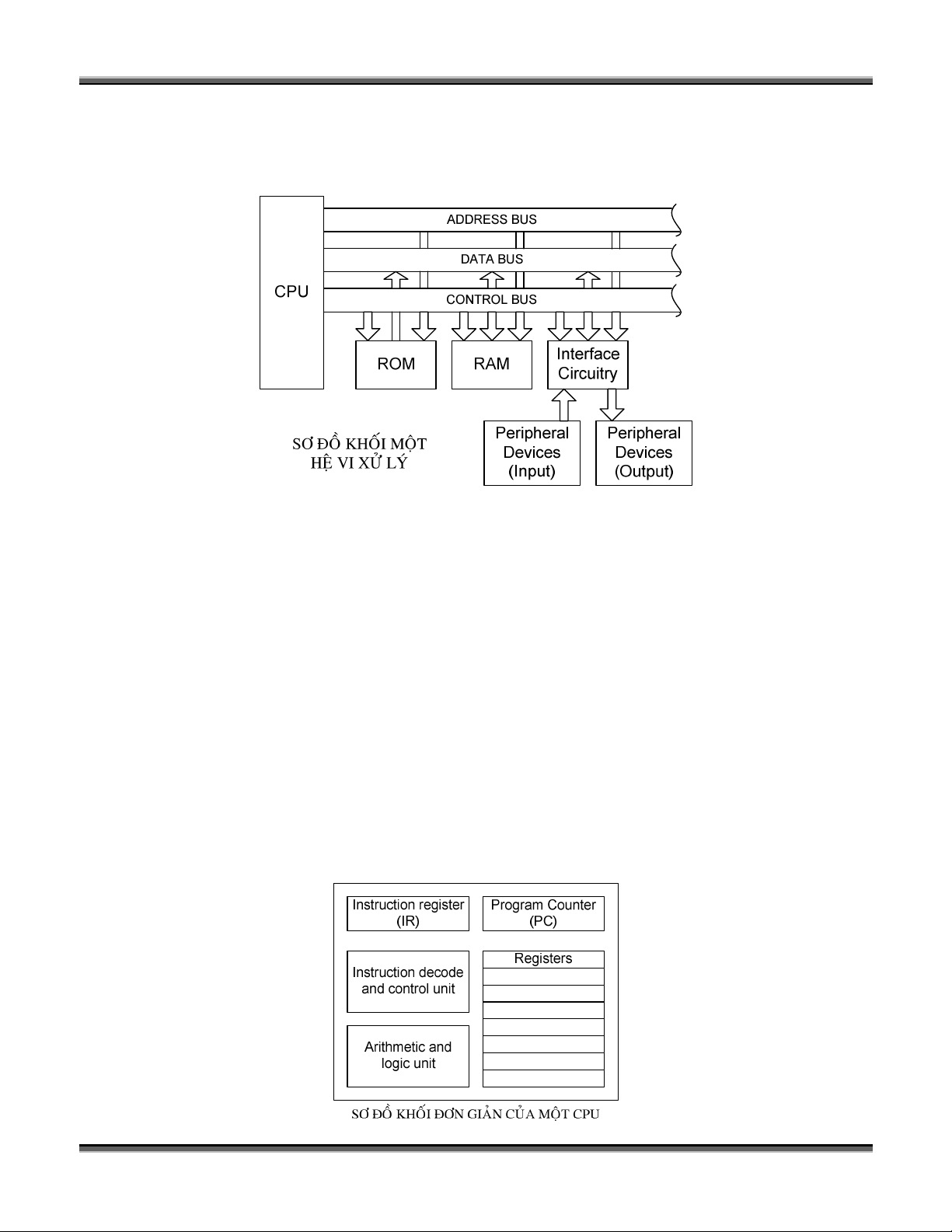

II. SƠ ð) KH+I C A M T H VI X LÝ: ð"nh nghĩa h vi x lý: •

KhN năng ñưPc lQp trình ñ thao tác trên các d li u mà không cVn s1 can thi p c a con ngưWi.

Chương 1: Gi i thi u chung v b vi x lý.

Trư ng ðH Công nghi p Tp.HCM. •

KhN năng lưu tr và phXc hYi d li u. TZng quát, h vi x lý gYm: •

PhVn c\ng (Hardware): các thi t b" ngo(i vi → ñ giao ti p v7i con ngưWi. •

PhVn m]m (Software): chương trình → ñ x lý d li u.

CPU (Central Processing Unit): ñơn v" x lý trung tâm.

RAM (Random Access Memory): b0 nh7 truy xuct ngdu nhiên.

ROM (Read Only Memory): b0 nh7 ch# ñec.

Interface Circuitry: m(ch ñi n giao ti p.

Peripheral Devices (Input): các thi t b" ngo(i vi (thi"t b$ nh%p).

Peripheral Devices (Output): các thi t b" ngo(i vi (thi"t b$ xu't). Address bus: bus ñ"a ch#. Data bus: bus d li u. Control bus: bus ñi]u khi n.

III. ðƠN V- X LÝ TRUNG TÂM:

CPU ñóng vai trò ch ñ(o trong h vi x lý, nó quNn lý tct cN các ho(t ñ0ng c a h và th1c hi n

tct cN các thao tác trên d li u.

CPU là m0t vi m(ch ñi n t có ñ0 tích hPp cao. Khi ho(t ñ0ng, CPU ñ,c mã l nh ñưPc ghi dư7i

d(ng các bit 0 và bit 1 tj b0 nh7, sau ñó nó sk th1c hi n gi/i mã các l nh này thành dãy các xung ñi]u

khi n tương \ng v7i các thao tác trong l nh ñ ñi]u khi n các kh/i khác th0c hi n tjng bư7c các thao

tác ñó và tj ñó t(o ra các xung ñi]u khi n cho toàn h . !

Chương 1: Gi i thi u chung v b vi x lý.

Trư ng ðH Công nghi p Tp.HCM.

IR (Instruction Register): thanh ghi l nh.

PC (Program Counter / Instruction Pointer): b0 ñ m chương trình / con trm l nh.

Instruction decode and control unit: ñơn v" giNi mã l nh và ñi]u khi n.

ALU (Arithmetic and Logic Unit): ñơn v" s/ hec và logic. Registers: các thanh ghi.

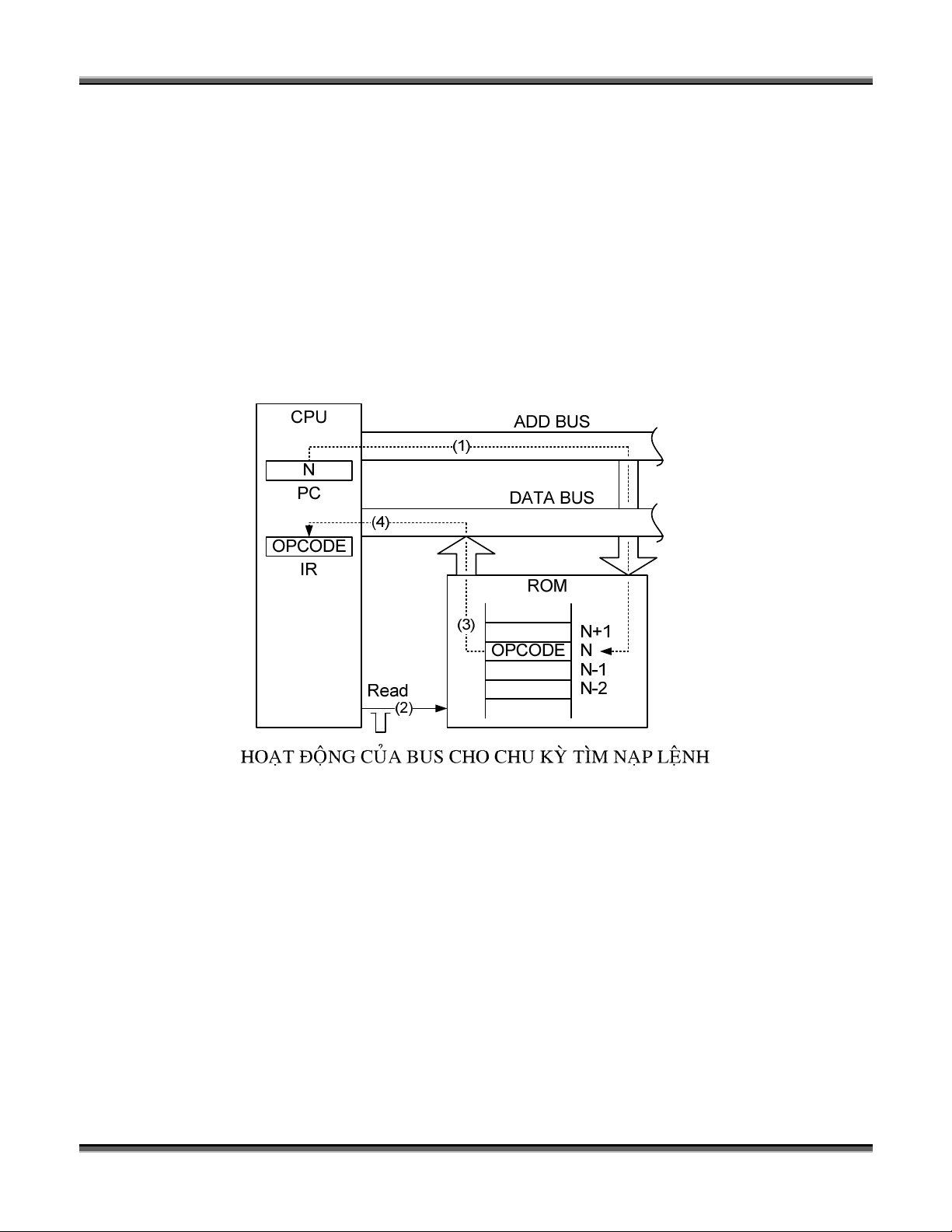

Tóm l(i, khi ho(t ñ0ng CPU sk th1c hi n liên tXc 2 thao tác: tìm n=p l nh và gi/i mã – th0c hi n l nh. • Thao tác tìm n=p l nh:

N0i dung c a thanh ghi PC ñưPc CPU ñưa lên bus ñ"a ch# (1).

Tín hi u ñi]u khi n ñec (Read) chuy n sang tr(ng thái tích c1c (2).

Mã l nh (Opcode) tj b0 nh7 ñưPc ñưa lên bus d li u (3).

Mã l nh ñưPc chuy n vào trong thanh ghi IR trong CPU (4).

N0i dung c a thanh ghi PC tăng lên m0t ñơn v" ñ chunn b" tìm n(p l nh k ti p tj b0 nh7. •

Thao tác gi/i mã – th0c hi n l nh:

Mã l nh tj thanh ghi IR ñưPc ñưa vào ñơn v" giNi mã l nh và ñi]u khi n.

ðơn v" giNi mã l nh và ñi]u khi n sk th1c hi n giNi mã opcode và t(o ra các tín hi u ñ

ñi]u khi n vi c xuct nhQp d li u gi a ALU và các thanh ghi (Registers).

Căn c\ trên các tín hi u ñi]u khi n này, ALU th1c hi n các thao tác ñã ñưPc xác ñ"nh.

M0t chuoi các l nh (Opcode) k t hPp l(i v7i nhau ñ th1c hi n m0t công vi c có ý nghĩa ñưPc

gei là chương trình (Program) hay phVn m]m (Software). IV. B NH BÁN D=N:

B0 nh7 bán ddn là m0t b0 phQn khác rct quan treng c a h vi x lý, các chương trình và d li u

ñ]u ñưPc lưu gi trong b0 nh7.

B0 nh7 bán ddn trong h vi x lý gYm: •

ROM: b0 nh7 chương trình → lưu gi chương trình ñi]u khi n ho(t ñ0ng c a toàn h th/ng. •

RAM: b0 nh7 d li u → lưu gi d li u, m0t phVn chương trình ñi]u khi n h th/ng, các

\ng dXng và k t quN tính toán. "

Chương 1: Gi i thi u chung v b vi x lý.

Trư ng ðH Công nghi p Tp.HCM.

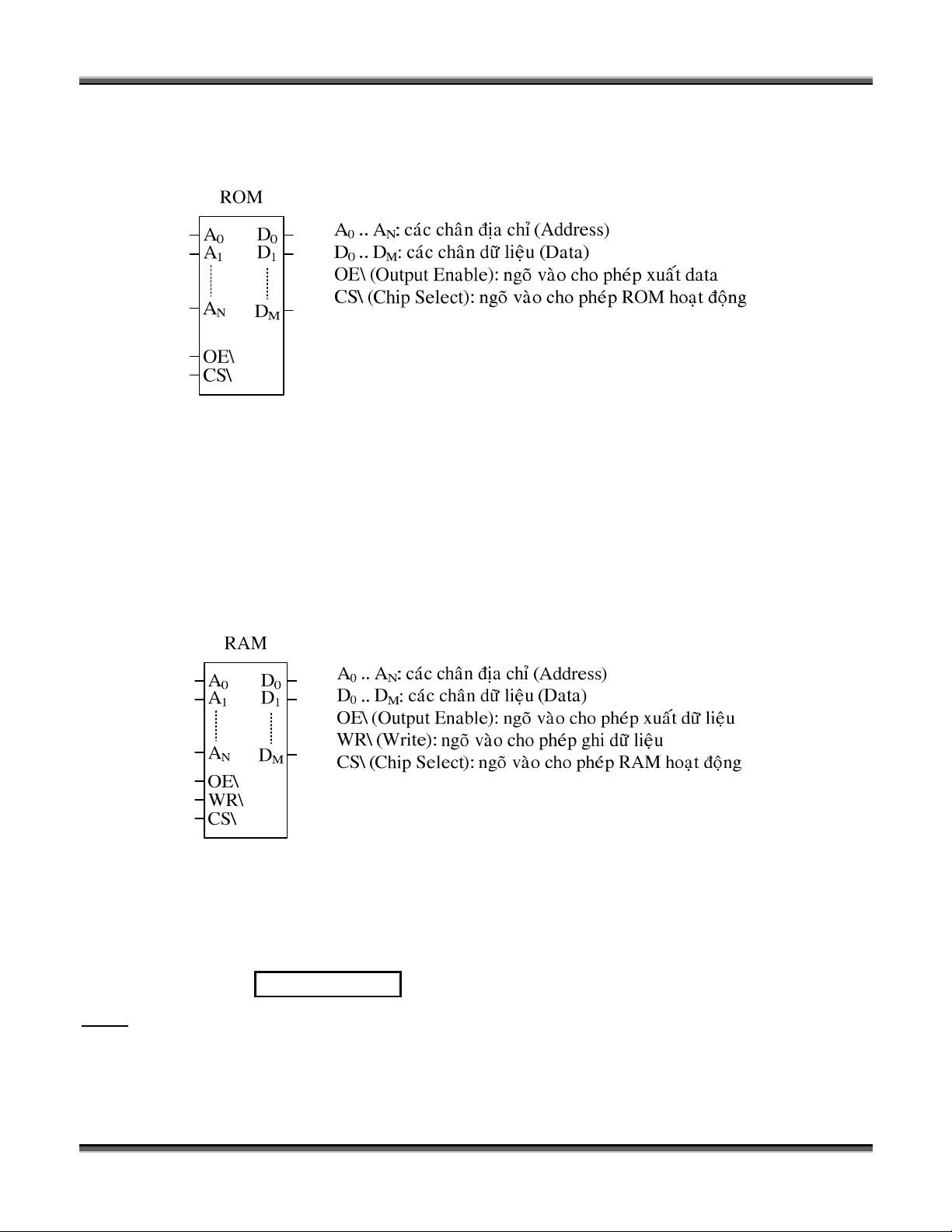

Sơ lưPc v] ccu trúc và phân lo(i ROM – RAM: •

ROM (Read Only Memory): b0 nh7 ch# ñec, thông tin trong ROM sk không b" mct ñi ngay

cN khi nguYn ñi n cung ccp cho ROM không còn. Ccu trúc ROM: Phân lo(i m0t s/ lo(i ROM: MROM (Mask ROM): ROM m t n(.

PROM (Programmable ROM): ROM lQp trình ñưPc.

EPROM (Eraseable PROM): ROM lQp trình và xóa ñưPc.

UVDEPROM (Ultra Violet EPROM): ROM xóa bsng tia c1c tím.

EEPROM (Electric EPROM): ROM lQp trình và xóa bsng tín hi u ñi n.

Flash ROM: ROM lQp trình và xóa bsng tín hi u ñi n. •

RAM (Random Access Memory): b0 nh7 truy xuct ngdu nhiên (b* nh+ ghi ñ-c), thông tin

trong RAM sk b" mct ñi khi nguYn ñi n cung ccp cho RAM không còn.. Ccu trúc RAM: Phân lo(i m0t s/ lo(i RAM: DRAM (Dynamic RAM): RAM ñ0ng SRAM (Static RAM): RAM tĩnh

Cách xác ñ"nh dung lưPng b0 nh7 bán ddn 8 bit s dXng cho chip vi ñi]u khi n 8051 như sau: •

D1a vào s/ lưPng chân ñ"a ch#:

Dung lư?ng = 2N , v7i N là s/ ñưWng ñ"a ch# c a b0 nh7.

Ví d0: B0 nh7 bán ddn 8 bit có 10 ñưWng ñ"a ch#. Cho bi t dung lưPng c a b0 nh7 là bao nhiêu?

N = 10 → Dung lưPng = 210 = 1024 = 1 KB #

Chương 1: Gi i thi u chung v b vi x lý.

Trư ng ðH Công nghi p Tp.HCM. • D1a vào mã s/ c a b0 nh7: Mã s/: XX YYYY XX: lo(i b0 nh7 27: UVDEPROM 28: EEPROM 61,62: SRAM 40,41: DRAM YYYY: dung lưPng b0 nh7

Dung lư?ng = YYYY (Kbit) ho c Dung lư?ng = YYYY / 8 (KB)

Ví d0: B0 nh7 có mã s/ 27256, dung lưPng c a b0 nh7 là bao nhiêu ? 27 → B0 nh7 UVFEPROM

256 → Dung lưPng = 256 (Kbit) = 32 (KB)

V. CÁC THIKT B- NGOLI VI (CÁC THIKT B- XUMT NHNP):

M(ch ñi n giao ti p (Interface Circuitry) và các thi t b" xuct nhQp hay thi t b" ngo(i vi

(Peripheral Devices) t(o ra khN năng giao ti p gi a h vi x lý v7i th gi7i bên ngoài. B0 phQn giao

ti p gi a bus h th/ng c a h vi x lý v7i các th gi7i bên ngoài thưWng ñưPc gei là cZng (Port). Như

vQy tùy theo tjng lo(i thi t b" giao ti p mà ta có các cZng nhQp (Input) ñ lcy thông tin tj ngoài vào h

và các cZng xuct (Output) ñ ñưa thông tin tj trong h ra ngoài.

TZng quát, ta có 3 lo(i thi t b" xuct nhQp sau: •

Thi t b" lưu tr l7n: băng tj, ñĩa tj, ñĩa quang, … •

Thi t b" giao ti p v7i con ngưWi: màn hình, bàn phím, máy in, … •

Thi t b" ñi]u khi n / ki m tra: các b0 kích thích, các b0 cNm bi n, … VI. H TH+NG BUS:

Bus là tQp hPp các ñưWng dây mang thông tin có cùng ch\c năng. Vi c truy xuct thông tin t7i

m0t m(ch ñi n xung quanh CPU thì nó s dXng 3 lo(i bus: bus ñ"a ch#, bus d li u và bus ñi]u khi n.

CPU s dXng h th/ng bus này ñ th1c hi n các thao tác ñec (READ) và ghi (WRITE) thông tin gi a

CPU v7i b0 nh7 ho c các thi t b" ngo(i vi. • Bus ñ"a ch# (Address bus):

ð chuy n tNi thông tin c a các bit ñ"a ch#.

Là lo(i bus 1 chi]u (CPU → MEM hay I/O).

ð xác ñ"nh b0 nh7 ho c thi t b" ngo(i vi mà CPU cVn trao ñZi thông tin.

ð xác ñ"nh dung lưPng b0 nh7 ho c ngo(i vi mà CPU có khN năng truy xuct. • Bus d li u (Data bus):

ð chuy n tNi thông tin c a các bit d li u.

Là lo(i bus 2 chi]u (CPU ↔ MEM hay I/O).

ð xác ñ"nh s/ bit d li u mà CPU có khN năng x lý cùng m0t lúc. • Bus ñi]u khi n (Control bus):

ð chuy n tNi thông tin c a các bit ñi]u khi n (moi ñưWng dây là m0t tín hi u ñi]u khi n khác nhau).

Là lo(i bus 1 chi]u (CPU → MEM5I/O ho6c MEM5I/O → CPU).

ð ñi]u khi n các kh/i khác trong h và nhQn tín hi u ñi]u khi n tj các kh/i ñó ñ ph/i hPp ho(t ñ0ng. $

Chương 1: Gi i thi u chung v b vi x lý.

Trư ng ðH Công nghi p Tp.HCM.

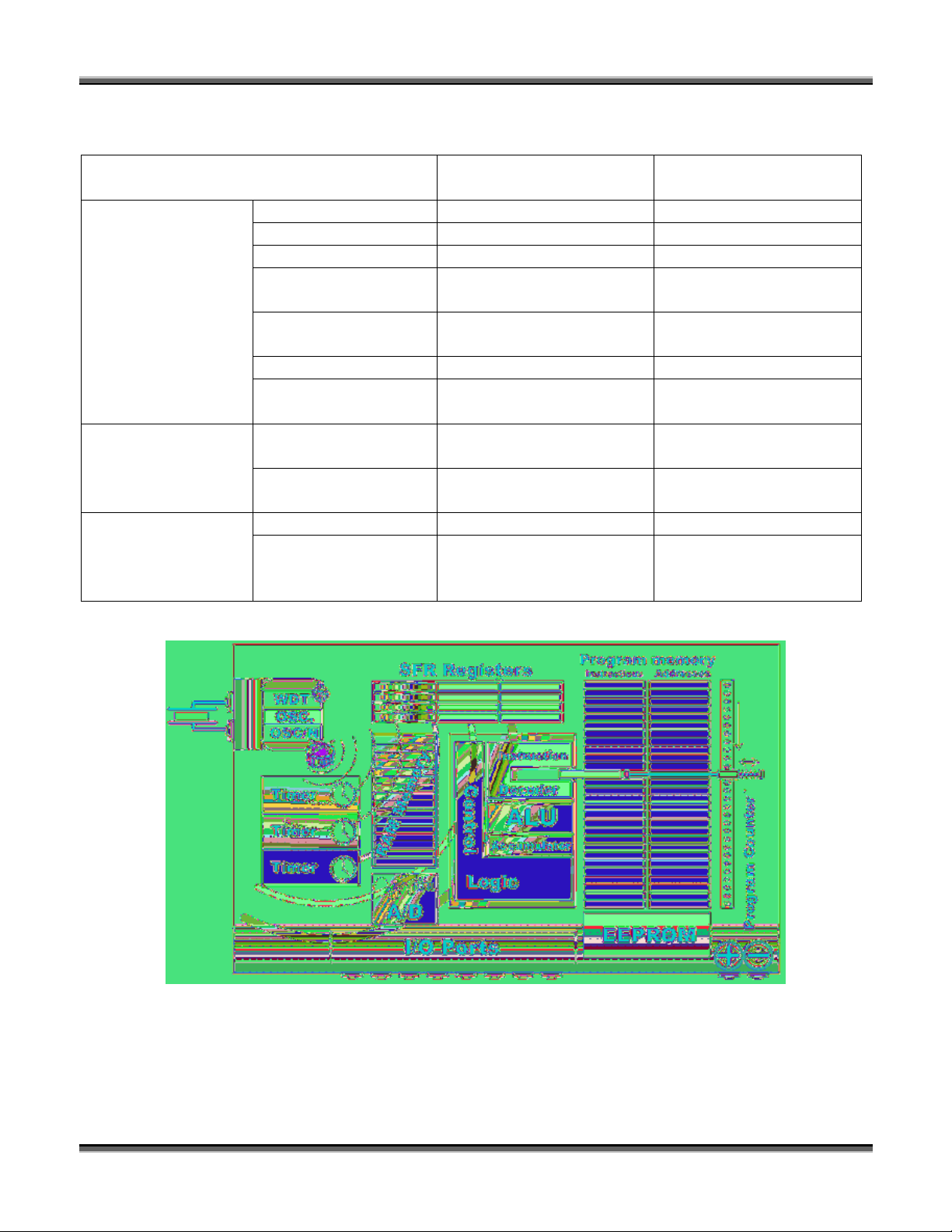

VII. VI X LÝ – VI ðI U KHI N:

ð phân bi t b0 vi x lý và b0 vi ñi]u khi n ta có th d1a trên các y u t/ như sau: Vi xU lý Vi ñiXu khiZn Y!u tP phân loSi (Microprocessor) (Microcontroller) CPU X X ROM X RAM X M(ch giao ti p n/i Ccu trúc phVn c\ng X ti p (Hardware M(ch giao ti p song architecture) X song M(ch ñi]u khi n ngyt X Các m(ch ñi]u khi n X khác zng dXng l7n, tính X Các \ngdXng toán ph\c t(p (Applications) zng dXng nhm, tính X toán ñơn giNn Các ñ c trưng c a Các ki u ñ"nh ñ"a ch# Nhi]u Ít tQp l nh (Instruction set ð0 dài tj d li u x Byte, Word, Double word, Bit, Byte lý … feature)

VIII. MINH H[A KIKN TRÚC C A M T H VI ðI U KHI N:

WDT (Watch5Dog Timer): B0 ñ"nh thWi WatchDDog.

OSC., OSC/N (Oscillator): B0 dao ñ0ng (N: h s/ chia tVn). Timer: B0 ñ"nh thWi.

A/D (Analog/Digital): B0 bi n ñZi tín hi u tương t1/s/.

SFR Registers (Special Function Register): Các thanh ghi ch\c năng ñ c bi t. RAM Memory: B0 nh7 d li u. %

Chương 1: Gi i thi u chung v b vi x lý.

Trư ng ðH Công nghi p Tp.HCM.

Program Memory: B0 nh7 chương trình. EEPROM: B0 nh7 EEPROM.

I/O Ports: Các port xuct/nhQp.

Instruction Decoder: B0 giNi mã l nh.

ALU: ðơn v" logic và s/ hec.

Accumulator: Thanh ghi tích lũy.

Control Logic: ði]u khi n logic.

Program Counter: B0 ñ m chương trình.

Instructions/Addresses: Các l nh / ñ"a ch#.

IX. L A CH[N B VI ðI U KHI N KHI THIKT KK:

Có b/n he vi ñi]u khi n thông dXng trên th" trưWng hi n nay là: 68xxx c a Motorola, 80xxx c a

Intel, Z8xx c a Zilog và PIC16xxx c a Microchip Technology. Moi lo(i vi ñi]u khi n trên ñ]u có m0t

tQp l nh và thanh ghi riêng nên chúng không tương thích ldn nhau. VQy khi ta ti n hành thi t k m0t h

th/ng s dXng vi ñi]u khi n thì ta cVn d1a trên nh ng tiêu chunn nào? Có ba tiêu chnn chính: •

Tiêu chu@n thA nhBt là: ðáp \ng yêu cVu tính toán m0t cách hi u quN và kinh t . Do vQy,

trư7c tiên ta cVn phNi xem xét b0 vi ñi]u khi n 8 bit, 16 bit hay 32 bit là thích hPp nhct. M0t s/ tham s/

k€ thuQt cVn ñưPc cân nhyc khi chen l1a là:

TDc ñ : t/c ñ0 l7n nhct mà vi ñi]u khi n ho trP là bao nhiêu.

KiFu IC: là ki u 40 chân DIP, QFP hay là ki u ñóng vm khác (DIP: v8 d9ng hai hàng

chân, QFP: v8 vuông d?t). Ki u ñóng vm rct quan treng khi có yêu cVu v] không gian, ki u lyp ráp và

t(o mdu th cho sNn phnm cu/i cùng.

Công suBt tiêu thG: là m0t tiêu chunn cVn ñ c bi t lưu ý n u sNn phnm dùng pin ho c ñi n áp lư7i.

Dung lưPng b0 nh7 ROM và RAM tích hPp s‚n trên chip.

S/ chân vào/ra và b0 ñ"nh thWi trên chip.

KhN năng dƒ dàng nâng cao hi u suct ho c giãm công suct tiêu thX.

Giá thành trên m0t ñơn v" khi mua s/ lưPng l7n. Vì ñây là vcn ñ] có Nnh hư…ng ñ n giá

thành cu/i cùng c a sNn phnm. •

Tiêu chu@n thA hai là: Có s‚n các công cX phát tri n phVn m]m, ch†ng h(n như các chương

trình mô phmng, trình biên d"ch, trình hPp d"ch và g‡ r/i. •

Tiêu chu@n thA ba là: KhN năng ñáp \ng v] s/ lưPng … hi n t(i cũng như … tương lai. ð/i

v7i m0t s/ nhà thi t k thì tiêu chunn này thQm chí còn quan treng hơn cN hai tiêu chunn trên. &

Chương 2: Ph n c ng chip vi ñi u khi n 8051.

Trư ng ðH Công nghi!p Tp.HCM. CHƯƠNG 2

PH N C NG CHIP VI ðI U KHI N 8051 I. T NG QUÁT: 1. Gi i thi!u chung:

MCS 51 là h vi ñi u khi n c a hãng Intel. Vi m ch t ng quát c a h MCS 51 là chip 8051.

Chip 8051 có m't s) ñ*c trưng cơ b/n sau:

B' nh2 chương trình bên trong: 4 KB (ROM).

B' nh2 d; liB' nh2 chương trình bên ngoài: 64 KB (ROM).

B' nh2 d; li4 port xuAt nhBp (I/O port) 8 bit. 2 b' ñCnh thDi 16 bit. M ch giao tiEp n)i tiEp.

B' xF lý bit (thao tác trên các bit riêng l ).

210 vC trí nh2 ñưIc ñCnh ñCa chJ, mLi vC trí 1 bit. Nhân / Chia trong 4 Ps.

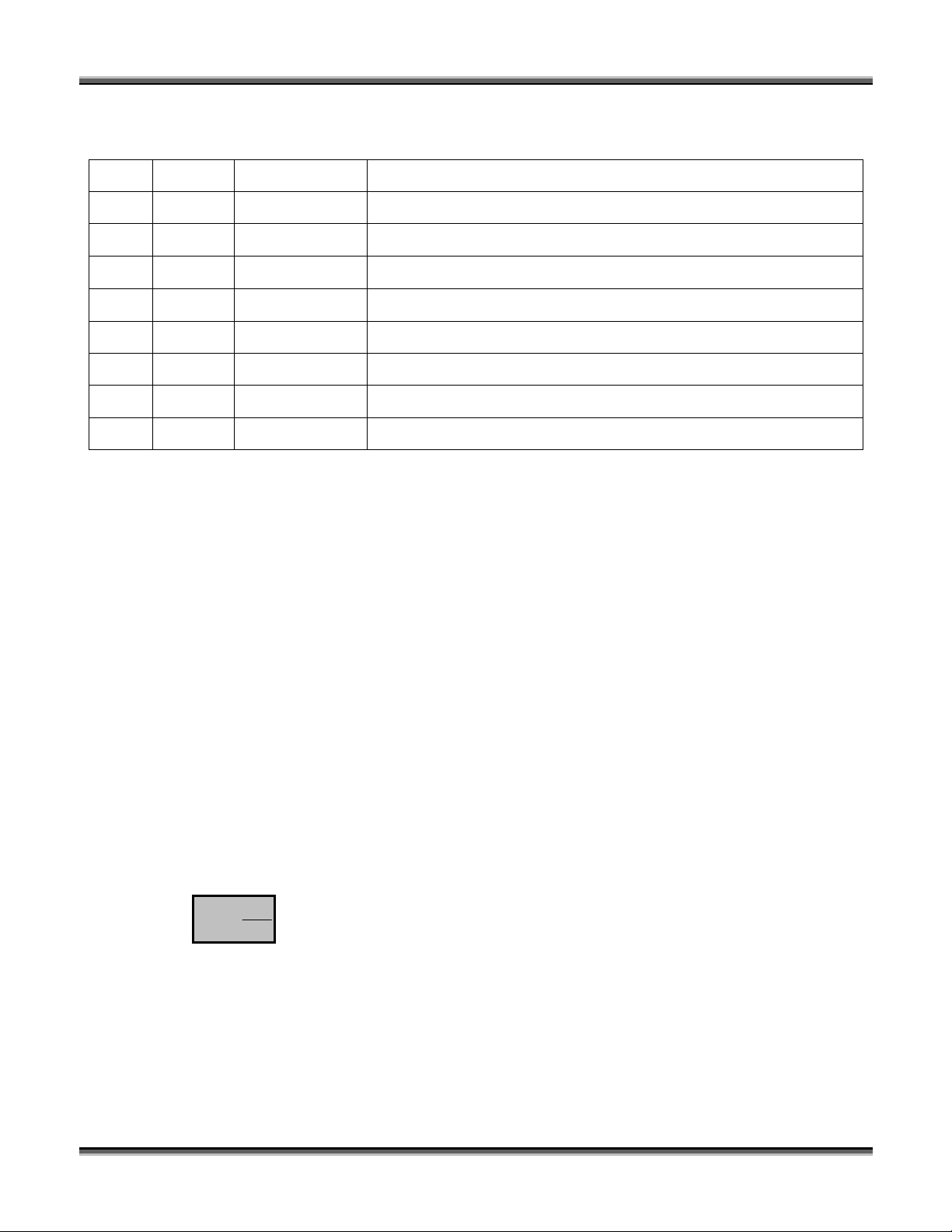

Ngoài ra, trong h MCS 51 còn có m't s) chip vi ñi u khi n khác có cAu trúc tương ñương như: Chip ROM trong RAM trong B. ñ0nh th1i 8031 0 KB 128 byte 2 8032 0 KB 256 byte 3 8051 4 KB PROM 128 byte 2 8052 8 KB PROM 256 byte 3 8751 4 KB UV EPROM 128 byte 2 8752 8 KB UV EPROM 256 byte 3 8951 4 KB FLASH ROM 128 byte 2 8952 8 KB FLASH ROM 256 byte 3

2. Các phiên b5n c6a chip vi ñi9u khi;n 8051: 2.1 B. vi ñi9u khi;n 8031:

8031 là m't phiên b/n khác c a h 8051. Chip này thưDng ñưIc coi là 8051 không có ROM trên

chip. ð có th dùng ñưIc chip này cbn ph/i b sung thêm ROM ngoài chca chương trình cbn thiEt cho

8031. 8051 có chương trình ñưIc chca d ROM trên chip bC gi2i h n ñEn 4KB, còn ROM ngoài c a

8031 thì có th lên ñEn 64KB. Tuy nhiên, ñ có th truy cBp hEt b' nh2 ROM ngoài thì cbn dùng thêm

hai c ng (Port 0 và Port 2) , do vBy chJ còn l i có hai c ng (Port 1 và Port 3) ñ sF dfng. Nhgm khhc

phfc vAn ñ này, chúng ta có th b sung thêm c ng vào/ra cho 8031. 2.2 B. vi ñi9u khi;n 8052:

8052 là m't phiên b/n c a h 8051. 8052 có tAt c/ các thông s) ki thuBt c a 8051, ngoài ra còn

có thêm 128 byte RAM, 4KB ROM và m't b' ñCnh thDi n;a. Như vBy, 8052 có t ng c'ng 256 byte

RAM, 8KB ROM và ba b' ñCnh thDi. Giáo trình Vi x* lý. 8 Biên so0n: Ph0m Quang Trí

Chương 2: Ph n c ng chip vi ñi u khi n 8051.

Trư ng ðH Công nghi!p Tp.HCM. ð=c tính k? thu@t 8031 8051 8052 ROM trên chip (KB) 0 4 8 RAM trên chip (byte) 128 128 256 B$ ñ&nh th'i 2 2 3 Chân vào/ra 32 32 32 C*ng n+i ti,p 1 1 1 Ngu/n ng0t 5 5 6

Như b/ng thông s) trên ta thAy 8051 là m't trưDng hIp riêng c a 8052. M i chương trình viEt

cho 8051 ñ u có th ch y ñưIc trên 8052 nhưng ñi u ngưIc l i có th là không ñúng. 2.3 B. vi ñi9u khi;n 8751:

Chip 8751 chJ có 4KB b' nh2 UV EPROM trên chip. ð sF dfng chip này cbn ph/i có thiEt bC

lBp trình PROM và thiEt bC xoá UV EPROM. Do ROM trên chip c a 8751 là UV EPROM, nên cbn

ph/i mAt kho/ng 20 phút ñ xoá 8751 trư2c khi ñưIc lBp trình. Vì ñây là quá trình mAt nhi u thDi gian

nên nhi u nhà s/n xuAt ñã cho ra phiên b/n Flash ROM và UV RAM. 2.4

B. vi ñi9u khi;n AT8951 c6a Atmel Corporation:

AT8951 là phiên b/n 8051 có ROM trên chip là b' nh2 Flash. Phiên b/n này rAt thích hIp cho

các cng dfng nhanh vì b' nh2 Flash có th ñưIc xóa trong vài giây. Dĩ nhiên là ñ dùng AT8951 cbn

ph/i có thiEt bC lBp trình PROM hL trI b' nh2 Flash nhưng không cbn ñEn thiEt bC xóa ROM vì b' nh2

Flash ñưIc xóa bgng thiEt bC lBp trình PROM. ð tim't phiên b/n c a AT8951 có th ñưIc lBp trình qua c ng COM c a máy tính PC và như vBy sl không

cbn ñEn thiEt bC lBp trình PROM. Ký hi!u ROM RAM I/O Timer NgIt Vcc SK chân IC AT89C51 4KB 128 32 2 5 5V 40 AT89LV51 4KB 128 32 2 5 3V 40 AT89C1051 1KB 64 15 1 3 3V 20 AT89C2051 2KB 128 15 2 5 3V 20 AT89C52 8KB 256 32 3 6 5V 40 AT89LV52 8KB 256 32 3 6 3V 40 2.5

B. vi ñi9u khi;n DS5000 c6a Dallas Semiconductor:

M't phiên b/n ph biEn khác n;a c a 8051 là DS5000 c a hãng Dallas Semiconductor. B' nh2

ROM trên chip c a DS5000 là NV RAM. DS5000 có kh/ năng n p chương trình vào ROM trên chip

trong khi nó vnn d trong h< th)ng mà không cbn ph/i lAy ra. Cách thoc hiGiáo trình Vi x* lý. 9 Biên so0n: Ph0m Quang Trí

Chương 2: Ph n c ng chip vi ñi u khi n 8051.

Trư ng ðH Công nghi!p Tp.HCM.

c a máy tính PC. ðây là m't ñi m m nh rAt ñưIc ưa chu'ng. Ngoài ra, NV RAM còn có ưu viphép thay ñ i n'i dung RAM theo tqng byte mà không cbn ph/i xóa hEt trư2c khi lBp trình như b' nh2 EPROM. Ký hi!u ROM RAM I/O Timer NgIt Vcc SK chân IC DS500098 8KB 128 32 2 6 5V 40 DS5000932 32KB 128 32 2 6 5V 40 DS5000T98 8KB 128 32 2 6 5V 40 DS5000T932 32KB 128 32 2 6 5V 40

ði m ñ*c bithêm m't ñtng ht thDi gian thoc (RTC: Real Time Clock) bên trong. Lưu ý ñtng ht thDi gian thoc RTC

hoàn toàn khác v2i b' ñCnh thDi Timer. RTC t o và lưu gi; thDi gian c a ngày (gi'/phút/giây) và ngày

tháng (ngày/tháng/năm) trên thoc tE ngay c/ khi không có ngutn cung cAp. 2.6

B. vi ñi9u khi;n P89V51xx c6a Philips Corporation:

ðây là m't phiên b/n c/i tiEn sF dfng CPU là b' vi ñi u khi n 80C51 v2i nhi u tính năng vưIt

tr'i: dung lưIng ROM/RAM trên chip rAt l2n, 3 Timer 16 bit + 1 Watch dog Timer, 2 thanh ghi DPTR,

8 ngutn nght, PWM (Pulse Width Modulator), SPI (Serial Peripheral Interface) và ñ*c bichương trình trên chip có tính năng ISP (In9System Programming) và IAP (In9Application Programming),… II. CÁC CHÂN CSA CHIP 8051:

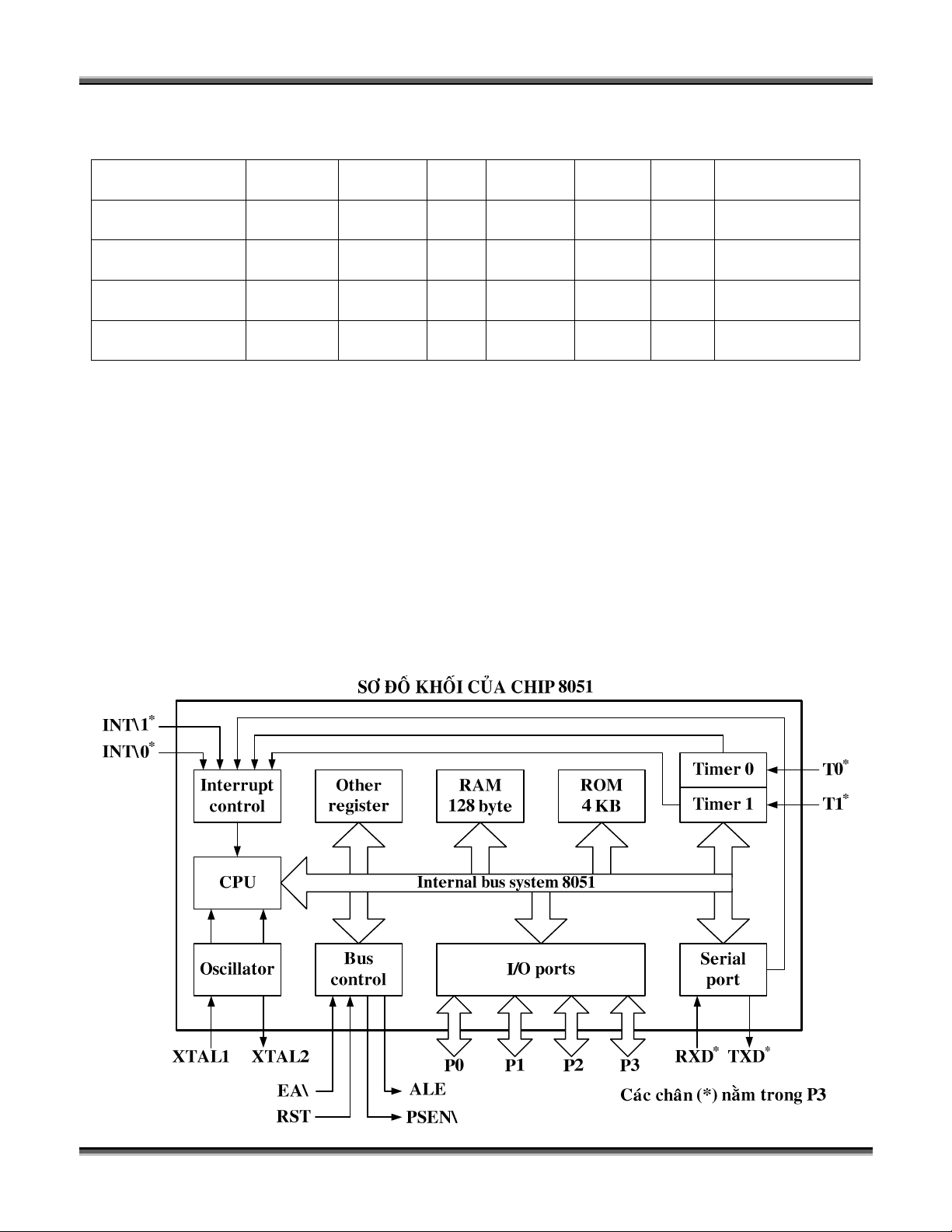

1. Sơ ñU khKi và chWc năng các khKi c6a chip 8051: Giáo trình Vi x* lý. 10 Biên so0n: Ph0m Quang Trí

Chương 2: Ph n c ng chip vi ñi u khi n 8051.

Trư ng ðH Công nghi!p Tp.HCM.

CPU (Central Processing Unit): ðơn vC xF lý trung tâm → tính toán và ñi u khi n quá

trình ho t ñ'ng c a h< th)ng.

OSC (Oscillator): M ch dao ñ'ng → t o tín hichip ho t ñ'ng.

Interrupt control: ði u khi n nght → nhBn tín hib' ñCnh thDi (Timer 0, Timer 1) và tq c ng n)i tiEp (Serial port), lbn lưIt ñưa các tín hiCPU ñ xF lý.

Other registers: Các thanh ghi khác → lưu tr; d; lilàm viRAM (Random Access Memory): B' nh2 d; liROM (Read Only Memory): B' nh2 chương trình trong chip → lưu tr; chương trình ho t ñ'ng c a chip.

I/O ports (In/Out ports): Các port xuAt/nhBp → ñi u khi n vid ng song song gi;a trong và ngoài chip thông qua các port P0, P1, P2, P3.

Serial port: Port n)i tiEp → ñi u khi n vitrong và ngoài chip thông qua các chân TxD, RxD.

Timer 0, Timer 1: B' ñCnh thDi 0, 1 → dùng ñ ñCnh thDi gian ho*c ñEm so kixung) thông qua các chân T0, T1.

Bus control: ði u khi n bus → ñi u khi n ho t ñ'ng c a h< th)ng bus và vithông tin trên h< th)ng bus.

Bus system: H< th)ng bus → liên kEt các kh)i trong chip l i v2i nhau.

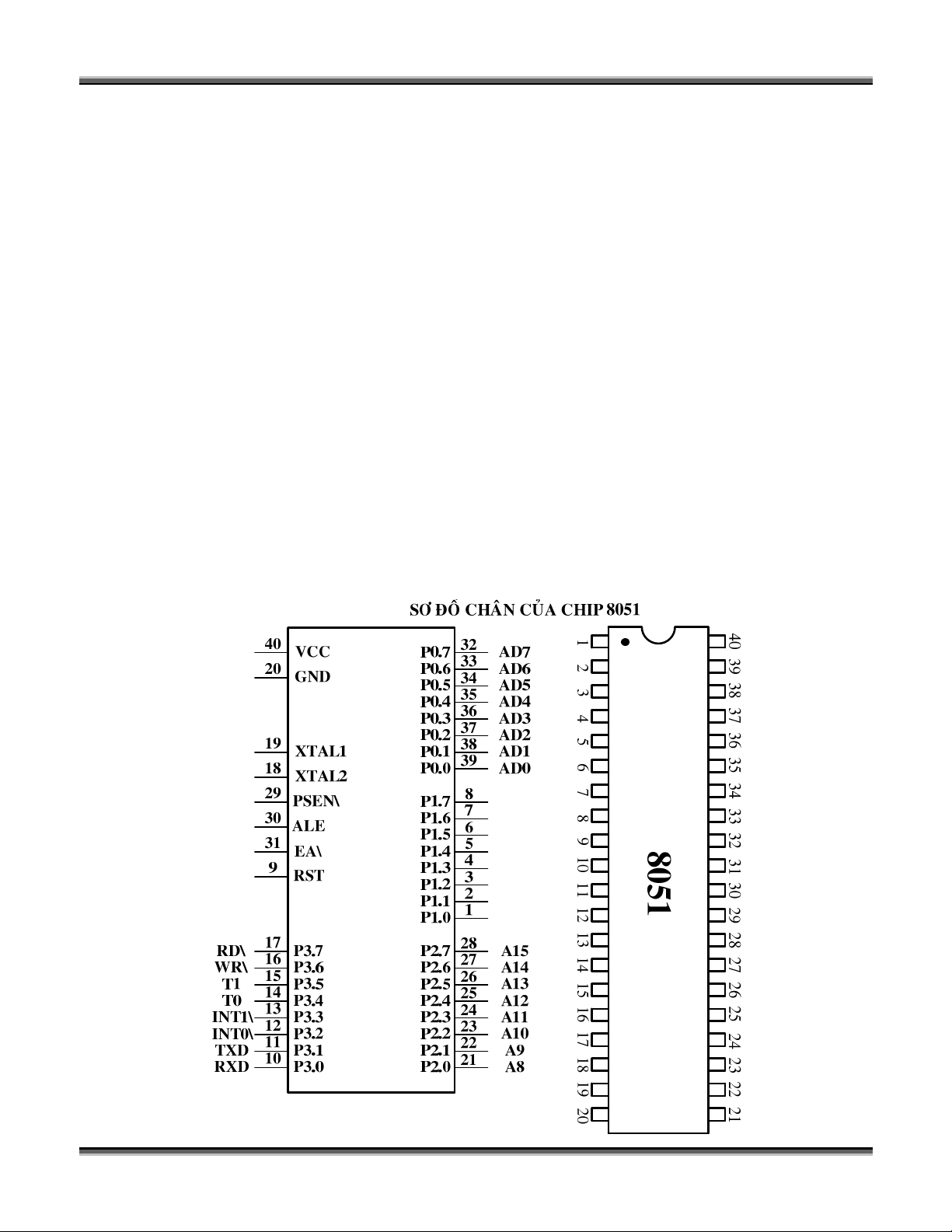

2. Sơ ñU chân và chWc năng các chân c6a chip 8051: Giáo trình Vi x* lý. 11 Biên so0n: Ph0m Quang Trí

Chương 2: Ph n c ng chip vi ñi u khi n 8051.

Trư ng ðH Công nghi!p Tp.HCM. 2.1. Port 0:

Port 0 (P0.0 – P0.7) có s) chân tq 32 – 39. Port 0 có hai chcc năng: • Port xuAt nhBp d; li•

Bus ñCa chJ byte thAp và bus d; lingoài.

Lưu ý: Khi Port 0 ñóng vai trò là port xuDt nhEp dF li!u thì phGi s* dHng các ñi!n trI kéo lên bên ngoài.

y chE ñ' m*c ñCnh (khi reset) thì các chân Port 0 (P0.0 9 P0.7) ñưIc cAu hình là port xuDt

d; licao (mIc 1) ñEn tAt c/ các bit c a port trư2c khi bht ñbu nhBp d; libày O phPn k, ti,p).

Khi lBp trình cho ROM trong chip thì Port 0 ñóng vai trò là ngõ vào c a d; li(xem sách “HS vi ñiKu khiTn 8051” trang 3339352). 2.2. Port 1:

Port 1 (P1.0 – P1.7) có s) chân tq 1 – 8. Port 1 có m't chcc năng: • Port xuAt nhBp d; lingoài.

y chE ñ' m*c ñCnh (khi reset) thì các chân Port 1 (P1.0 – P1.7) ñưIc cAu hình là port xuDt

d; licao (mIc 1) ñEn tAt c/ các bit c a port trư2c khi bht ñbu nhBp d; libày O phPn k, ti,p).

Khi lBp trình cho ROM trong chip thì Port 1 ñóng vai trò là ngõ vào c a ñCa chJ byte thAp

(A0 – A7) (xem sách “HS vi ñiKu khiTn 8051” trang 3339352). 2.3. Port 2:

Port 2 (P2.0 – P2.7) có s) chân tq 21 – 28. Port 2 có hai chcc năng: • Port xuAt nhBp d; li•

Bus ñCa chJ byte cao (A8 – A15) → có sF dfng b' nh2 ngoài.

y chE ñ' m*c ñCnh (khi reset) thì các chân Port 2 (P2.0 – P2.7) ñưIc cAu hình là port xuDt

d; licao (mIc 1) ñEn tAt c/ các bit c a port trư2c khi bht ñbu nhBp d; libày O phPn k, ti,p).

Khi lBp trình cho ROM trong chip thì Port 2 ñóng vai trò là ngõ vào c a ñCa chJ byte cao (A8 – A11) và các tín hi2.4. Port 3:

Port 3 (P3.0 – P3.7) có s) chân tq 10 – 17. Port 3 có hai chcc năng: •

Port xuAt nhBp d; lichcc năng ñ*c bi•

Các tín hiy chE ñ' m*c ñCnh (khi reset) thì các chân Port 3 (P3.0 – P3.7) ñưIc cAu hình là port xuDt

d; licao (mIc 1) ñEn tAt c/ các bit c a port trư2c khi bht ñbu nhBp d; libày O phPn k, ti,p). Giáo trình Vi x* lý. 12 Biên so0n: Ph0m Quang Trí

Chương 2: Ph n c ng chip vi ñi u khi n 8051.

Trư ng ðH Công nghi!p Tp.HCM.

Khi lBp trình cho ROM trong chip thì Port 3 ñóng vai trò là ngõ vào c a các tín hikhi n (xem sách “HS vi ñiKu khiTn 8051” trang 3339352).

Chcc năng c a các chân Port 3: Bit Tên ðCa chJ bit Chcc năng P3.0 RxD B0H Chân nhBn d; liP3.1 TxD B1H Chân phát d; liP3.2 INT0\ B2H Ngõ vào nght ngoài 0. P3.3 INT1\ B3H Ngõ vào nght ngoài 1. P3.4 T0 B4H

Ngõ vào c a b' ñCnh thDi/ñEm 0. P3.5 T1 B5H

Ngõ vào c a b' ñCnh thDi/ñEm 1. P3.6 WR\ B6H

ði u khi n ghi vào RAM ngoài. P3.7 RD\ B7H

ði u khi n ñ c tq RAM ngoài. 2.5. Chân PSEN\:

PSEN (Program Store Enable): cho phép b' nh2 chương trình, chân s) 29. Chcc năng: • Là tín hi•

Là tín hiPSEN\ = 0 → trong thDi gian CPU tìm n p lPSEN\ = 1 → CPU sF dfng ROM trong (không sW dXng ROM ngoài).

Khi sF dfng b' nh2 chương trình bên ngoài, chân PSEN\ thưDng ñưIc n)i v2i chân OE\ c a

ROM ngoài ñ cho phép CPU ñ c mã l2.6. Chân ALE:

ALE (Address Latch Enable): cho phép ch)t ñCa chJ, chân s) 30. Chcc năng: •

Là tín hibyte thAp và bus d; li•

Là tín hiALE = 0 → trong thDi gian bus AD0 AD7 ñóng vai trò là bus D0 D7.

ALE = 1 → trong thDi gian bus AD0 AD7 ñóng vai trò là bus A0 A7.

Khi lBp trình cho ROM trong chip thì chân ALE ñóng vai trò là ngõ vào c a xung lBp trình

(PGM\) (xem sách “HS vi ñiKu khiTn 8051” trang 3339352). Lưu ý: fOSC f

→ có th dùng làm xung clock cho các m ch khác. = ALE 6

fALE (MHz): tbn s) xung t i chân ALE.

fOSC (MHz): tbn s) dao ñ'ng trên chip (tbn s) th ch anh).

Khi l(xem gi\n ñ/ trang 38939 sách “HS vi ñiKu khiTn 8051”). 2.7. Chân EA\:

EA (External Access): truy xuAt ngoài, chân s) 31. Chcc năng: •

Là tín hiGiáo trình Vi x* lý. 13 Biên so0n: Ph0m Quang Trí

Chương 2: Ph n c ng chip vi ñi u khi n 8051.

Trư ng ðH Công nghi!p Tp.HCM. •

Là tín hiEA\ = 0 → Chip 8051 sF dfng chương trình c a ROM ngoài.

EA\ = 1 → Chip 8051 sF dfng chương trình c a ROM trong.

Khi lBp trình cho ROM trong chip thì chân EA ñóng vai trò là ngõ vào c a ñi(Vpp = 12V – 12,5V cho hS 89xx; 21V cho hS 80xx, 87xx) (xem sách “HS vi ñiKu khiTn 8051” trang 3339352).

Lưu ý: Chân EA\ ph/i ñưIc n)i lên Vcc (n,u sW dXng chương trình c`a ROM trong) ho*c n)i

xu)ng GND (n,u sW dXng chương trình c`a ROM ngoài), không bao giD ñưIc phép b~ tr)ng chân này. 2.8. Chân XTAL1, XTAL2:

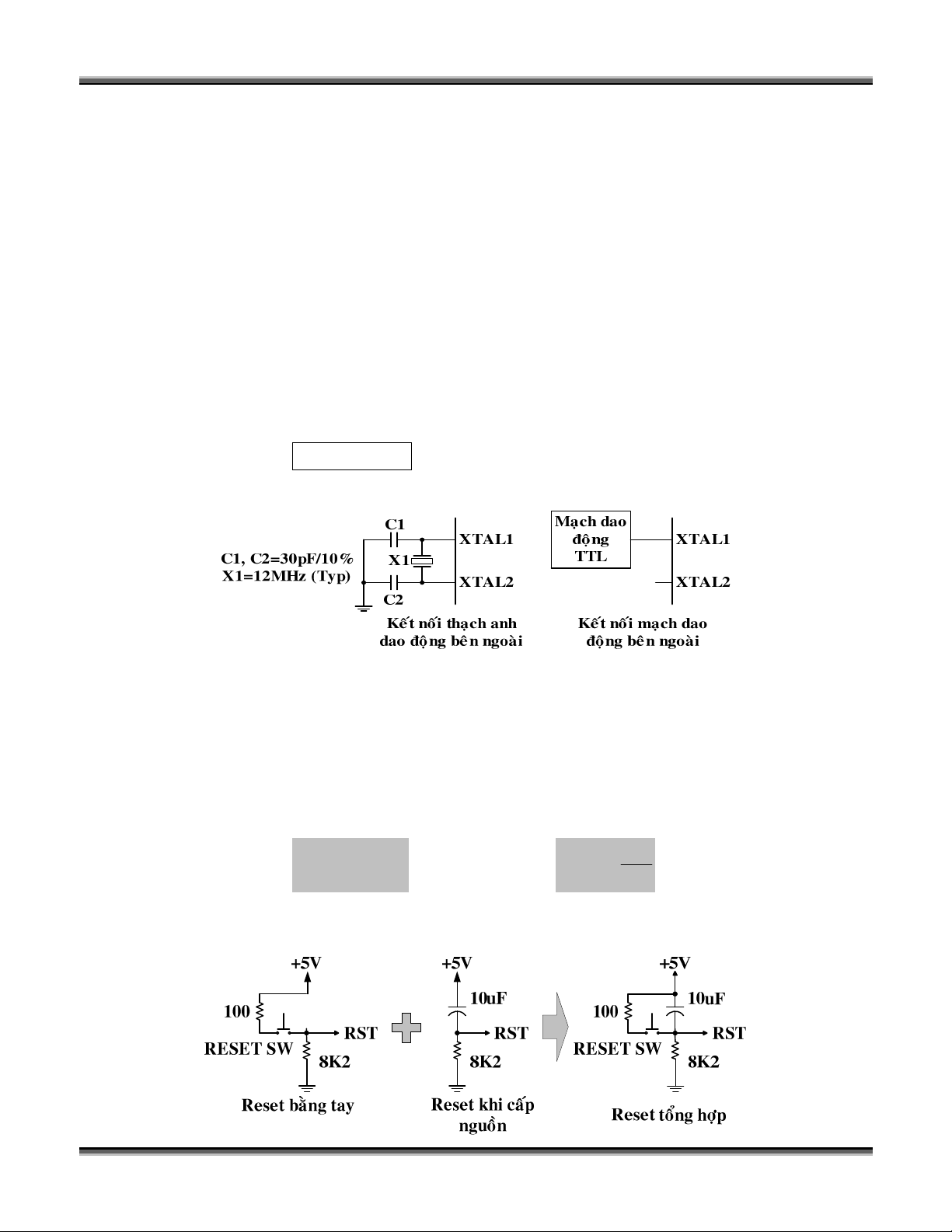

XTAL (Crystal): tinh th th ch anh, chân s) 18 19. Chcc năng: •

Dùng ñ n)i v2i th ch anh ho*c m ch dao ñ'ng t o xung clock bên ngoài, cung cAp tín hi•

XTAL1 → ngõ vào m ch t o xung clock trong chip. •

XTAL2 → ngõ ra m ch t o xung clock trong chip. Lưu ý: f MHz 12 TYP = fTYP (MHz): tbn s) danh ñCnh. 2.9. Chân RST:

RST (Reset): thiEt lBp l i, chân s) 9. Chcc năng: • Là tín hi•

Là tín hiRST = 0 → Chip 8051 ho t ñ'ng bình thưDng.

RST = 1 → Chip 8051 ñưIc thiEt l*p l i tr ng thái ban ñbu. Lưu ý: t 12 ≥ 2 × T Re set Machine T = Machine fOSC tRESET (Ps): thDi gian reset. fOSC (MHz): tbn s) th ch anh. TMACHINE (Ps): chu kỳ máy. Giáo trình Vi x* lý. 14 Biên so0n: Ph0m Quang Trí

Chương 2: Ph n c ng chip vi ñi u khi n 8051.

Trư ng ðH Công nghi!p Tp.HCM.

Ví dX: Xác ñCnh chu kỳ máy và thDi gian reset tương cng cho tqng trưDng hIp fOSC = 11,0592MHz, fOSC = 12MHz và fOSC = 16MHz. Gi\i •

fOSC = 11,0592MHz → TMACHINE = 1,085Ps và tRESET ≥ 2,17Ps. •

fOSC = 12MHz → TMACHINE = 1Ps và tRESET ≥ 2Ps. •

fOSC = 16MHz → TMACHINE = 0,75Ps và tRESET ≥ 1,5Ps 2.10. Chân Vcc, GND:

Vcc, GND: ngutn cAp ñiChcc năng: • Cung cAp ngutn ñi• Vcc = +5V ± 10% và GND = 0V.

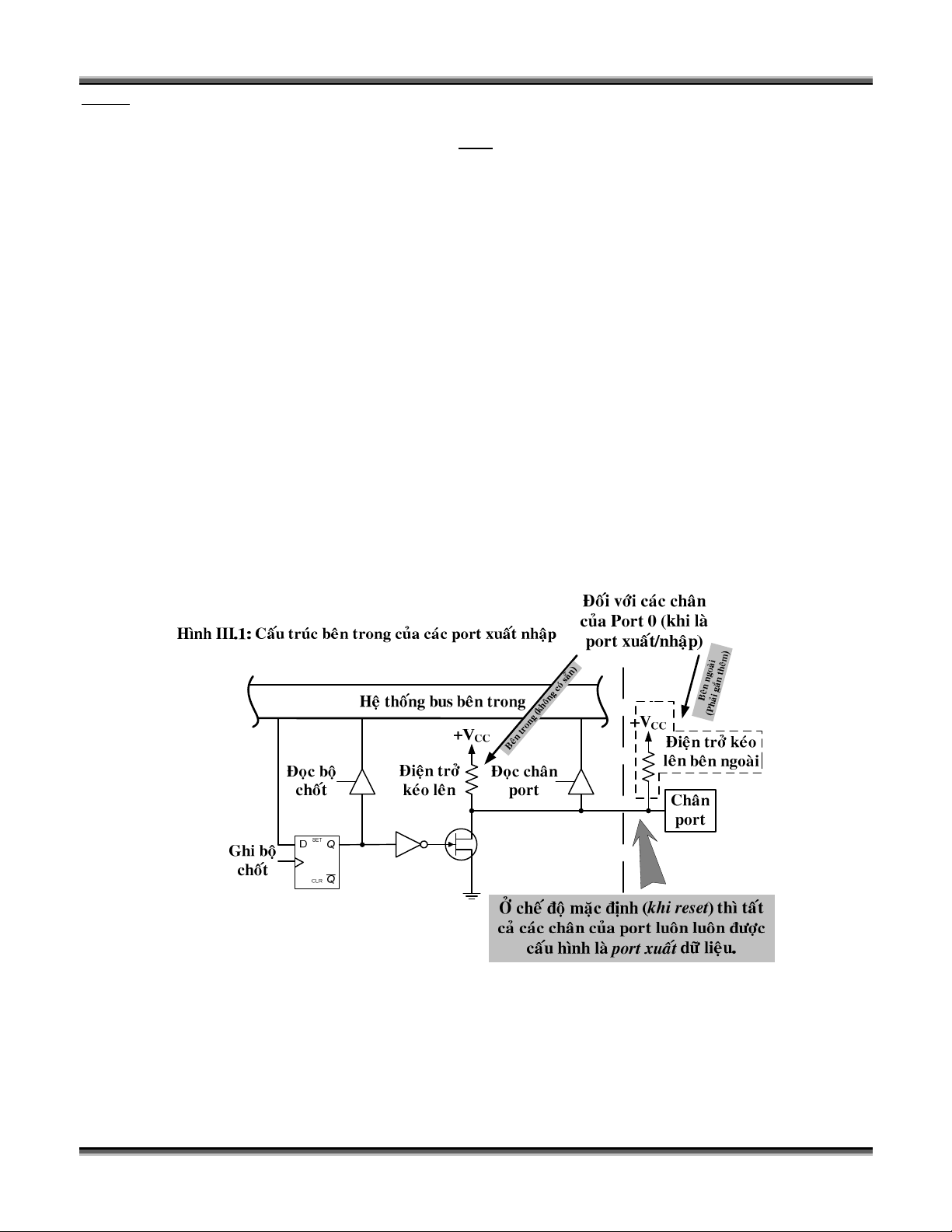

III. CcU TRÚC CÁC PORT XUcT NHeP CHIP 8051:

Kh/ năng fanout (s) lưIng t/i ñbu ra) c a các tqng chân port chip 8051 là: • Port 0: 8 t/i TTL. • Port 1: 4 t/i TTL. • Port 2: 4 t/i TTL. • Port 3: 4 t/i TTL. Lưu ý: •

Khi Port 0 ñóng vai trò là port xuDt nhEp thì sl không có ñiñó ngư i s* dHng c n thêm vào ñi!n trI kéo lên bên ngoài (xem Hình III.1). •

y chE ñ' m*c ñCnh (khi reset) thì tAt c/ các chân c a các port (P0 – P3) ñưIc cAu hình là port xuDt d; li•

Mu)n các chân port c a chip 8015 làm port nhEp d; libgng cách ghi mcc logic cao (mcc 1) ñEn tAt c/ các bit (các chân) c a port trư2c khi bht ñbu nhBp d; liGiáo trình Vi x* lý. 15 Biên so0n: Ph0m Quang Trí

Chương 2: Ph n c ng chip vi ñi u khi n 8051.

Trư ng ðH Công nghi!p Tp.HCM. •

Các chân trong cùng m't port không nhAt thiEt ph/i có cùng ki u cAu hình (port xuJt hoac

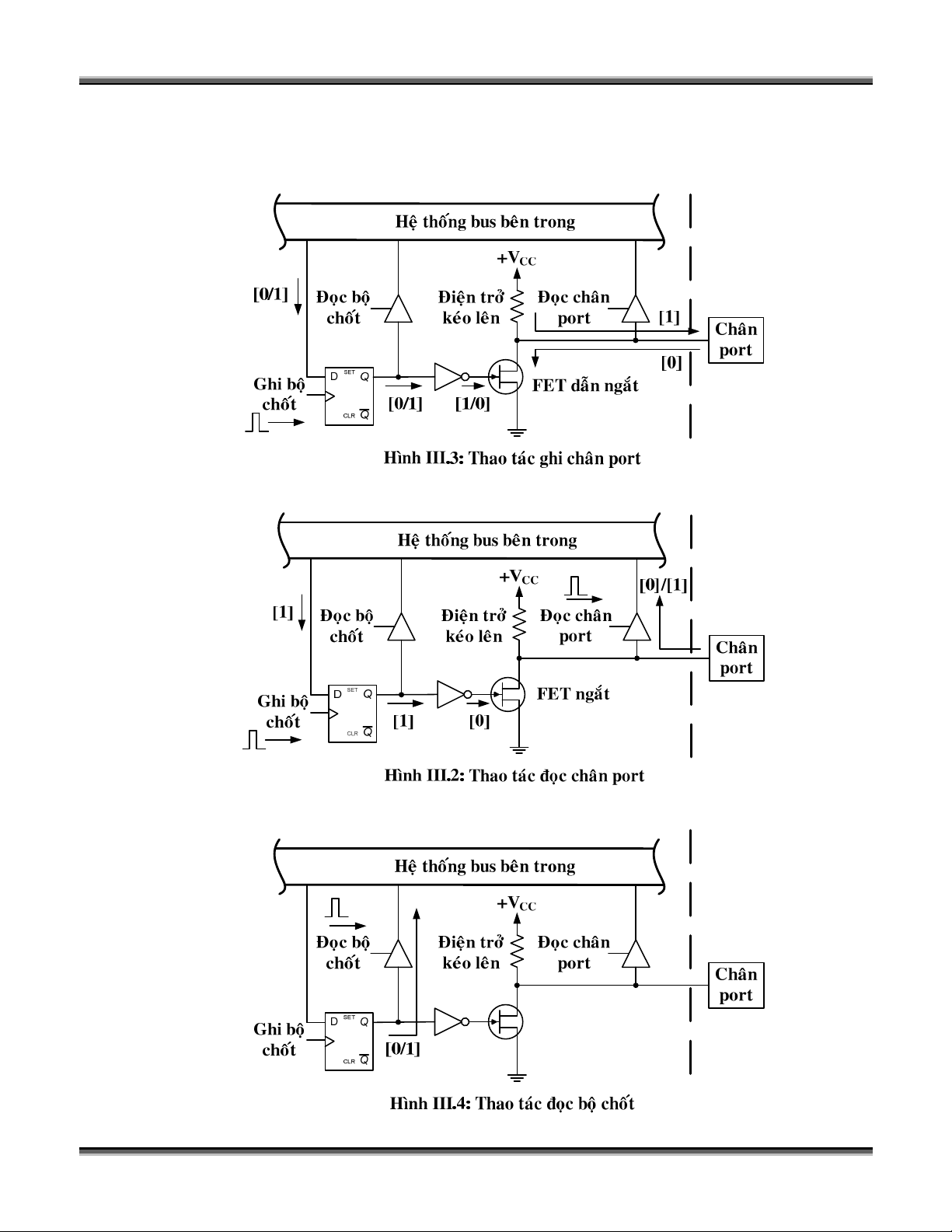

port nhcp). Nghĩa là trong cùng m't port có th có chân dùng ñ nhBp d; lixuAt d; liQuá trình ghi chân port (xuJt dd lieu ra chân port).

Quá trình ñ c chân port (nhcp dd lieu tf chân port).

Quá trình ñ c b' ch)t (kiTm tra dd lieu tgi chân port). Giáo trình Vi x* lý. 16 Biên so0n: Ph0m Quang Trí

Chương 2: Ph n c ng chip vi ñi u khi n 8051.

Trư ng ðH Công nghi!p Tp.HCM.

Lưu ý: Vivào lkhông mong mu)n này là do quá trình ñ c d; litrình ñSc chân port và quá trình ñSc b$ ch+t.

Quá trình ñOc chân port: Khi ta sF dfng các lñưIc sau khi thoc hiQuá trình ñOc bW chXt: Khi ta sF dfng các lDEC, DJNZ, JBC, CLR bit, SETB bit, MOV bit. D; lidF li!u hi!n t0i I các bW chXt (là các dd lieu ñã ñưMc ghi ra port tgi th'i ñiTm trưjc ñó bOi quá trình

ghi chân port), chc không ph/i là d; liquá trình ñ c mà d; liñưIc cBp nhBt.

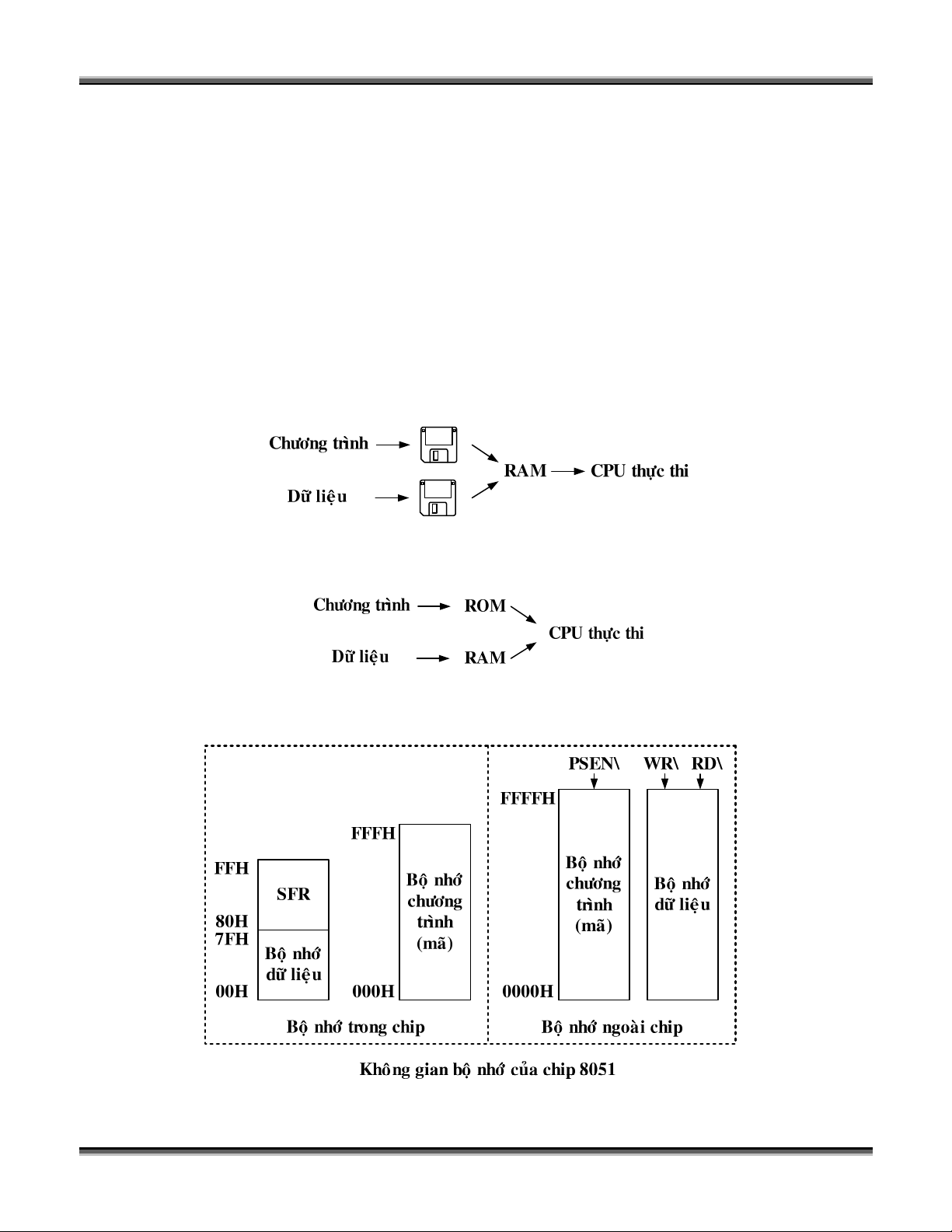

IV. T CH C Bf NHg CSA CHIP 8051:

B' vi xF lý → có không gian b' nh2 chung cho d; li→ chương trình và d; liB' vi ñi u khi n → có không gian b' nh2 riêng cho d; li→ chương trình và d; liT chcc b' nh2 c a chip 8051: Giáo trình Vi x* lý. 17 Biên so0n: Ph0m Quang Trí