Preview text:

ĐỒ ÁN 2 ĐỀ TÀI :

THIẾT KẾ BỘ NHÂN 4BITS DÙNG VERILOG MỤC LỤC

CHƯƠNG I: GIỚI THIỆU TỔNG QUAN VỀ ĐỀ TÀI THIẾT KẾ BỘ NHÂN 4 BIT

1. Giới thiệu đề tài và nguyên lý thiết kế Chip

1.1 Giới thiệu đề tài đồ án 2

Trong việc tính toán trong máy tính, những phép tính cơ bản thường sử dụng đó là

các phép tính cộng ,trừ, nhân, chia...Trong bài báo cáo này ta tìm hiểu và phân tích

về phép nhân 2 số 4 bit từ đó thiết kế mạch nhân 4 bit.

Nhân hai số nhị phân cũng tương tự như trong thập phân,tuy nhiên vì hệ nhị phân chỉ

có hai số 0 và 1 nên việc nhân cũng tương đối đơn giản.

1.2 Nguyên lý thiết kế Chip

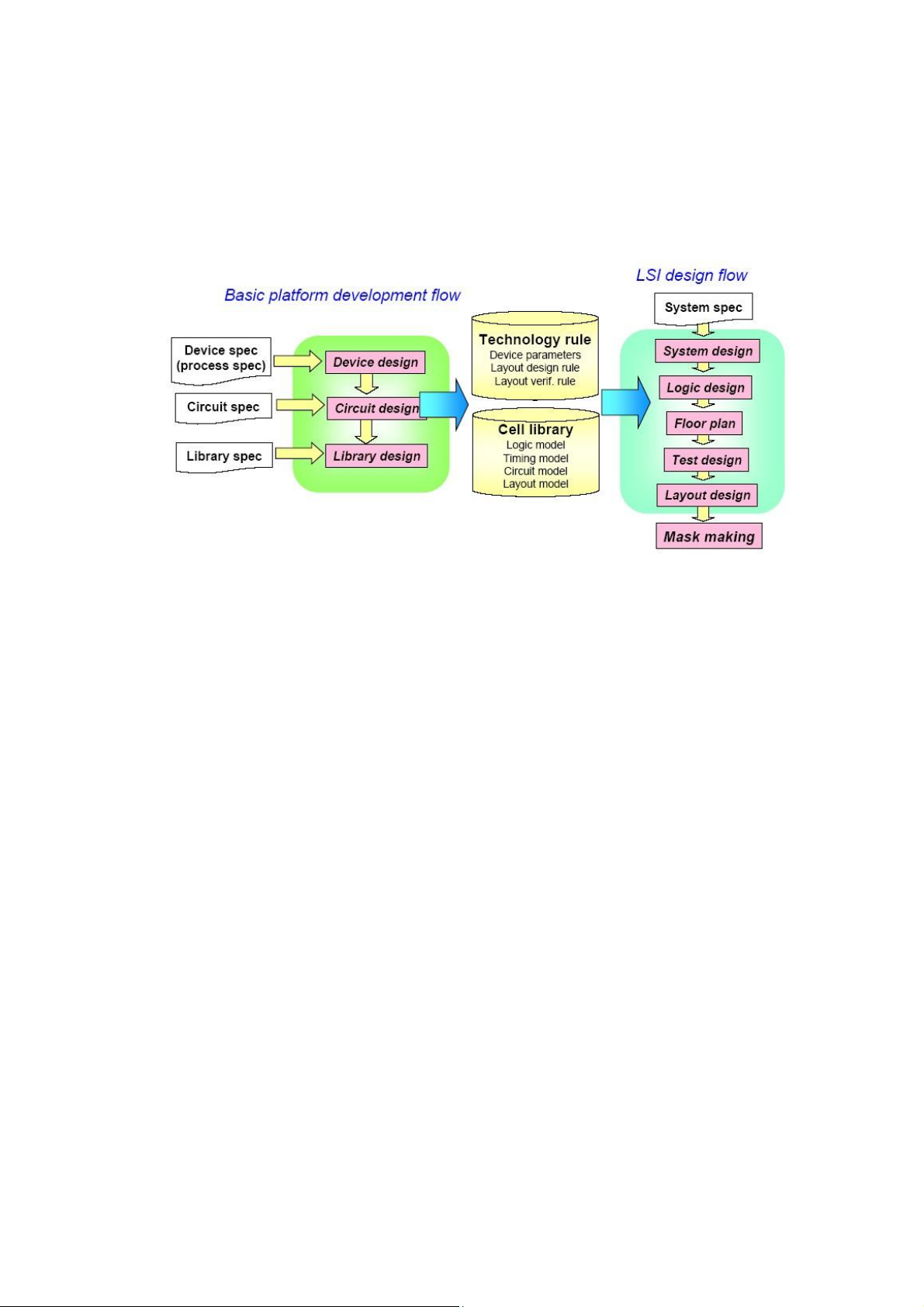

Nguyên lý thiết kế chip ICs số thường dựa trên quá trình “Basic platform development flow”

Hình 1.1: Tổng quan về nguyên lý thiết kế Chip

Khi thực hiện một thiết kế ta cần phân tích, xác định các đặc tính kỹ thuật của IC số

bằng cách tìm hiểu xu hướng thị trường, các yêu cầu của khách hàng. Từ đó đưa ra

các đặc trưng (spec) của hệ thống, các thông số kỹ thuật: hoạt động của hệ thống

(performance), tiêu hao năng lượng (power dissipation), độ tin cậy, giá cả… Trong

quá trình thiết kế ta cần quan tâm: –

Tối ưu hóa hệ thống: rút gọn các phần dư, mô tả không cần thiết. –

Cần phân tích để tránh các tình huống, yếu tố có thể làm thay đổi hệ thống. Ví

dụ: cấu trúc các khối, phân tầng thiết kế, chiều dài dây nối, … có thể làm thay

đổi tần số hoạt động tối đa, công suất tiêu tán của chip…

Về mặt kỹ thuật ta cần quan tâm đến spec, và các thông số kỹ thuật khác: tần số hoạt

động, kích thước, công nghệ chế tạo.

Các hệ thống lớn thường được xây dựng lên bằng cách kế thừa các hệ thống nhỏ có

sẵn. Kết hợp và phát triển các hệ thống nhỏ để có được hệ thống lớn. Tập hợp các hệ

thống nhỏ này được lưu giữ trong thư viện. Đây chính là quá trình hình thành các thư

viện thiết kế (các library cell).

Ngoài các library cell, còn cần có thêm các thư viện công nghệ, các luật, quy tắc thiết kế,…

2. Sơ đồ khối mạch thiết kế

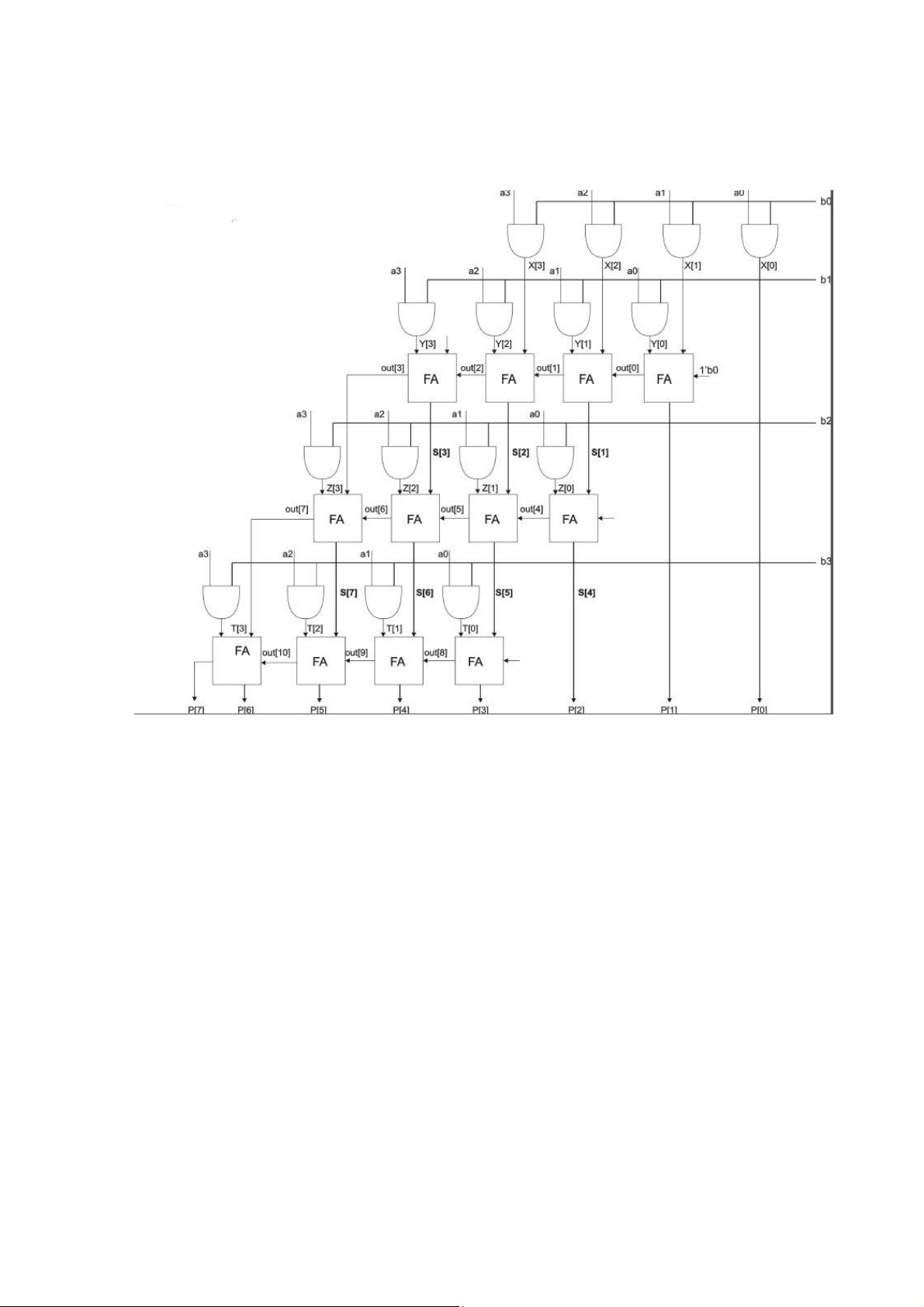

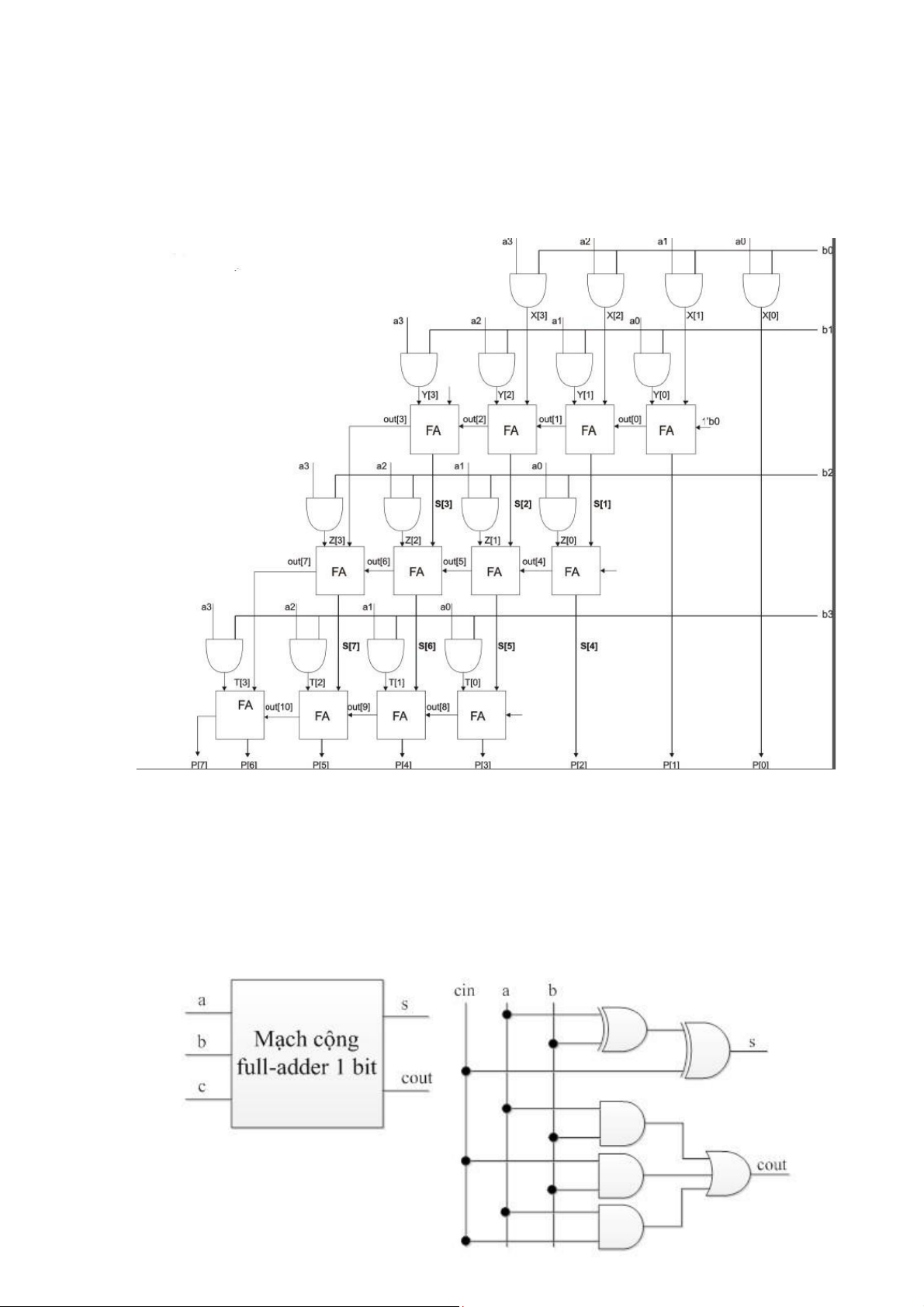

Hình 2.1 Sơ đồ khối bộ nhân 4 bits

CHƯƠNG II: TÌM HIỂU NGÔN NGỮ VERILOG/ VHDL

1. Một số khái niệm về Verilog

Verilog HDL là một ngôn ngữ mô tả phần cứng đa mục đích dễ học và dễ sử dụng.

Nó có cấu trúc đơn giản tương tự ngôn ngữ lập trình C. Đối với người thiết kế đã có

kinh nghiệm trong lập trình với ngôn ngữ C sẽ thấy dễ dàng khi học về Verilog.

Verilog cho phép người thiết kế mô tả thiết kế ở nhiều cấp độ: mô tả hành vi, mô tả

luồng dữ liệu, mô tả mức cổng, thanh ghi hoặc kết hợp giữa các mức này. Do đó

người thiết kế chỉ cần học một ngôn ngữ duy nhất cho nhiều loại thiết kế khác nhau.

Hầu hết các công cụ tổng hợp đều hỗ trợ ngôn ngữ Verilog. Do đó, Verilog ngày càng

trở nên phổ biến và là lựa chọn của các nhà thiết kế.

Tất cả các nhà sản xuất đều cung cấp thư viện VerilogHDL để tổng hợp cho thiết kế.

Nên việc sử dụng Verilog cho phép chúng ta lựa chọn nhà sản xuất. 2.

Phương pháp thiết kế

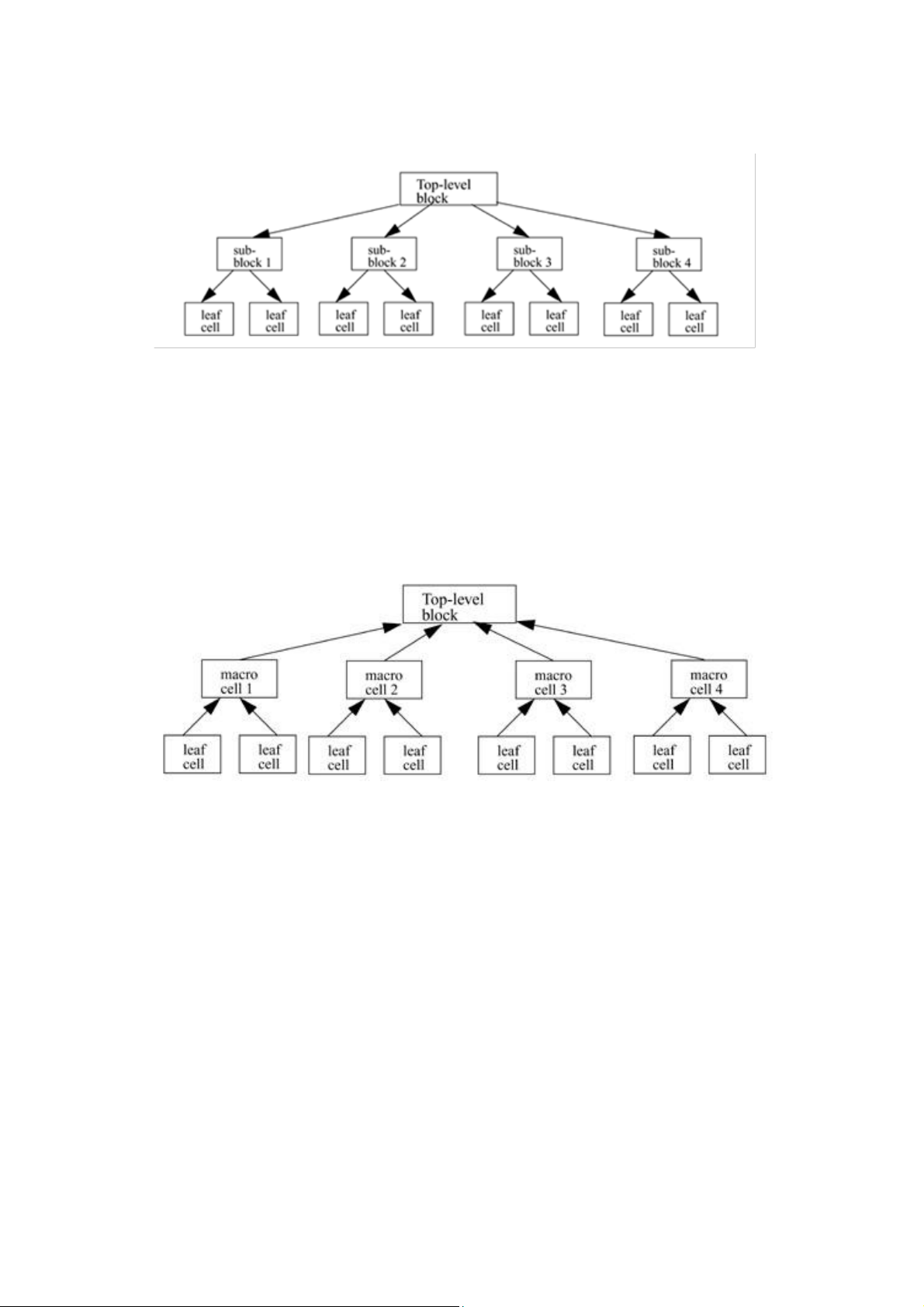

Để dễ cho việc thiết kế người ta thường chia nhỏ công việc ra để giải quyết.

Sau khi chia nhỏ công việc cho thiết kế người ta có thể thực hiện thiết kế theo 2

phương pháp từ trên xuống (top-down) hoặc từ dưới lên (bottom-up).

Top-down là phương pháp thiết kế thực hiện thiết kế các khối top trước rồi mới thiết

kế các khối chính, cuối cùng mới thiết kế các khối cell lá (leaf cell). Top-down design

đòi hỏi người thiết kế rất cẩn thận và tuân thủ chặt các nguyên tắc trong thiết kế. Các

module con được gọi khi chưa được thiết kế.

Hình 2.1 Mô tả phương pháp thiết kế Top-down

Bottom-up là phương pháp thiết kế mà trong đó ta sẽ xây dựng các khối nhỏ trước.

Sau đó các khối thiết kế lớn sẽ được xây dựng từ các khối thiết kế nhỏ này. Từng

bước xây dựng lên các khối cao hơn cho đến khi xây dựng lên được top module.

Hình 2.2 Mô tả về việc thiết kế Bottom-up

3. Các mức mô tả Logic

Trong Verilog ta có nhiều cấp độ mô tả:

Mô tả mức trạng thái (hành vi).

Mô tả mức luồng dữ liệu. Mô tả mức cổng. Mô tả mức Switch.

Verilog cũng cho phép người thiết kế kết hợp bốn mức mô tả này trong cùng một module.

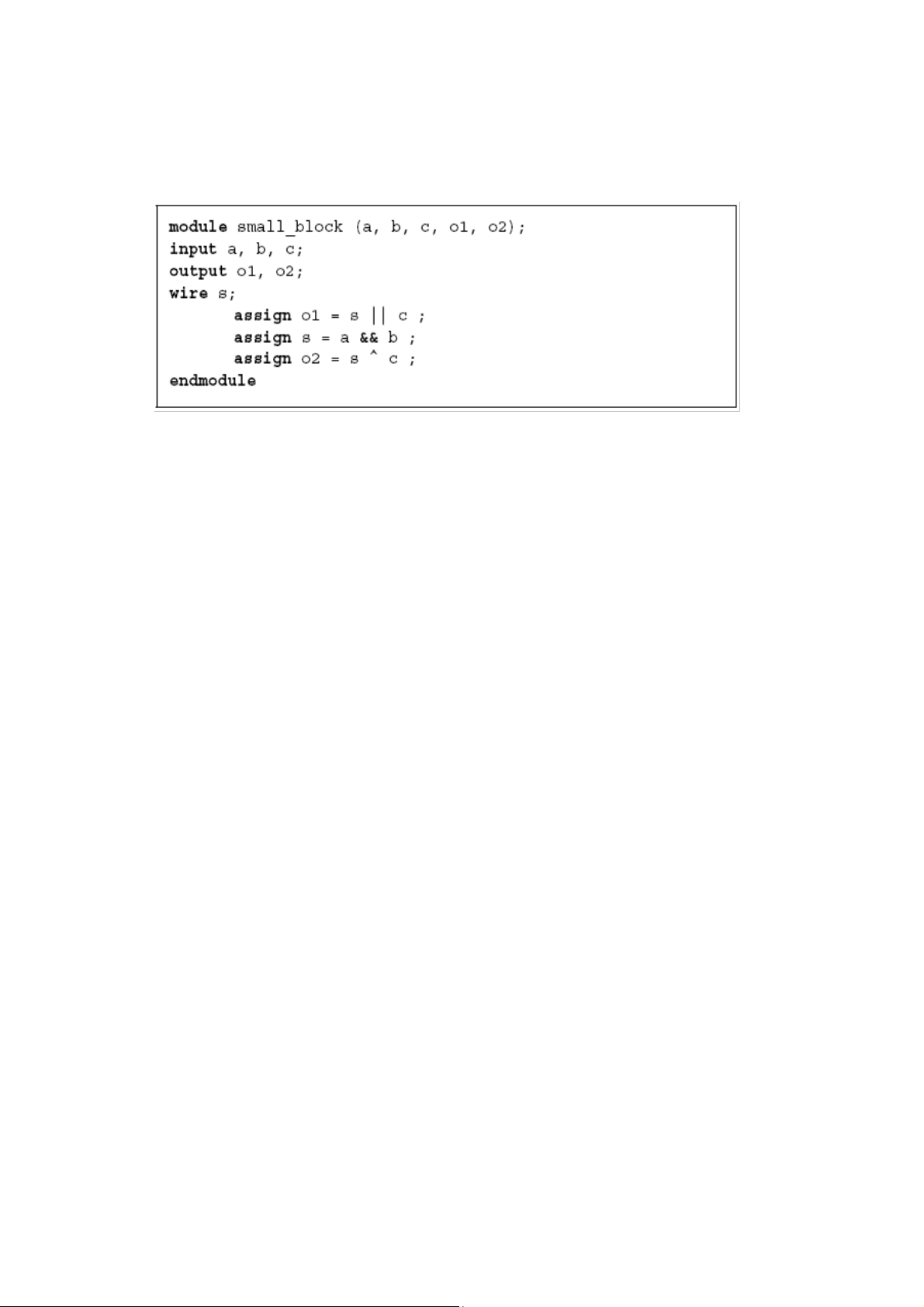

Trong Verilog mỗi khối mô tả được gọi là một module. Trong một module ta có thể

gọi thể hiện của các module thấp hơn.

Verilog HDL : Là ngôn ngữ để thiết kế một hệ thống trong đó có thể có cả CPU.Các

khối (module) chức năng trong HLD được thực hiện song song, hoặc là tuần tự tùy vào người lập trình.

4. Cấu trúc và các viết chương trình một module 4.1 Cấu trúc 1) Module

Verilog đưa ra một khái niệm là module. Module là một khối cơ bản được xây dựng

trong Verilog. Một module có thể là một thành phần hoặc một tập hợp các khối thiết

kế nhỏ hơn. Một module phải diễn tả, thể hiện được các giao tiếp bên ngoài cũng như

nội dung bên trong của khối. Nội dung này có thể được mô tả ở mức cấu trúc, luồng

dữ liệu hay mô tả hành vi.

Hình 3.1: Ví dụ về module đơn giản

Trên đây là một module nhỏ được mô tả gồm các phép tính logic đơn giản.

Hình 3.2: Cấu trúc một module

Thông thường ta có cấu trúc của một module sẽ bao gồm các phần chính sau:

-Khai báo, định nghĩa module.

-Khai báo port xuất, nhập và tín hiệu bên trong module.

-Mô tả chức năng của module. -Kết thúc module. Phân tích ví dụ. 1

Trong module thì các port xuất nhập phải được khai báo bằng các từ khóa: “input”, “output”.

1 Các tín hiệu bên trong của module cũng được khai báo ở dạng các “Register” hoặc các “Net”. 1

Các “Register” được dùng cho các tín hiệu có khả năng tự lưu trữ dữ liệu.

1 Các “Net” trong Verilog diễn tả một kết nối vật lý trong phần cứng. Nó có thể được

dùng để nối các module hay cổng lại với nhau, nhưng bản thân nó không thể tự lưu trữ giá trị. 1

Một “wire” có thể được dùng bất cứ chỗ nào trong module, nó chỉ được gán bởi: •

Ngõ ra của một module, cổng. •

Gán với một phép gán liên tục. •

Các phép gán liên tục được khai báo bằng lệnh “assign”. Tất cả các phép gán

liên tục đều được thực hiện đồng thời.

4.2 Các qui ước

Verilog hỗ trợ cho người thiết kế mô tả hệ thống ở nhiều cấp độ khác nhau. Mức mô

tả hành vi: Là cấp độ mô tả trừu tượng cao nhất. Module được hiện thực trong các

điều kiện mong muốn thiết kế về mặt logic. Mà không quan tâm đến việc thực hiện

về mặt phần cứng. Do vậy ở cấp độ thiết kế này Verilog sẽ giống với ngôn ngữ C nhất.

Mức mô tả luồng dữ liệu: Ở mức này người thiết kế phải chỉ rõ luồng dữ liệu. Người

thiết kế phải hiểu được luồng dữ liệu giữa các thanh ghi, hiểu được dữ liệu sẽ được

xử lý như thế nào trong thiết kế.

Mức mô tả mức cổng: Module được thể hiện giới hạn mức cổng và sự kết nối giữa các cổng

Mức mô tả Switch: Là mức mô tả cấp thấp nhất mà Verilog cung cấp. Module được

thực hiện dựa vào các điều khoảng của các switch, các storage nodes, và kết nối của chúng.

4.3 Các phép tính

Là phần được dùng để mô tả các phép toán trong Verilog, trước khi đi sâu vào các

phép toán ta cần nắm sơ về toán hạng. -Toán hạng Toán hạng có thể là:

Con số; các net (bit hoặc phần bit được lựa chọn); các reg (bit hoặc phần bit chọn)

Giá trị trả về khi gọi một function. -Toán tử

Các toán tử được hỗ trợ trong Verilog được miêu tả trong bảng sau

-Các phép toán số học : + ; - ; * ; /

-Các phép toán quan hệ (so sánh): < ; > ; <= ; >=; == ; != -Các phép toán logic : ! && ||

-Toán tử rút gọn : & | ^

-Kết hợp với toán tử not : ~& ~| ~^ Toán tử dịch – Dịch trái: << – Dịch phải >> Toán tử điều kiện:

Conditional_expression ? true_expression: false_expression

CHƯƠNG III: TÌM HIỂU NGUYÊN LÝ HOẠT ĐỘNG CỦA BỘ NHÂN 4 BIT

1. Sơ đồ giải thuật

2. Nguyên lý hoạt động chính

2.1 Nguyên lý hoạt động của bộ cộng (Full adder)

-Khối cộng full adder là khối tổ hợp thực hiện chức năng cộng giá trị 2 ngõ

vào có tính đến cờ nhớ.

Hình 3.5 Các cổng logic trong bộ Full adder 1 bit

-Khối cộng full-adder một bit có bảng sự thật sau A B Cin Cout S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1

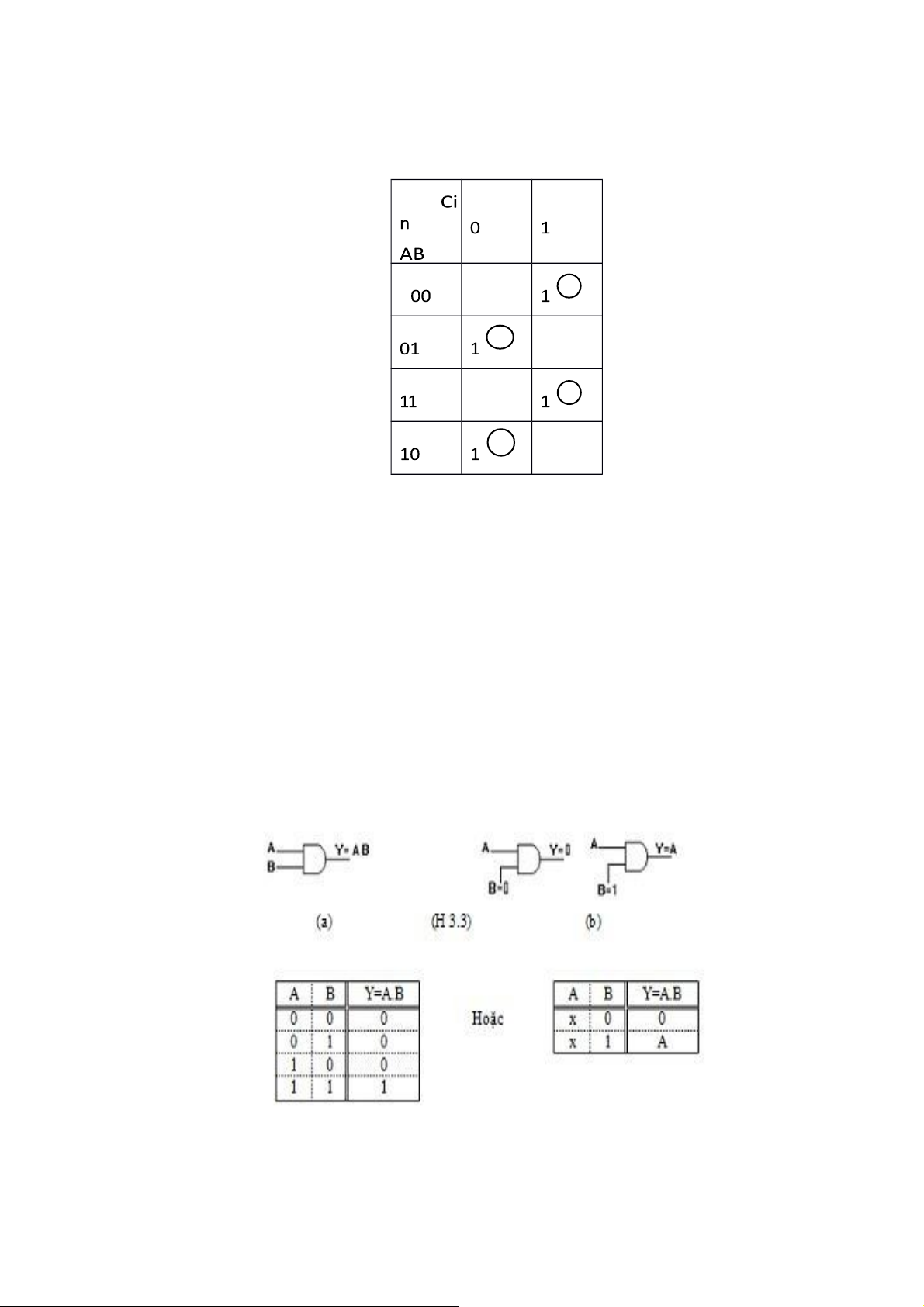

-Dùng bìa Karnaugh rút gọn 2 ngõ ra S và Cout. Ci n 0 1 AB 00 01 1 11 1 1 10 1

➔Hàm Cout sau khi rút gọn: Cout=AB+ACin+Bcin.

➔Biểu diễn dưới dạng cổng logic bằng ngôn ngữ verilog: Cout=A&B|A&Cin| B&Cin

➔Hàm S sau khi rút gọn:S=A⊕B⊕Cin.

➔Biểu diễn dưới dạng cổng logic bằng ngôn ngữ verilog:S=A^B^Cin.

2.2 Nguyên lý hoạt động của bộ nhân (AND) Dùng

thực hiện hàm AND hai hay nhiều biến.

-Cổng AND có số ngõ vào tuỳ thuộc số biến và một ngõ ra.Ngõ ra của cổng là hàm

AND của các biến ngõ vào.

-Ký hiệu cổng AND 2 ngõ vào cho 2 biến (H3.3a). Hình3.3 Nhận xét:

-Ngõ ra cổng AND chỉ ở mức cao khi tất cả ngã vào lên cao.

-Khi có một ngõ vào bằng 0,ngõ ra sẽ bằng 0 bất chấp các ngõ vào còn lại.

-Khi có một ngõ vào bằng 1,ngõ ra bằng AND của các ngõ vào còn lại.

Vậy với cổng AND 2 ngã vào ta có thể dùng 1 ngã vào làm ngã kiểm soát (H 3.3b),

khi ngã kiểm soát = 1, cổng mở cho phép tín hiệu logic ở ngã vào còn lại qua cổng

và khi ngã kiểm soát = 0, cổng đóng , ngã ra luôn bằng 0, bất chấp ngã vào còn lại.

Với cổng AND có nhiều ngã vào hơn, khi có một ngã vào được đưa lên mức cao thì

ngã ra bằng AND của các biến ở các ngã vào còn lại.

CHƯƠNG IV: VIẾT CODE MÔ TẢ MẠCH DÙNG PHẦN MÊM QUARTUS II

Tất cả các thiết kế trong bài báo cáo này đều được viết dựa trên chương trình Quartus

II- phần mềm vừa có thể mô phỏng dạng mạch ban đầu vừa có thể kiểm tra dạng sóng kết quả.

Thiết kế mạch nhân được chia làm hai phần. Đầu tiên là thiết kế khối FA sau đó đến

các cổng AND sau đó kết nối tất cả lại với nhau theo lưu đồ là hoàn thành mạch nhân 4 bits. 1)Khối FA

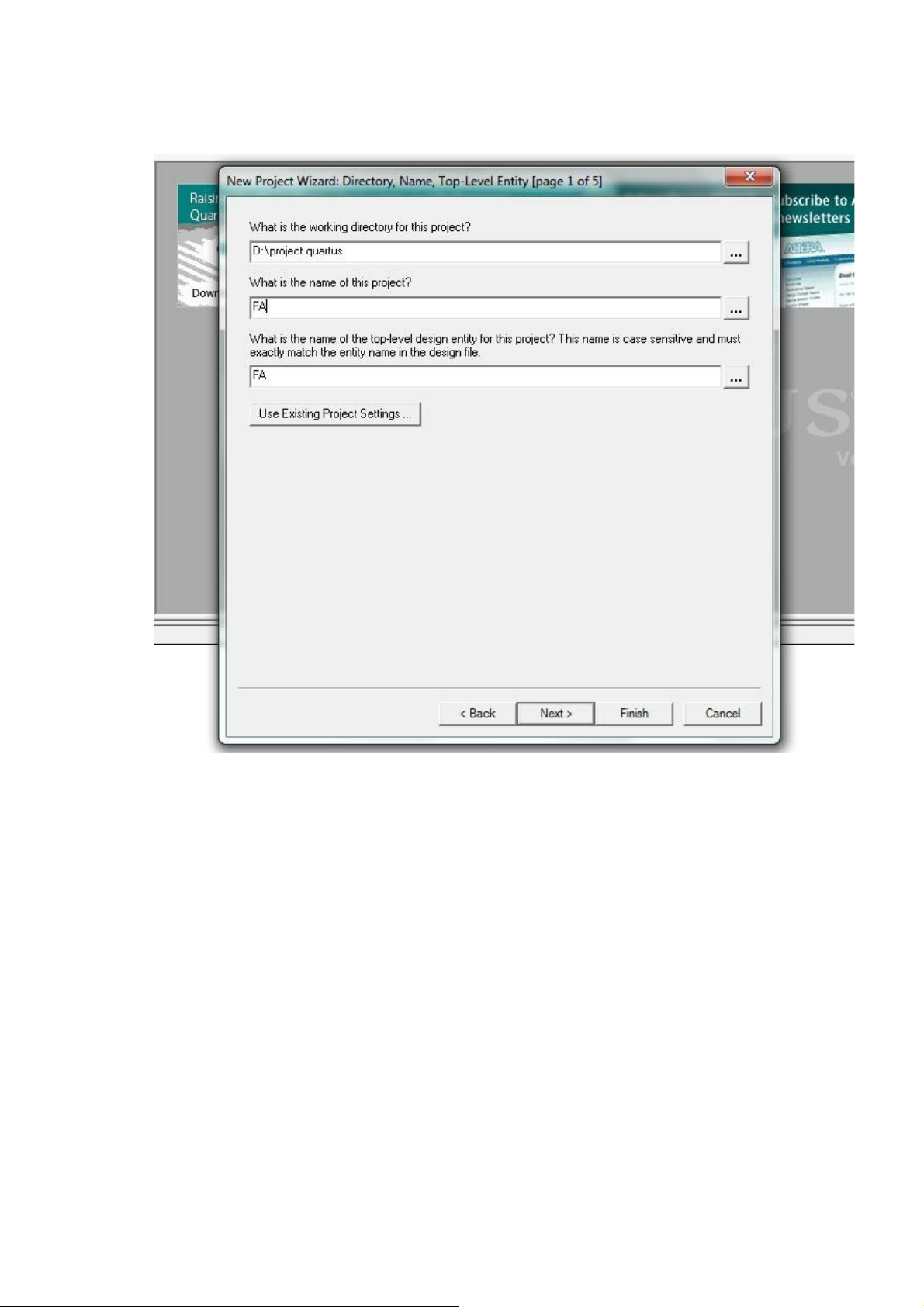

Trước tiên mở chương trình Quartus II và tạo project mang tên FA

Hình 3.6 Tạo file FA để lập trình thiết kế bộ Full adder 1 bit

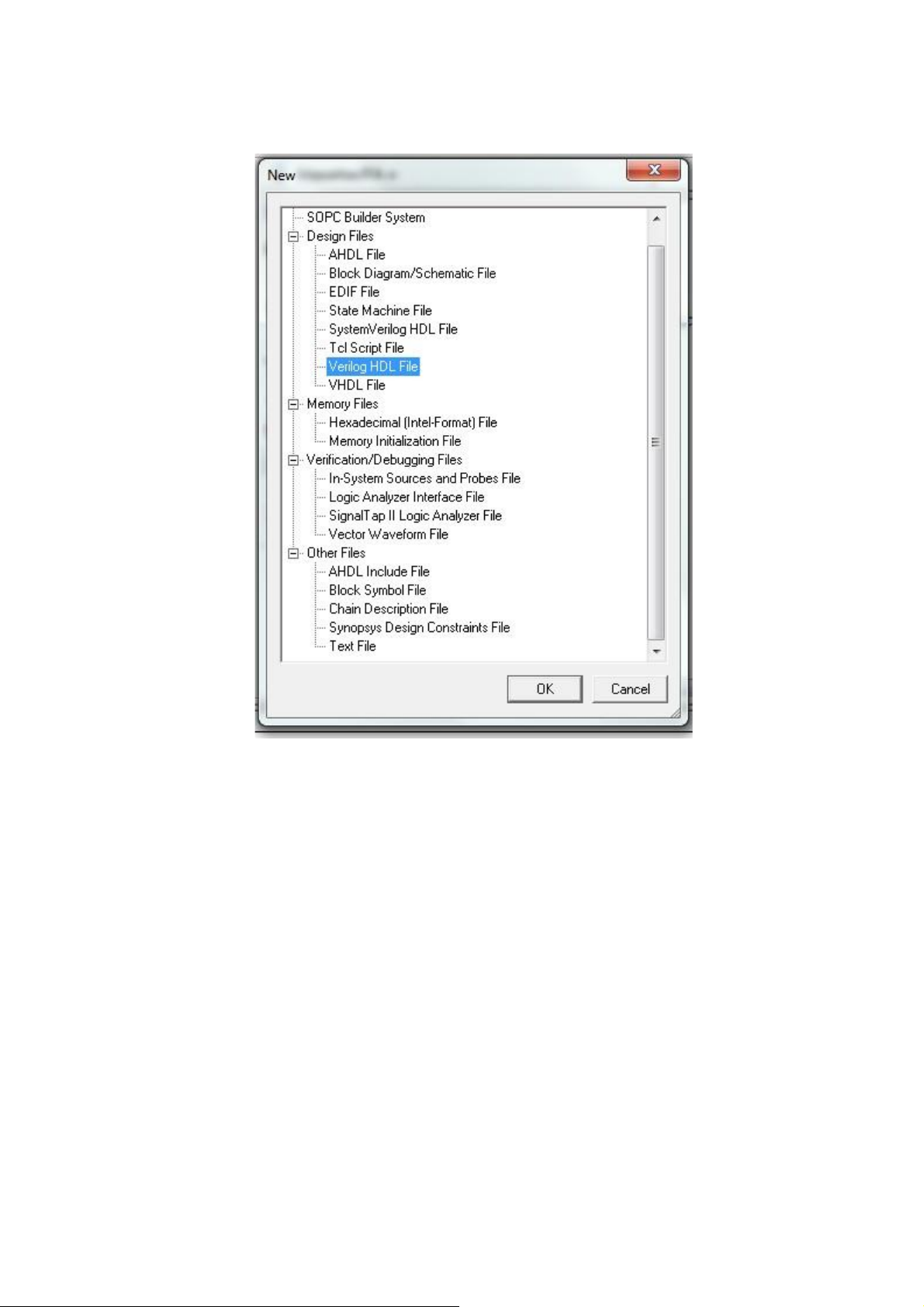

Sau khi tạo xong project ta tiếp tục chọn File-New và chọn tạo file verilog để thiết kế

Hình 3.7 Chọn Verilog HDL File

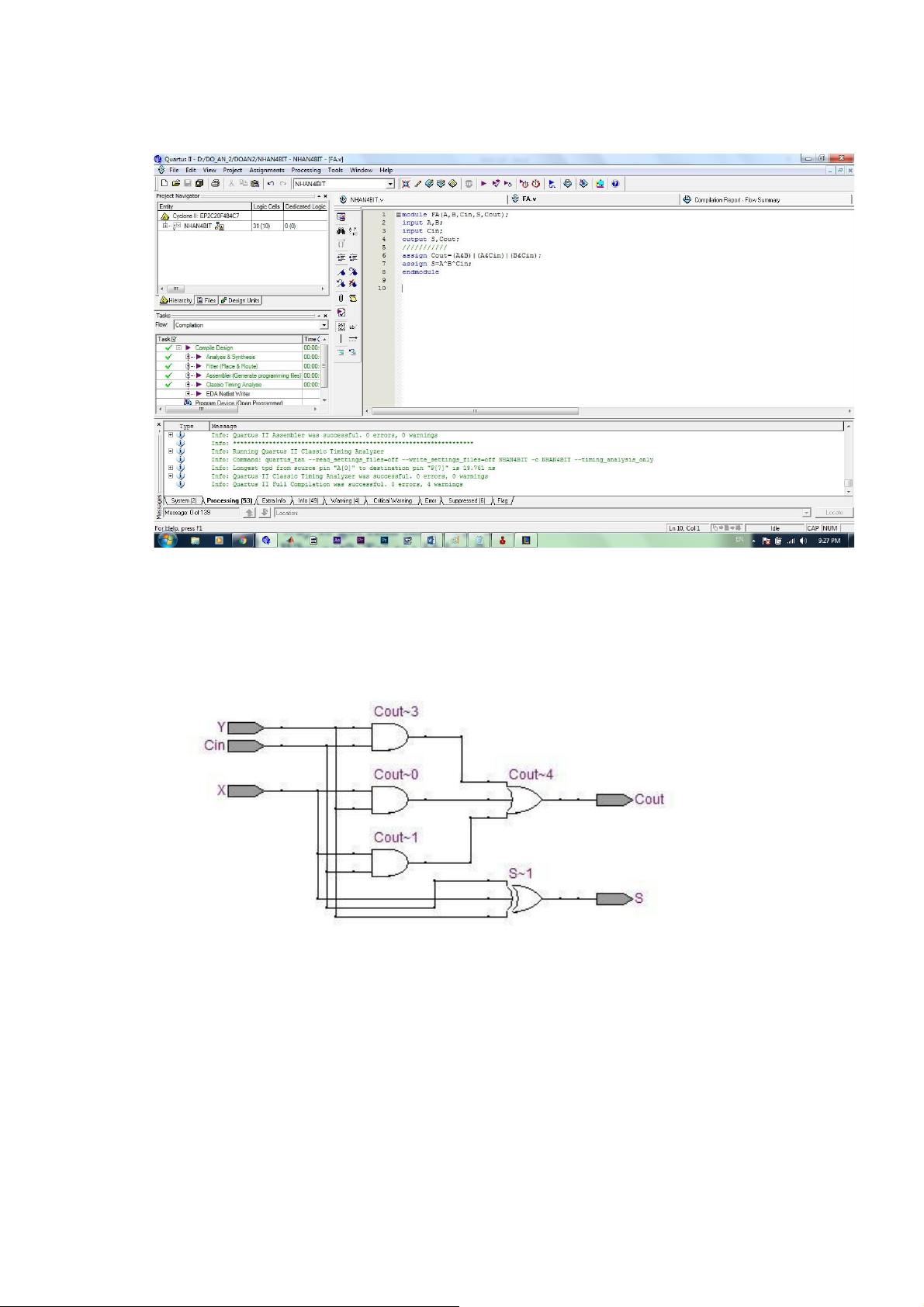

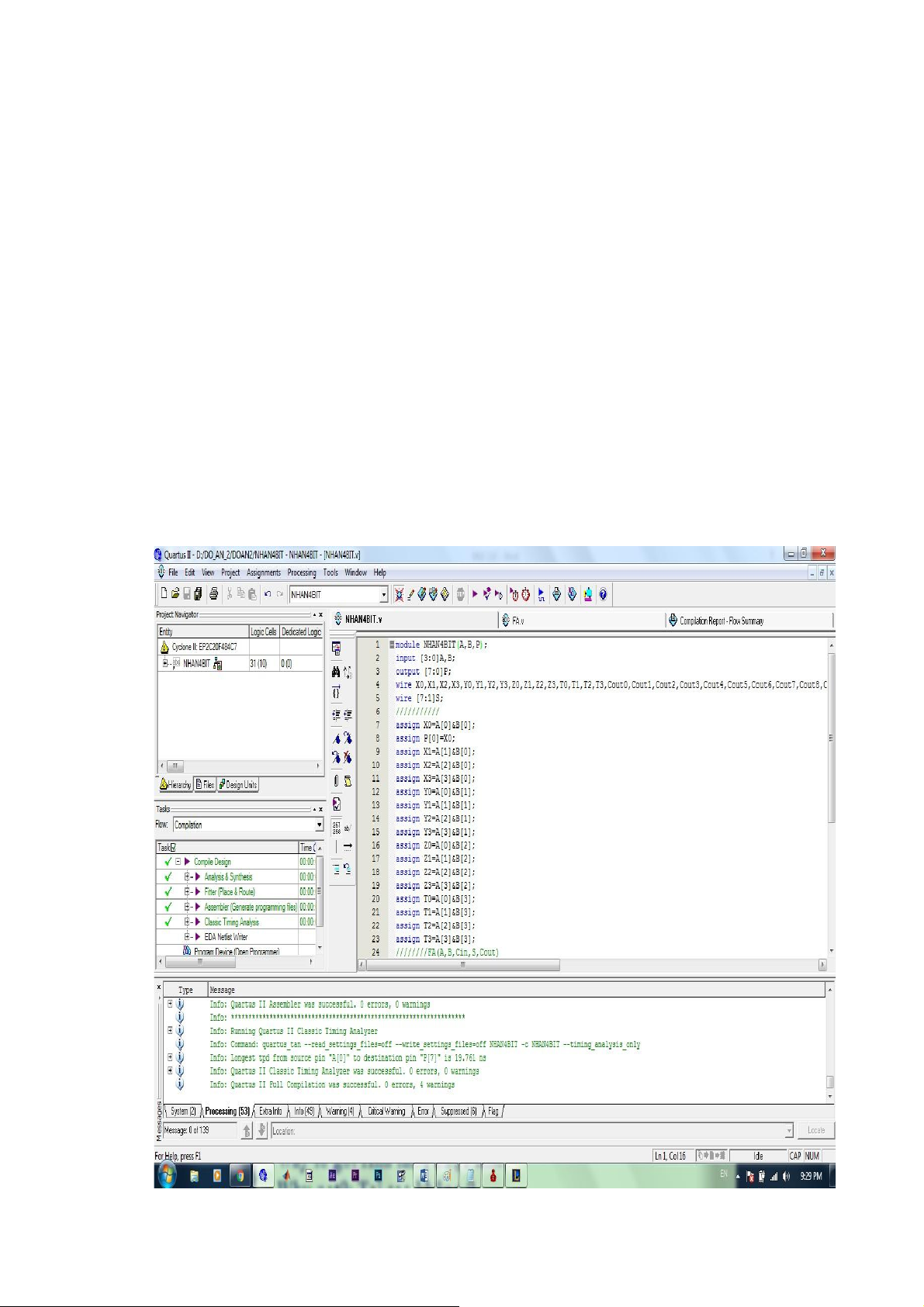

Kế tiếp là soạn thảo code cho khối FA và chạy chương trình.Sau khi dịch thành công ta có mạch sau: module FA(A,B,Cin,S,Cout); input A,B; input Cin; output S,Cout; ////////////////

assign S= A^B^Cin; assign Cout=

(A&B)|(A&Cin)|(B&Cin); endmodule .

Hình 3.9 Viết code bộ Full adder 1bit trên phần mềm quartus II

Hình 3.10 Bộ Full adder 1 bit

Vậy là ta đã thiết kế xong khối FA,kế đến ta sẽ thiết kế các cổng AND và kết nối mạch

2)Thiết kế cổng AND và kết nối các thành phần trong mạch

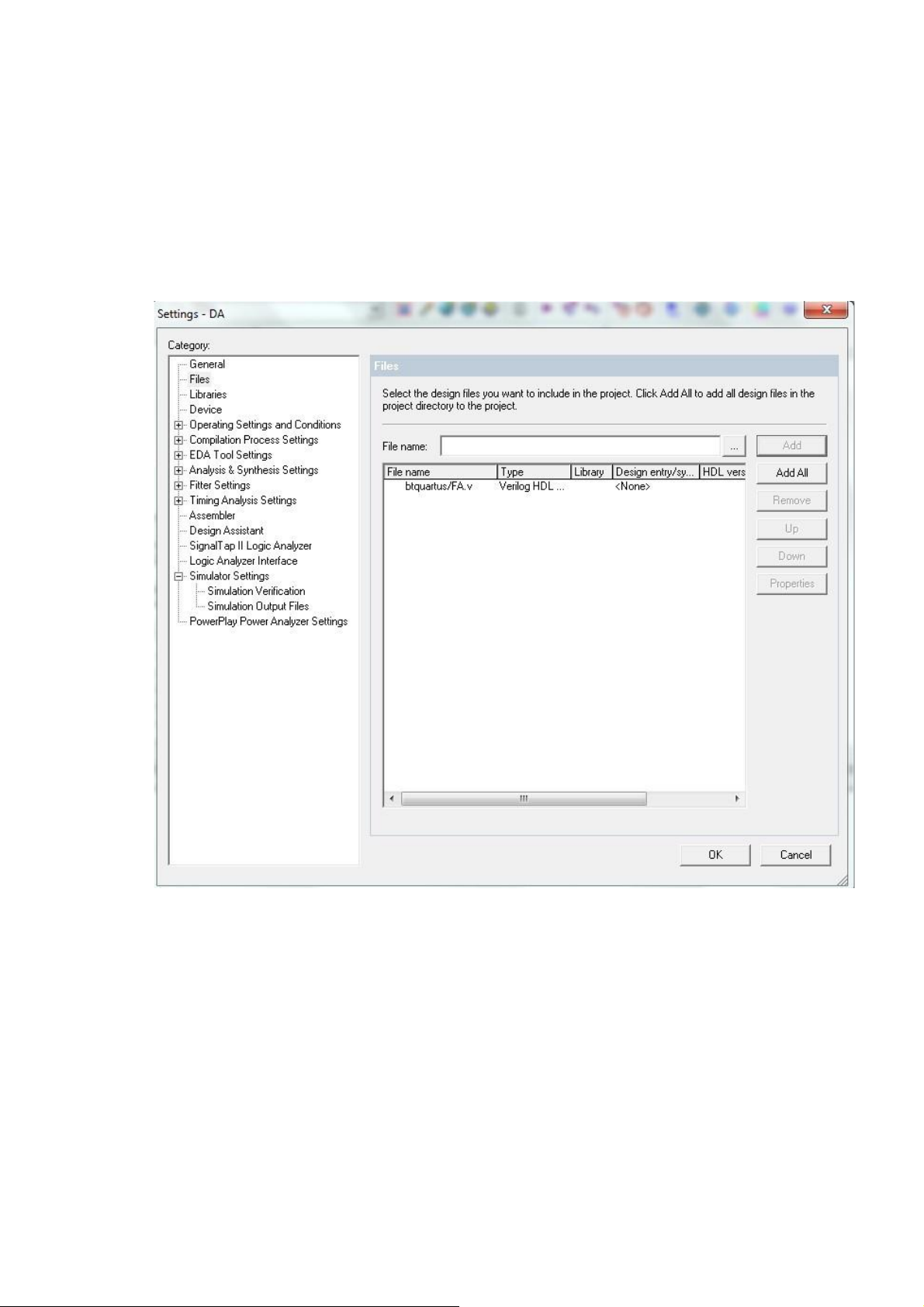

Đầu tiên ta tạo một project mới mang tên NHAN4BIT.Lưu ý khi tạo project ta phải

thêm vào project FA đã thiết kế lúc đầu để khi viết chương trình ta có thể dử dụng.Sau khi chọn xong nhấn OK Hình 3.11 Setup

Khởi tạo project xong ta lại chọn file verilog để thiết kế như trên

Kế tiếp là soạn thảo code và chạy chương trình. Sau khi dịch thành công ta có mạch sau: module NHAN4BIT(A,B,P); input (3:0)A,B; output (7:0)P; wire

X0,X1,X2,X3,Y0,Y1,Y2,Y3,Z0,Z1,Z2,Z3,T0,T1,T2,T3,Cout0,Cout1,Cout2,Cout3,

Cout4,Cout5,Cout6,Cout7,Cout8,Cout9,Cout10; wire (7:1)S; ////////// assign X0= A[0]&B[0]; assign P0= X0; assign X1= A[1]&B[0]; assign X2= A[2]&B[0]; assign X3= A[3]&B[0]; assign Y0= A[0]&B[1]; assign Y1= A[1]&B[1]; assign Y2= A[2]&B[1]; assign Y3= A[3]&B[1]; assign Z0= A[0]&B[2]; assign Z1= A[1]&B[2]; assign Z2= A[2]&B[2]; assign Z3= A[3]&B[2]; assign T0= A[0]&B[3]; assign T1= A[1]&B[3]; assign T2= A[2]&B[3]; assign T3= A[3]&B[3]; //////////FA(A,B,Cin,S,Cout) FA A0(X1,Y0,1'b0,P[1],Cout0); FA A1(X2,Y1,Cout0,S1,Cout1); FA A2(X3,Y2,Cout1,S2,Cout2);

FA A3(1'b0,Y3,Cout2,S3,Cout3); FA A4(S1,Z0,1'b0,P[2],Cout4); FA A5(S2,Z1,Cout4,S5,Cout5); FA A6(S3,Z2,Cout5,S6,Cout6);

FA A7(Cout3,Z3,Cout6,S7,Cout7); FA A8(S5,T0,1'b0,P[3],Cout8);

FA A9(S6,T1,Cout8,P[4],Cout9);

FA A10(S7,T2,Cout9,P[5],Cout10);

FA A11(Cout7,T3,Cout10,P[6],P[7]); Endmodule

Hình 3.12 Viết code Bộ nhân 4 bits trên phần mềm quartus II CHƯƠNG V: MÔ PHỎNG MẠCH

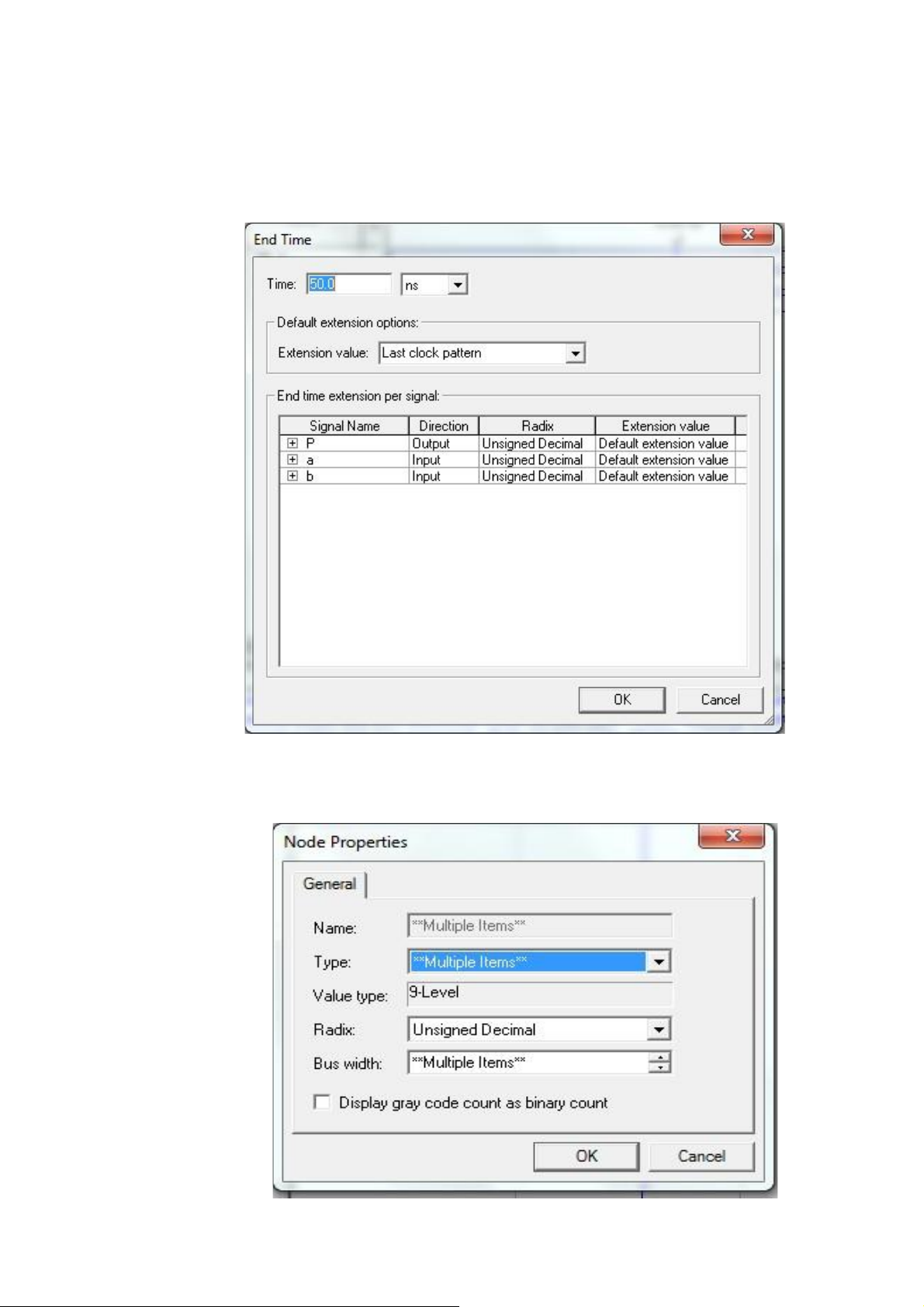

Khi biên dịch thành công ta đưa vào dạng sóng của các biến và nhập vào các thông số cần thiết

Hình 3.13 Thiết lập thời gian

Hình 3.14 Thiết lập dạng Unsigned Decimal để dễ dàng xét kết quả

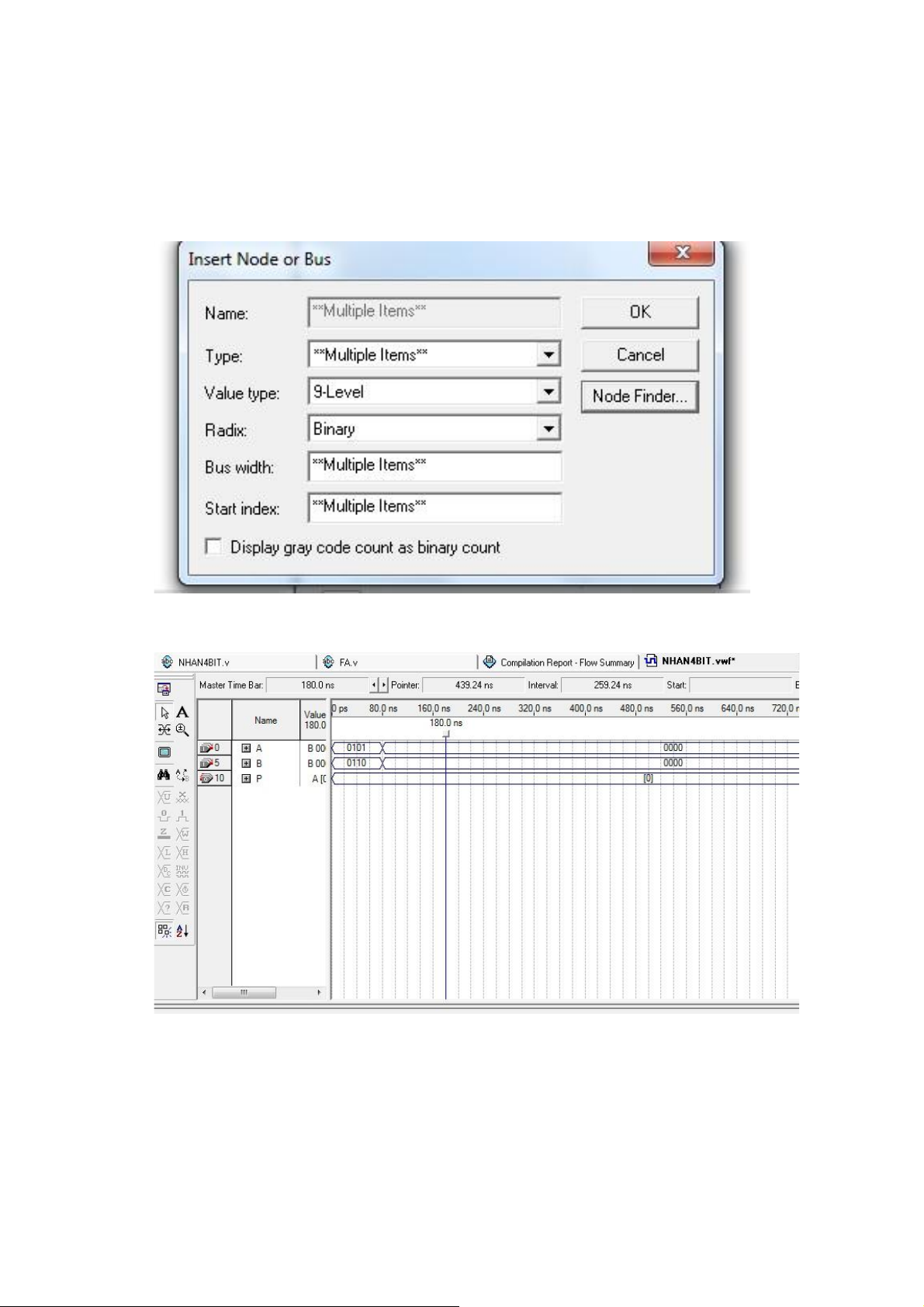

Trong hình 3.15 ta chọn Radix là Binary số nhị phân

Hình 3.15 Thiết lập dạng Binary

Hình 3.16 Mô phỏng tính toán ở dạng số nhị phân

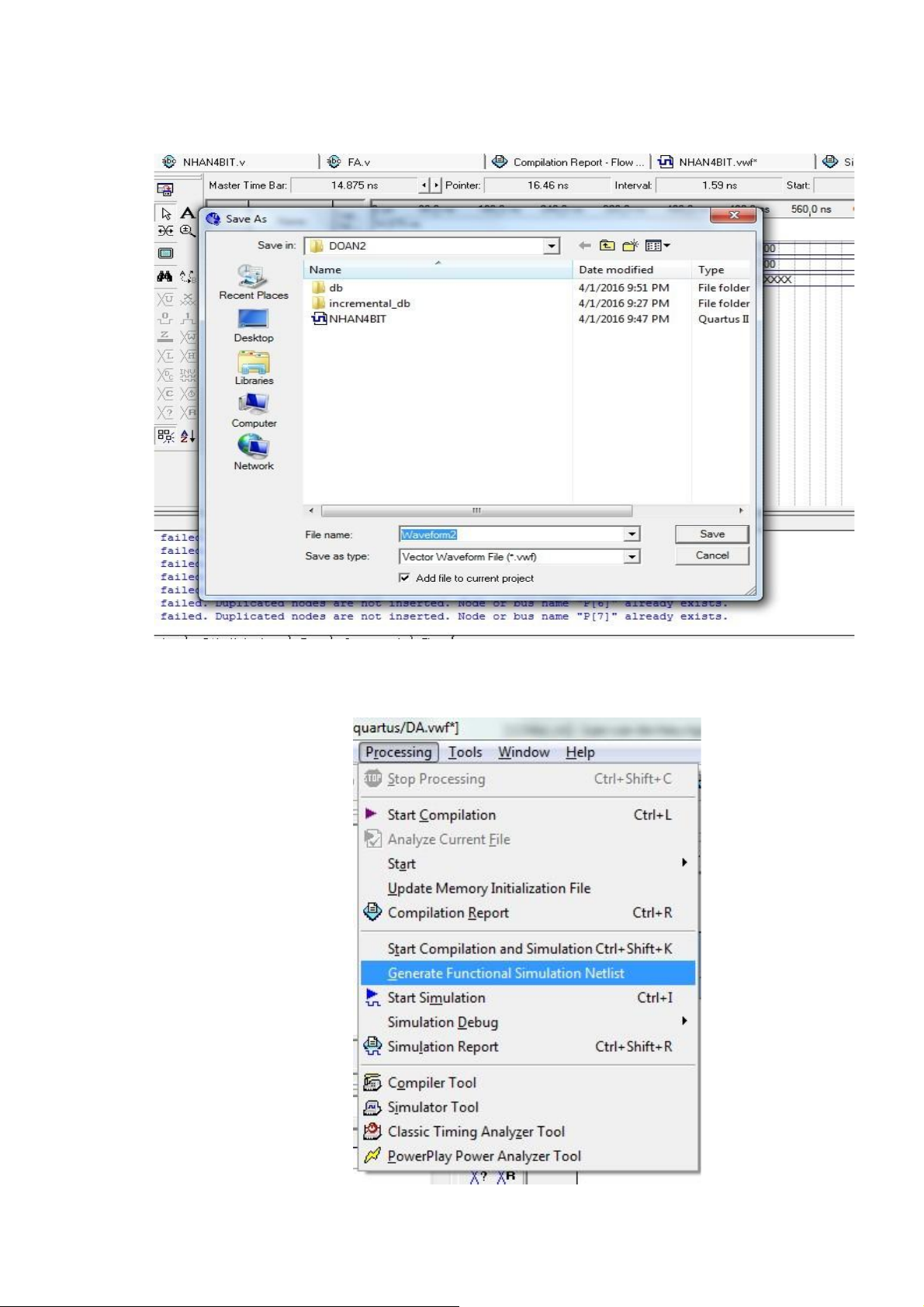

Xong ta bắt đầu lưu lại theo trình tự sau và simulation nó theo các hình vẽ:

Hình 3.17 Save file waveform để tiến hành chạy mô phỏng

Hình 3.18 Tiến hành chọn Generate Functional Simulation Netlist