Preview text:

BẢNG PHÂN CHIA NHIỆM VỤ VÀ MỨC ĐỘ HOÀN THÀNH CỦA TỪNG THÀNH VIÊN

BỘ GIÁO DỤC VÀ ĐÀO TẠO

TRƯỜNG ĐẠI HỌC SƯ PHẠM KỸ THUẬT

THÀNH PHỐ HỒ CHÍ MINH MỨC ĐỘ S HỌ VÀ TÊN MSSV NHIỆM VỤ

KHOA: ĐIỆN – ĐIỆN TỬ HOÀN TT THÀNH Khảo sát các IC và làm 1 Hoàng Minh Nhật 21151510 ppt

Thiết kế mạch nguyên lí Nguyễn Quỳnh 2 21151301 và mô phỏng trên BÁO CÁO TOPIC Nhu KỸ THUẬT SỐ protues Lựa chọn linh kiện cho ĐỀ TÀI

khối đếm, khối hiển thị

THIẾT KẾ MẠCH ĐẾM NHỊ PHÂN KHÔNG Thái Thị Huỳnh 3 21142649

và khối chuyển đổi; mô

ĐỒNG BỘ 12 BIT UP/DOWN ĐIỀU KHIỂN BẰNG Như

1 NÚT NHẤN (MẠCH SỬ DỤNG IC 4027) phỏng trên protues; tổng hợp word

Giảng viên: ThS. Võ Đức Dũng

Vẽ sơ đồ khối và hoạt

Mã lớp học: DIGI330163_22_2_13 Châu Đặng Mỵ 4 21151302

động của các khối; làm

Sinh viên thực hiện Nương STT Họ và tên ppt MSSV 1 Hoàng Minh Nhật 21151510 Lựa chọn linh kiện và 2 Nguyễn Quỳnh Nhu 21151301 5 Nguyễn Văn Pháp 3 21151303 tính toán cho khối tạo Thái Thị Huỳnh Như 21142649 4 Châu Đặng Mỵ Nương xung 21151302 5 Nguyễn Văn Pháp 21151303 STT H ọ và tên MSSV

Thành phố Hồ Chí Minh, tháng 5 năm 2023

NHẬN XÉT CỦA GIẢNG VIÊN

...........................................................................................................................................

...........................................................................................................................................

...........................................................................................................................................

...........................................................................................................................................

...........................................................................................................................................

...........................................................................................................................................

...........................................................................................................................................

...........................................................................................................................................

...........................................................................................................................................

Ngày…….Tháng…….Năm……. Ký tên

------------------------- MỤC LỤC

CHƯƠNG 1: CÁC IC LIÊN QUAN CÓ TRONG MẠCH CẦN THIẾT KẾ.....1

1.1. Khảo sát IC555:.......................................................................................1

1.1.1. Thông số:..........................................................................................1

1.1.2. Chức năng của IC555:.......................................................................1

1.2. Khảo sát IC 4027:....................................................................................2

1.2.1. Sơ đồ chân.........................................................................................3

1.2.2. Mô tả chân linh kiện..........................................................................3

1.2.3. Thông số kỹ thuật..............................................................................3

1.2.4. Nơi ứng dụng....................................................................................4

1.2.5. Cách sử dụng.....................................................................................4

1.2.6. Các ứng dụng....................................................................................4

CHƯƠNG 2: SƠ ĐỒ KHỐI MẠCH THIẾT KẾ VÀ HOẠT ĐỘNG CỦA CÁC

KHỐI TRONG SƠ ĐỒ..................................................................................................6

2.1. Sơ đồ khối của mạch thiết kế...................................................................6

2.2. Hoạt động của các sơ đồ khối..................................................................6

CHƯƠNG 3: MẠCH NGUYÊN Lo VÀ Lo DO CHỌN CÁC LINH KIÊqN,

TrNH TOÁN CÁC THÔNG SỐ TRONG MẠCH........................................................7

3.1. Mạch nguyên lý:......................................................................................7

3.2. Lý do chọn các linh kiện và tính toán các thông số trong mạch:..............7

3.2.1. Khối tạo xung dao động:.................................................................7

3.2.2. Khối đếm IC4027.........................................................................10

3.2.3. Khối chuyển đổi hai chế độ..........................................................11

3.2.4. Khối hiển thị...................................................................................12

CHƯƠNG 4: MÔ PHỎNG MẠCH TRÊN PHẦN MỀM PROTUES..............14

CHƯƠNG 5: THI CÔNG MẠCH....................................................................17

CHƯƠNG 1: CÁC IC LIÊN QUAN CÓ TRONG MẠCH CẦN THIẾT KẾ 1.1. Khảo sát IC555:

IC 555 là một trong những dòng sản phẩm của công ty Signetics Corporation.

với 2 dòng sản phẩm là SE555/NE555. IC 555 là một vi mạch dùng để tạo thời gian trễ

(Time Delays) và tạo xung (Oscillation) với mức độ ổn định và tỷ lệ chính xác cao.. 1.1.1. Thông số:

- Điện áp đầu vào : 2 - 18V ( Tùy từng loại của 555 : LM555, NE555, NE7555..)

- Dòng tiêu thụ : 6mA - 15mA

- Điện áp logic ở mức cao : 0.5 - 15V

- Điện áp logic ở mức thấp : 0.03 - 0.06V

- Công suất tiêu thụ (max): 600mW

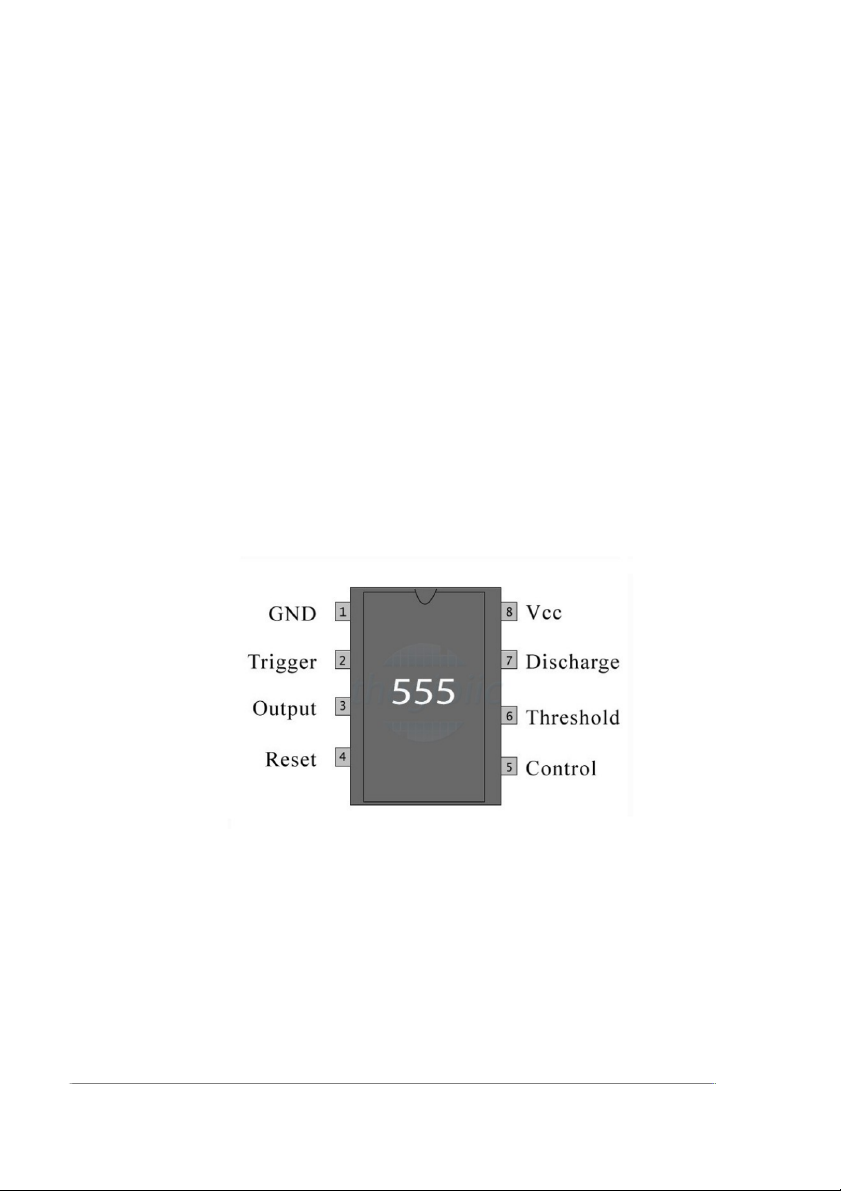

1.1.2. Chức năng của IC555: a) Bố trí chân

Hình 1: IC NE555 N gồm có 8 chân

b)Chức năng của từng chân.

+ Chân số 1 (GND): cho nối GND để lấy dòng cấp cho IC hay chân còn gọi là chân chung. 1

+ Chân số 2 (TRIGGER): Đây là chân đầu vào thấp hơn điện áp so sánh và

được dùng như 1 chân chốt hay ngõ vào của 1 tần so áp.Mạch so sánh ở đây dùng các

transitor PNP với mức điện áp chuẩn là 2/3Vcc.

+ Chân số 3 (OUTPUT): Chân này là chân dùng để lấy tín hiệu ra logic. Trạng

thái của tín hiệu ra được xác định theo mức 0 và 1.

+ Chân số 4 (RESET): Dùng lập định mức trạng thái ra. Khi chân số 4 nối

masse thì ngõ ra ở mức thấp. Còn khi chân 4 nối vào mức áp cao thì trạng thái ngõ ra

tùy theo mức áp trên chân 2 và 6.Nhưng mà trong mạch để tạo được dao động thường hay nối chân này lên VCC.

+ Chân số 5 (CONTROL VOLTAGE): Dùng làm thay đổi mức áp chuẩn trong

IC 555 theo các mức biến áp ngoài hay dùng các điện trở ngoài cho nối GND.

+ Chân số 6 (THRESHOLD): là một trong những chân đầu vào so sánh điện áp

khác và cũng được dùng như 1 chân chốt.

+ Chân số 7 (DISCHAGER): có thể xem chân này như 1 khóa điện tử và chịu

điều khiển bỡi tầng logic của chân 3 .Khi chân 3 ở mức áp thấp thì khóa này đóng

lại.ngược lại thì nó mở ra. Chân 7 tự nạp xả điện cho 1 mạch R-C lúc IC 555 dùng như 1 tầng dao động .

+ Chân số 8 (Vcc): là chân cung cấp áp và dòng cho IC hoạt động. Không có

chân này coi như IC chết. Nó được cấp điện áp từ 2V -->18V

1.2. Khảo sát IC 4027:

CD4027 là IC gói JK Flip-Flop kép tốc độ cao dựa trên CMOS, mỗi cổng có

xung clock ngõ vào và 2 ngõ ra Q và Q’. Là một mạch tích hợp được xây dựng từ các

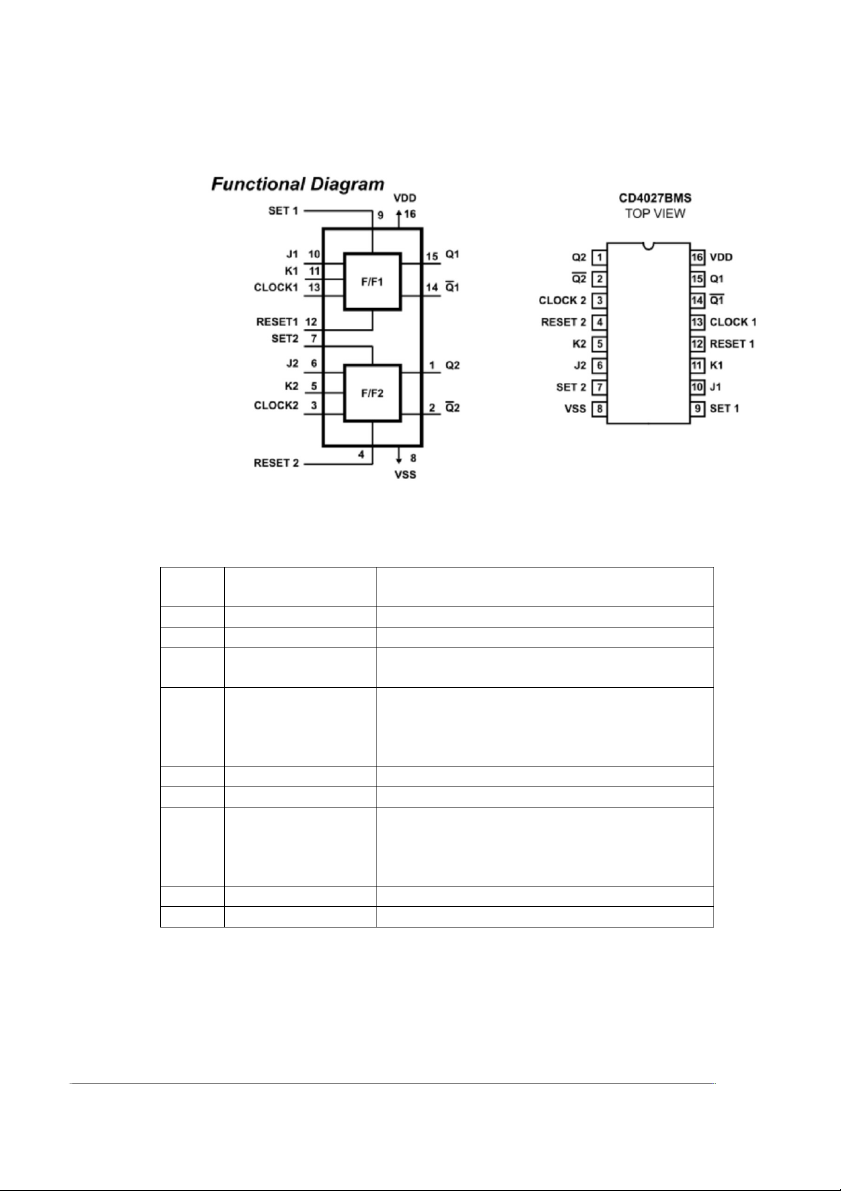

Mosfet và một số điện trở phụ trợ. 2 1.2.1. Sơ đồ chân

Hình 2: IC CD4027 gồm có 16 chân

1.2.2. Mô tả chân linh kiện

IC CD4027 có tổng cộng 16 chân: Số Tên chân Mô tả chân 1, 15 Q2, Q1 Chân đầu ra 2, 14 ~Q2, ~Q1 Chân đầu ra đảo CLOCK 2 , 3, 13 Xung clock CLOCK 1

Khi chân này có mức logic thaaos, giá trị của Q sẽ là 1. 4, 12 Reset 2, Reset 1

Khi chân này có mức logic cao giá trị đầu ra ~Q sẽ là 1. 5, 11 K2, K1 Chân đầu vào 1 6, 10 J2, J1 Chân đầu vào 2

Khi chân này ở mức logic cao, giá trị của Q sẽ là 1. 7, 9 SET 2, SET 1

Khi chân này ở mức logic thấp, giá trị của ~Q sẽ là 1. 8 GND Cung cấp điện âm 16 Vdd Cung cấp điện tích cực

1.2.3. Thông số kỹ thuật

- Hoạt động với tốc độ trung bình 16 MHz với nguồn cung cấp 10V. 3

- Nhiệt độ hoạt động từ -55oC-125 C. o

- Nguồn cung cấp có dải điện áp từ -0.5-20V.

- Điện áp hoạt động: 5V, 10V, 15V.

- Điện áp hoạt động tối đa: 20V.

- Flip-Flop hoạt động tĩnh.

- Có khả năng set và reset.

- Công suất tiêu thụ thấp 50 nW.

- Thời gian tăng / giảm đầu vào ở 5V: 45us.

- Điện áp đầu vào mức cao tối thiểu: 2V.

- Điện áp đầu vào mức thấp tối đa: 0,8V.

- Có các gói PDIP, GDIP, PDSO 14 chân.

- Điện áp cao như 15V với biên độ nhiễu thấp chỉ 2,5V.

1.2.4. Nơi ứng dụng

CD4027IC được sử dụng để lưu dữ liệu và thực hiện các chức năng điều khiển,

thanh ghi dữ liệu và chuyển đổi dữ liệu. Trong ứng dụng bật tắt, nó được sử dụng để

thay đổi tín hiệu bằng các tín hiệu đầu vào điều khiển.

Cũng có thể sử dụng IC này trong các thiết bị chốt tín hiệu do đặc tính của nó là

lưu dữ liệu và xuất tín hiệu đầu ra dựa vào trạng thái logic đầu ra trước đó.

1.2.5. Cách sử dụng

CD4027 có hai flip flop, mỗi flip có bốn đầu vào độc lập và hai đầu ra ngược

tín hiệu nhau. Các chân đầu vào J và K điều khiển trạng thái logic flip flop khi có xung

cạnh tích cực cao của xung clock.

Chúng ta có thể cấp tín hiệu clock thông qua một nút nhấn hoặc tín hiệu PWM.

Các chân set và reset hoạt động độc lập với xung clock. Bắt đầu hoạt động bằng cách

cấp tín hiệu logic cao cho các chân này. Chân 8 được mắc với mass. Kết nối chân 16 với nguồn điện dương.

Đây là một sơ đồ mạch đơn giản cùng các tín hiệu điều khiển và xung clock. Có

thể thấy, tín hiệu reset và set được đặt bằng không. Do đó, các đầu ra trên chân Q và ~

Q phụ thuộc vào tín hiệu đầu vào JK.

1.2.6. Các ứng dụng

- Mạch bộ nhớ máy tính. 4

- Thanh ghi dịch có thể được thiết bằng vi mạch này vì chúng là các mạch logic

tuần tự và chủ yếu được sử dụng để lưu dữ liệu digital.

- Được sử dụng trong thanh ghi thoại (voice register) và thanh ghi bộ nhớ hoặc thanh ghi điều khiển

- Các mạch EEPROM để chứa một lượng nhỏ dữ liệu.

- Các linh kiện và bộ đếm chốt dữ liệu. 5

CHƯƠNG 2: SƠ ĐỒ KHỐI MẠCH THIẾT KẾ VÀ HOẠT ĐỘNG

CỦA CÁC KHỐI TRONG SƠ ĐỒ

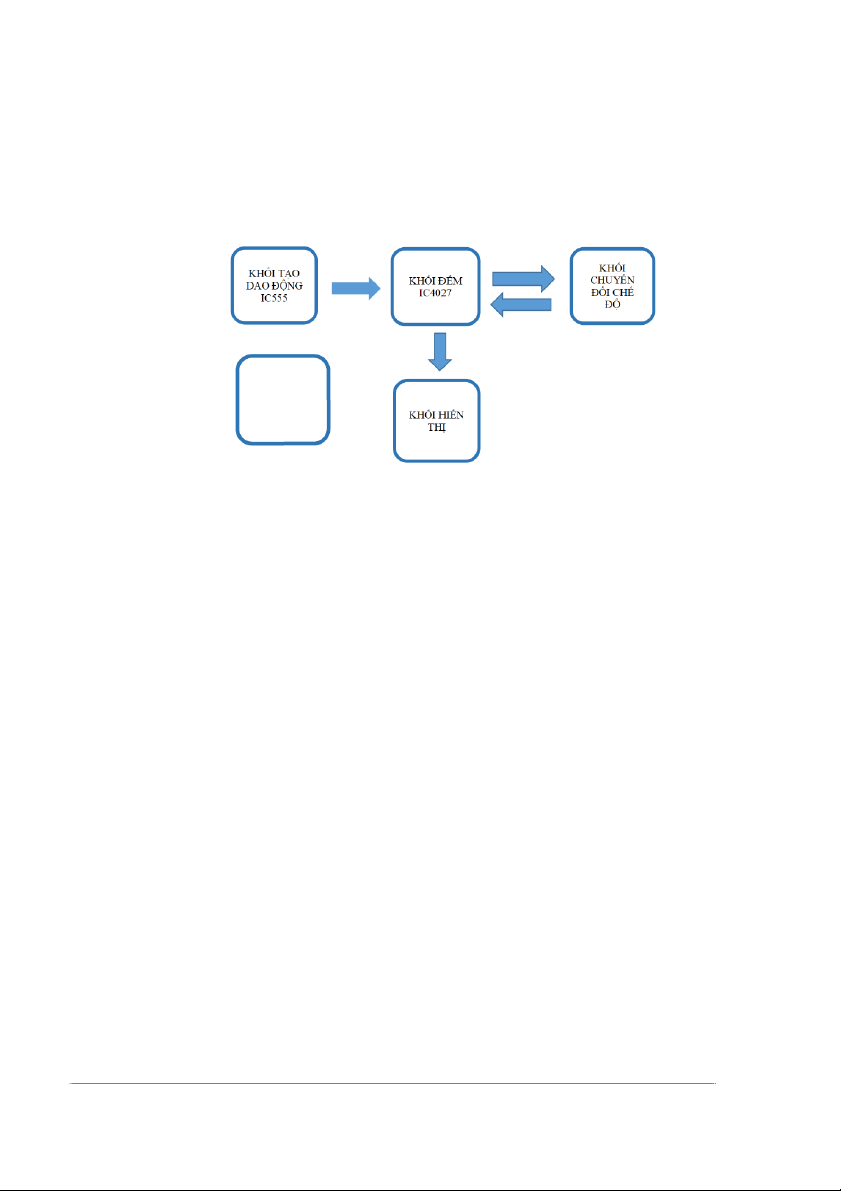

2.1. Sơ đồ khối của mạch thiết kế KHỐI NGUỒN

2.2. Hoạt động của các sơ đồ khối

Khối nguồn: cung cấp nguồn cho mạch dao động

Khối tạo dao động: Tạo

ra các xung Clock rồi đưa xung qua khối đếm, cụ thể

là được đưa vào flip flop đầu tiên của khối.

Khối đếm: Bao gồm các flipflop được nối tiếp với nhau. Khi có các xung kích

cạnh lên thì các khối này lập tức đếm lên từ trạng thái 000 đến FFF hoặc đếm xuống,

được mã hóa thành các bit nhị phân ra các chân.

Khối chuyển đổi chế độ: Sử dụng mô qt nút nhâ qn và mô qt con FF JK để chuyển

đếm lên, xuống. Khi mạch đang đếm lên mà ta nhấn nút nhấn thì mạch sẽ chuyển đổi

từ đếm 000 đến FFF thành từ FFF xuống 000 và ngược lại.

Khối hiển thị:Dùng Led 7 đoạn hiển thị ra các giá trị số đếm từ các mã nhị phân. 6

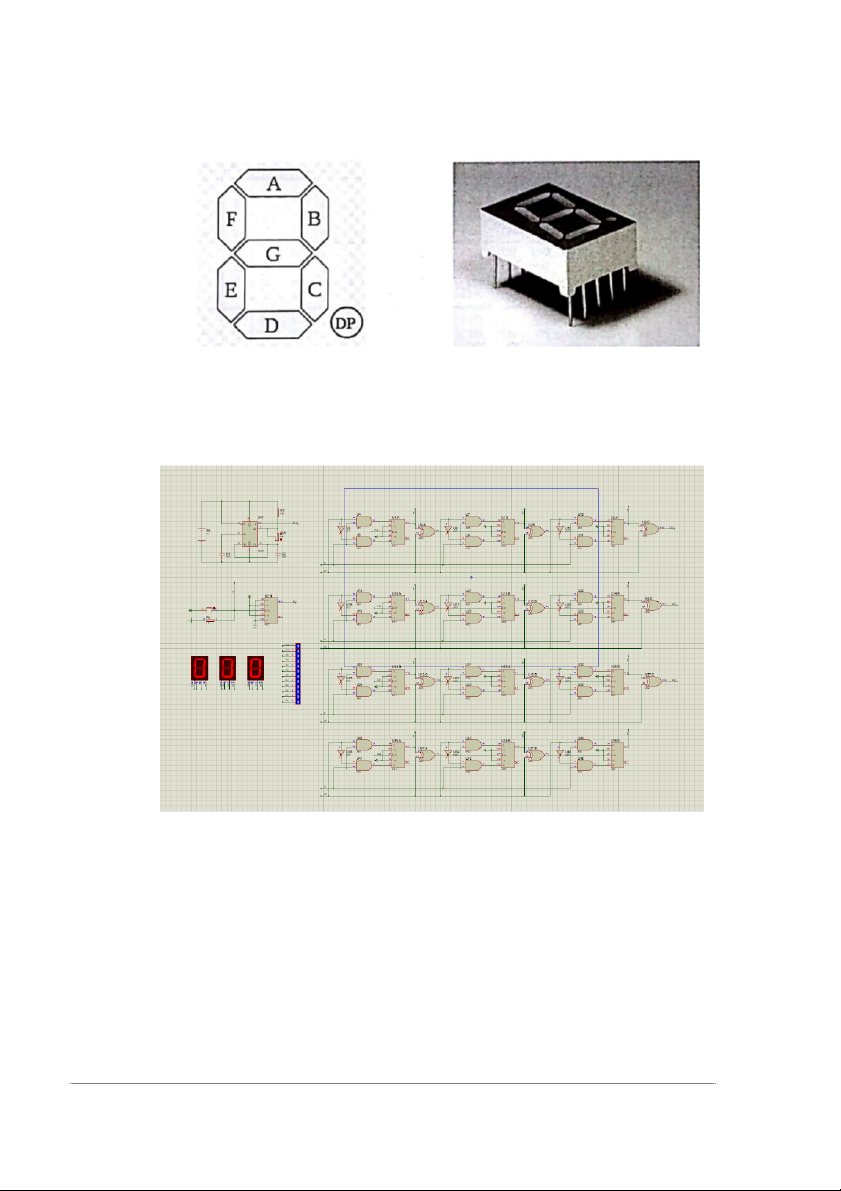

Hình 3: Kí hiệu và hình ảnh của led 7 đoạn

CHƯƠNG 3: MẠCH NGUYÊN Lz VÀ Lz DO CHỌN CÁC LINH

KIÊ{N, TÍNH TOÁN CÁC THÔNG SỐ TRONG MẠCH

3.1. Mạch nguyên lý:

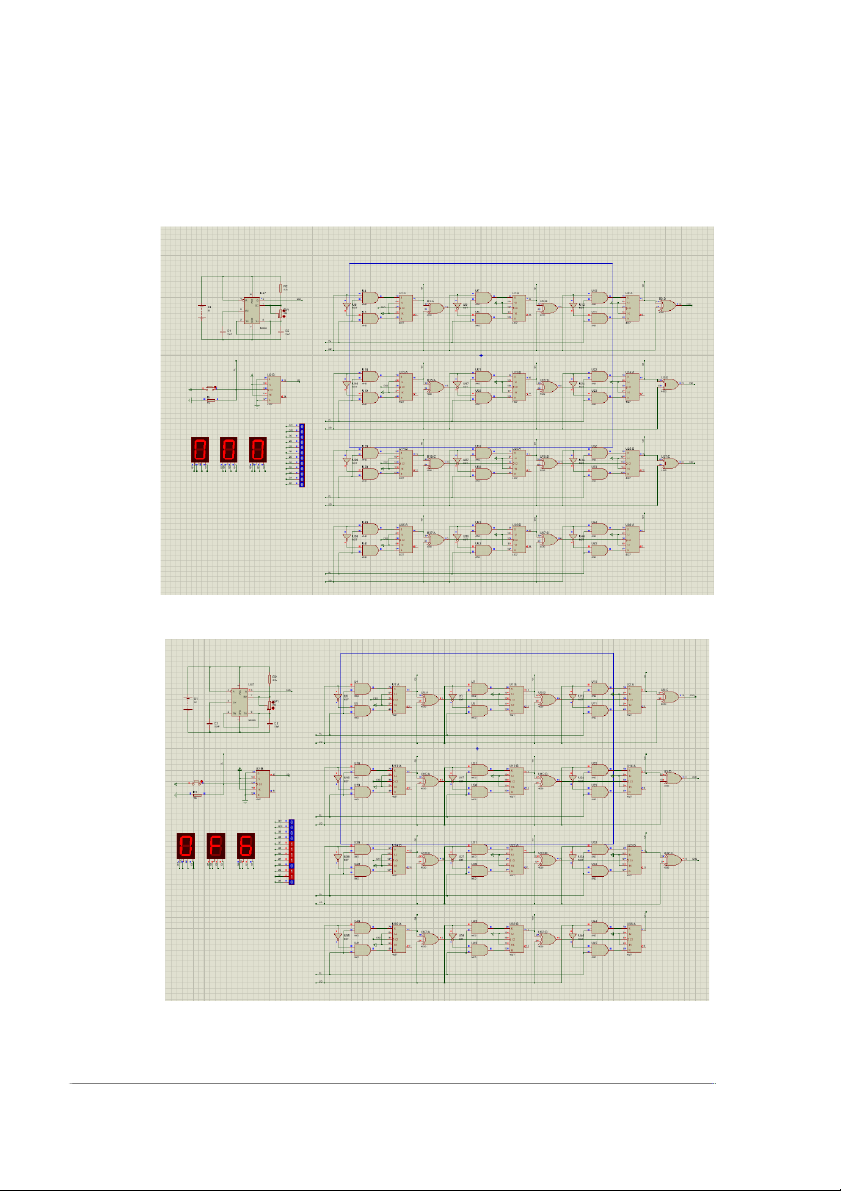

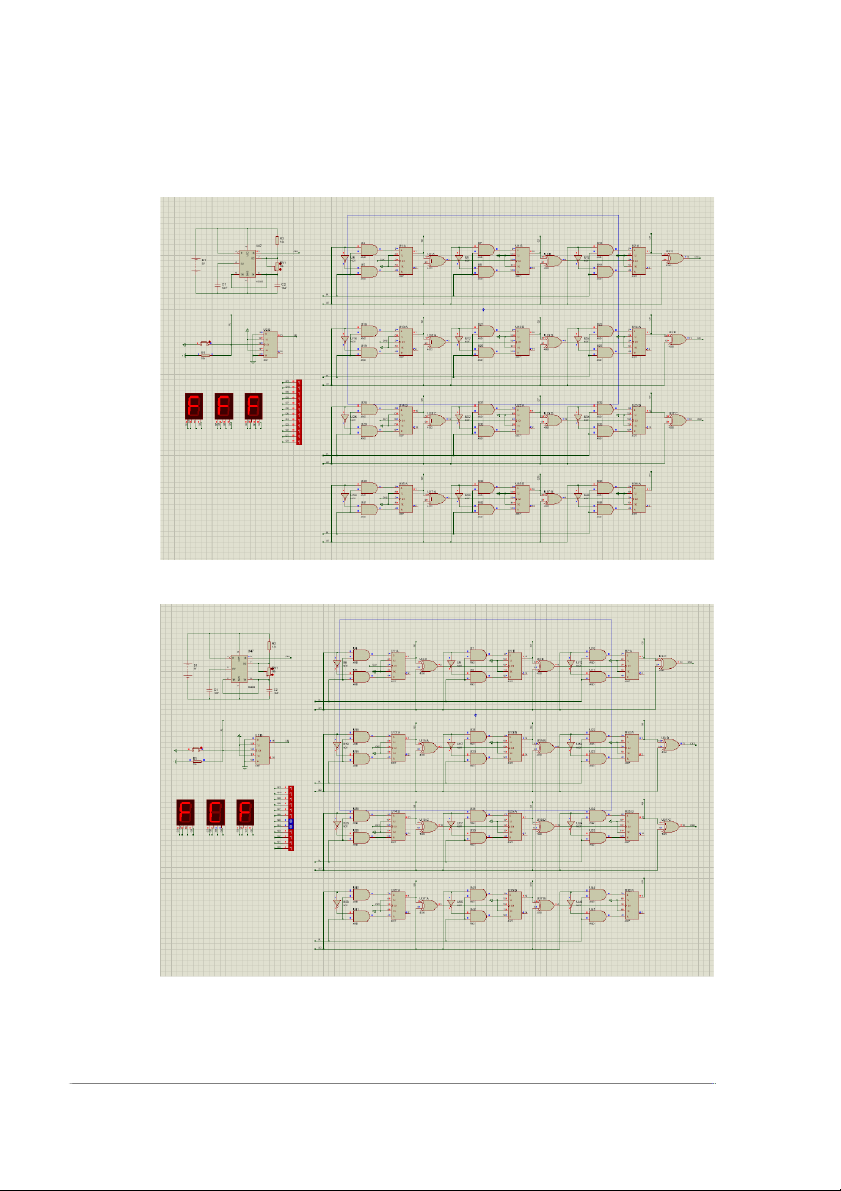

Hình 4: Sơ đồ nguyên lí mạch đếm 12 bit sử dụng IC 4027

3.2. Lý do chọn các linh kiện và tính toán các thông số trong mạch:

3.2.1. Khối tạo xung dao động:

Chức năng: Cấp xung clock cho thanh ghi

- Lựa chọn linh kiện và lý do chọn:

+ IC555 được ứng dụng rất phổ biến để tạo nên các mạch như: Mạch đơn ổn,

mạch dao dộng đa hài, mạch chia tần,…. 7

+ Có thể kết hợp với điện trở và tụ điện để tạo ra chu kì dao đông theo ý muốn.

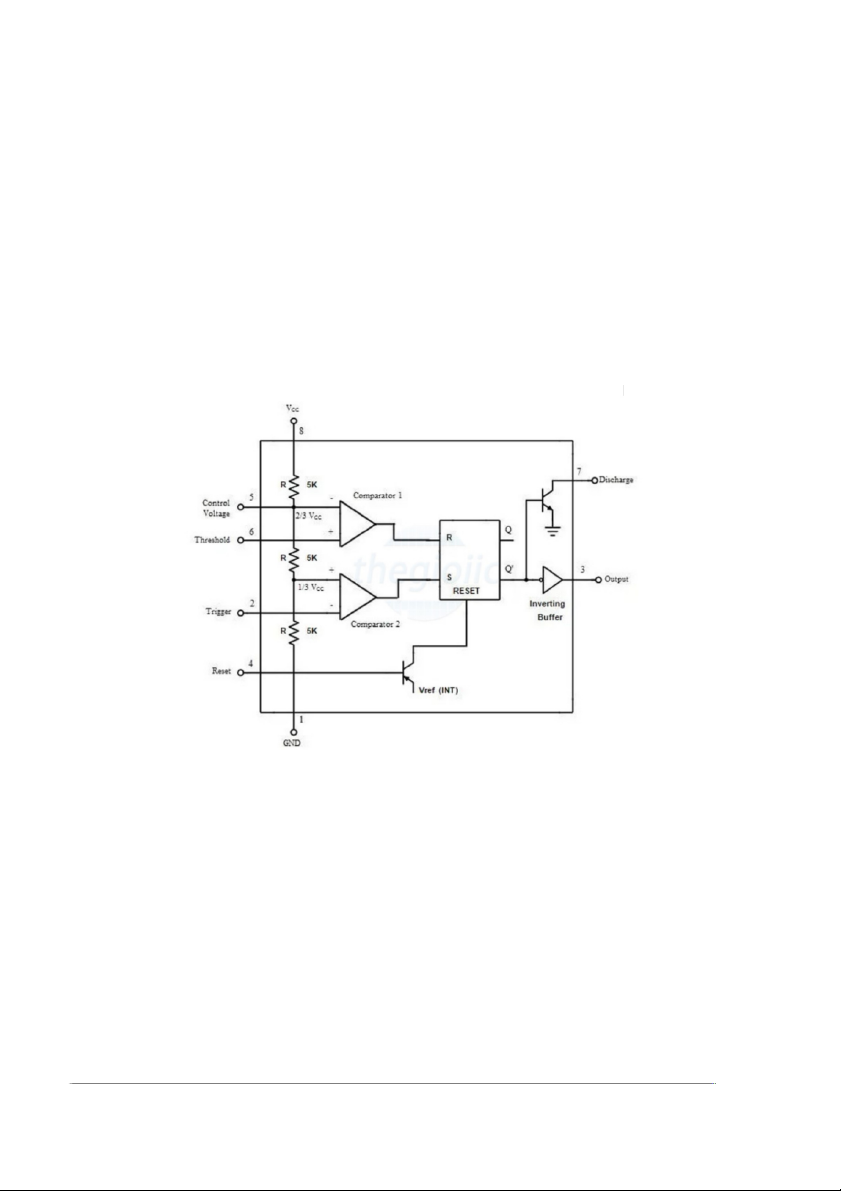

- Nguyên lý hoạt động:

Cấu tạo của NE555 gồm OP-amp so sánh điện áp, mạch lật và transistor để xả

điện. Cấu tạo của IC đơn giản nhưng hoạt động tốt. Bên trong gồm 3 điện trở mắc nối

tiếp chia điện áp VCC thành 3 phần. Cấu tạo này tạo nên điện áp chuẩn. Điện áp 1/3

VCC nối vào chân dương của Op-amp 1 và điện áp 2/3 VCC nối vào chân âm của Op-

amp 2. Khi điện áp ở chân 2 nhỏ hơn 1/3 VCC, chân S = [1] và FF được kích. Khi

điện áp ở chân 6 lớn hơn 2/3 VCC, chân R của FF = [1] và FF được reset

Hình 5: Cấu tạo của IC NE555

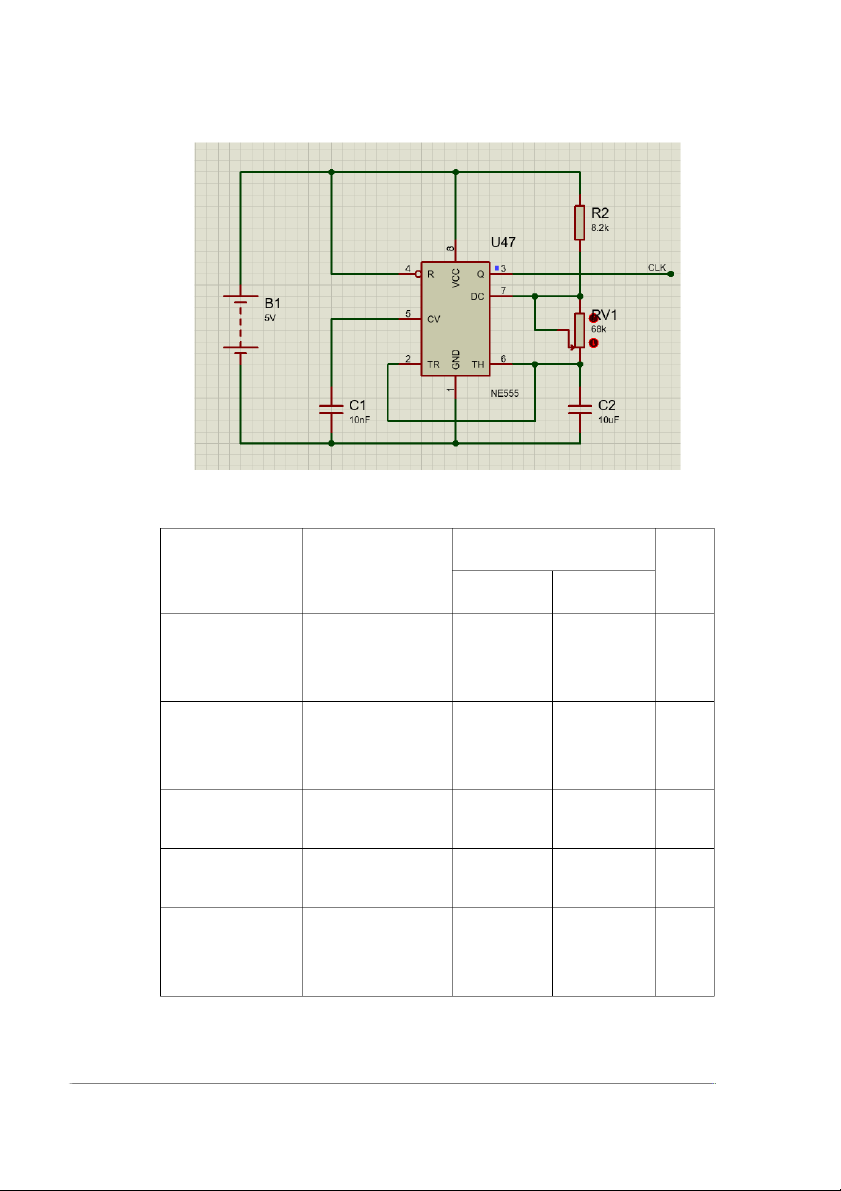

- Nhìn vào sơ đồ mạch trên ta có công thức tính tần số , độ rộng xung:

+ Tần số của tín hiệu đầu ra là: f = 1/(ln2.C.(R1 + 2R2))

+ Chu kì của tín hiệu đầu ra : t = 1/f

+ Thời gian xung ở mức H (1) trong một chu kì: t1 = ln2 .(R1 + R2).C

+ Thời gian xung ở mức L (0) trong 1 chu kì: t2 = ln2.R2.C 8

Hình 6: Mạch mô phỏng tạo xung

- Tính toán các thông số trong mạch: Kết quả Tham số Công thức Đơn vị RV1 = 0 Ω RV1 = 68k Ω

Thời gian nhưng ln(2) × (R3 + RV1) × dẫn ở mức áp cao 0.057 0.528 Giây C2 (Tn) Thời gian nhưng dẫn ở mức áp thấp ln(2) × RV1 × C2 0 0.471 Giây (Tx) Khoảng thời gian ln(2) × (R3 + 2 × 0.057 1 Giây (T) RV1) × C2 1 / ((R3 + 2 × RV1) Hertz Tần số (F) 17.594 1 × C2 × ln(2)) (Hz) Phần Chu kỳ xung (Tn / T) × 100 100 52.8 trăm (%) 9

3.2.2. Khối đếm IC4027

- Chức năng: Đếm lên/xuống theo mã nhị phân 12 bit

- Lý do lựa chọn linh kiê qn: Để có thể đáp ứng cho yêu cầu là khởi tạo mạch

đếm lên/xuống có thể hoạt đô qng thì nhóm chúng em chọn JK Flip Flop cụ thể là IC CD4027 - Chức năng các chân:

+ Chân CLK: chân nhận xung clock của IC. Để IC có thể hoạt động thì phải có

xung clock đưa vào chân này. Xung clock sẽ được tạo ra bởi khối tạo dao động chính

là IC NE555 và ngõ ra của khối tạo dao động sẽ được kết nối với ngõ vào xung CK của IC CD4027

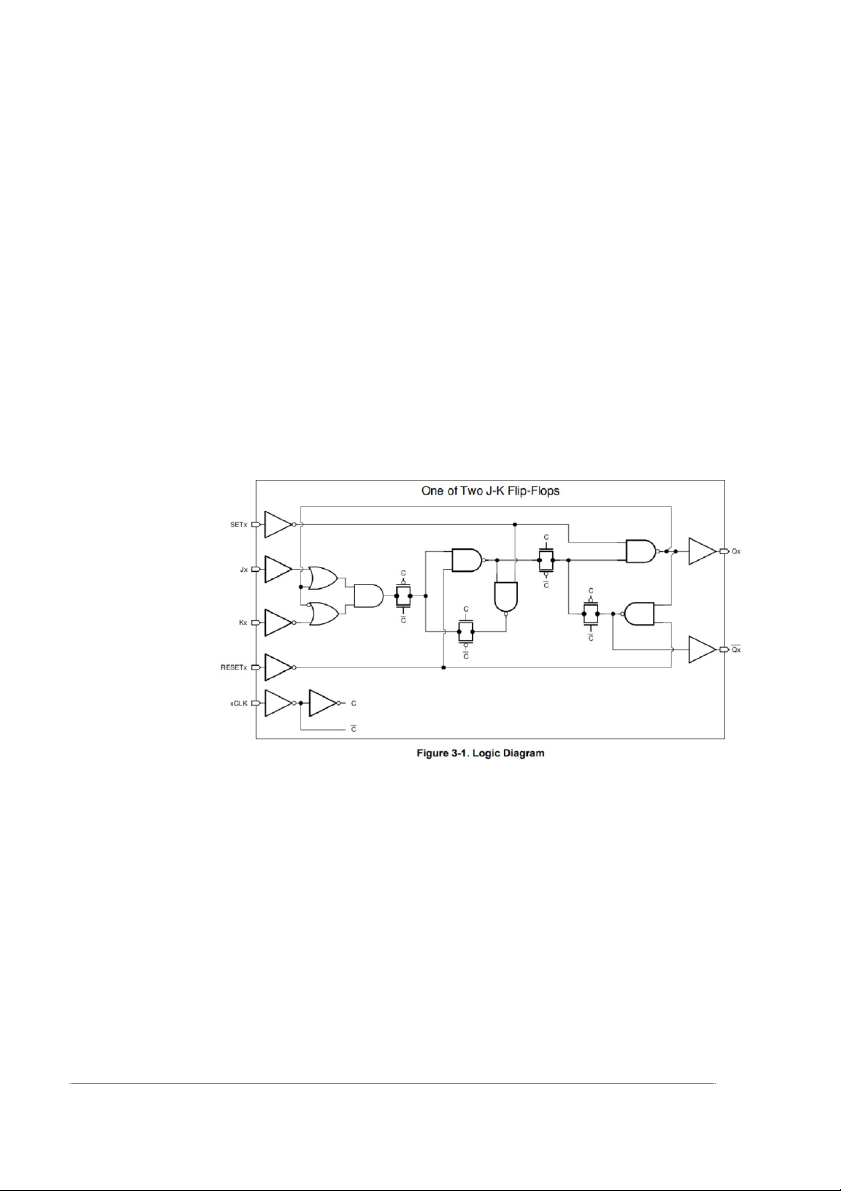

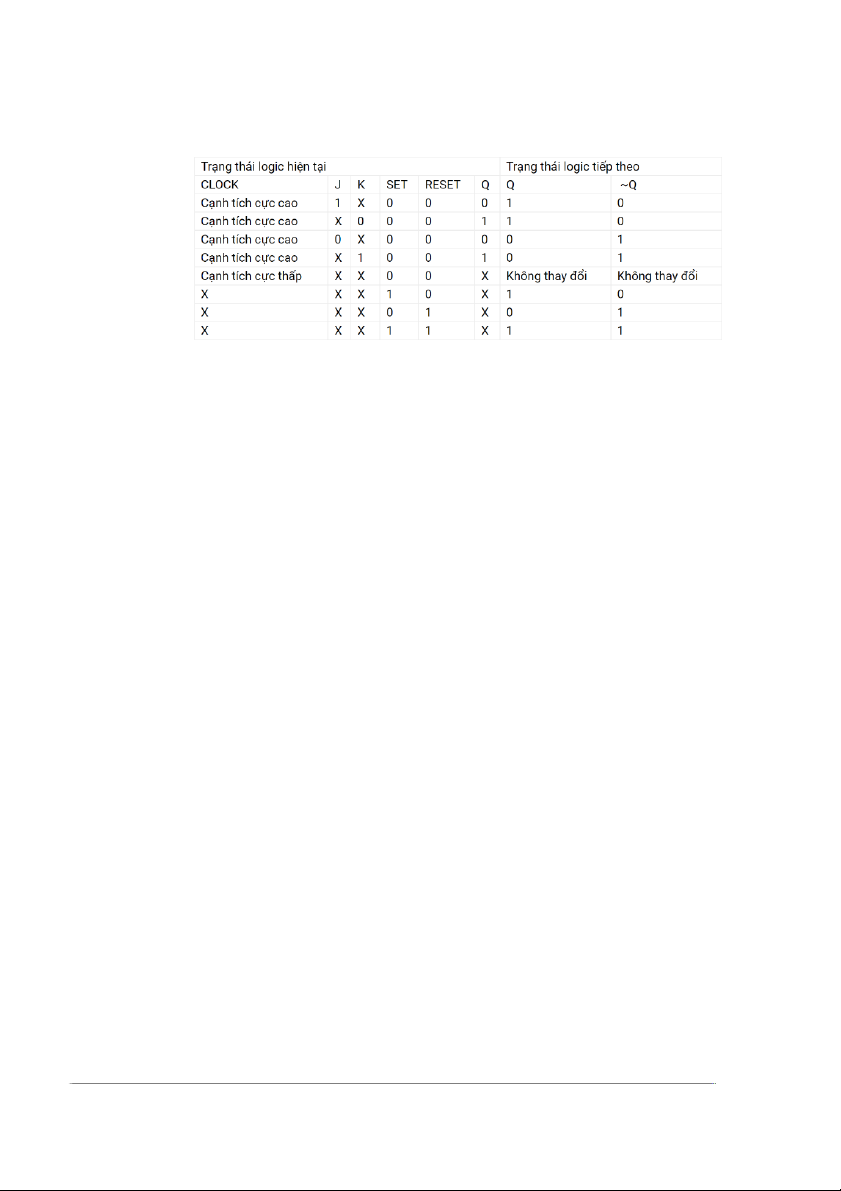

- Sơ đồ logic của từng chân: - Bảng trạng thái 10

+Khi chân RESET ở mức thấp, chân PRE ở mức thấp, CK tích cực cao, J ở

mức 1 thì ngõ ra Q được set lên mức 1

+Khi chân RESET ở mức thấp, chân PRE ở mức thấp, CK tích cực cao, K ở

mức 0 thì ngõ ra Q được set lên mức 1

+Khi chân RESET ở mức thấp, chân PRE ở mức thấp, CK tích cực cao, J ở

mức 0 thì ngõ ra Q được reset về mức 0

+Khi chân RESET ở mức thấp, chân PRE ở mức thấp, CK tích cực cao, K ở

mức 1 thì ngõ ra Q được reset về mức 0

+Khi chân RESET ở mức thấp, chân PRE ở mức thấp, CK tích cực thấp thì ngõ

ra Q sẽ không đổi so với trạng thái trước.

+Khi chân RESET ở mức thấp, chân PRE ở mức cao thì ngõ ra Q được set lên 1.

+Khi chân RESET ở mức cao, chân PRE ở mức thấp thì ngõ ra Q bị reset về 0.

+Khi chân RESET ở mức thấp, chân PRE ở mức thấp thì ngõ ra Q nhận trạng thái cấm.

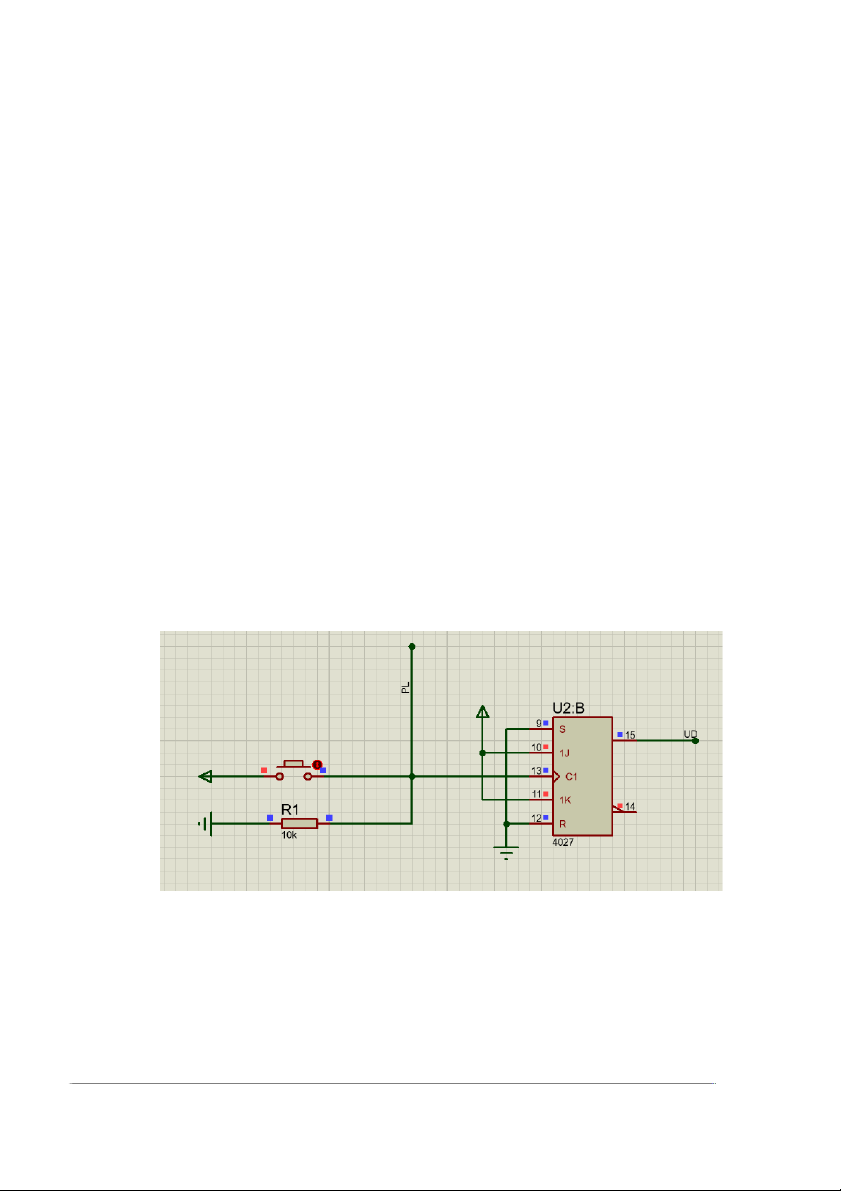

3.2.3. Khối chuyển đổi hai chế độ

Theo yêu cầu đề tài, mạch cần hoạt động theo 2 chế độ là đếm lên và đếm

xuống điều khiển bằng nút nhấn.

- Chức năng: chuyển đổi qua lại giữa 2 chế độ hiển thị. - Lý do lựa chọn:

IC CD4027 là IC Flip-Flop kép, có tính năng của JK, mỗi flip có bốn đầu vào

độc lập và hai đầu ra ngược tín hiệu nhau. Các chân đầu vào J và K điều khiển trạng

thái logic flip flop khi có xung cạnh tích cực cao của xung clock. Yêu cầu cần chuyển 11

2 chế độ nên chọn IC CD4027 sẽ giúp mạch chuyển đổi qua lại 2 chế độ bằng trạng

thái đảo của Flip-Flop JK. - Cơ chế hoạt động:

Để mạch có thể hoạt động ở 2 chế độ như yêu cầu đề tài ta cần kết hợp hai

mạch đếm lên và đếm xuống. Phương pháp thực hiện như sau:

Gọi tín hiê qu điều khiển đếm lên/xuống là UD với UD = 1 đếm lên và UD = 0 mạch đếm xuống

- Đếm lên : Qn đảo nối với Ckn+1

- Đếm xuống: Qn nối với Ckn+1 Hàm tổng Ck0= Ck Ckn+1 = Qn ⊕ UD Ví dụ:

Khi đếm lên xung Ck = 1, UD = 0 (chưa nhấn nút) Ck1 = Q . UD + Q 0 . UD = 1.1 + 0.0 =1 0

Khi đếm xuống Ck = 1, UD = 1 (nhấn nút)

Ck1= Q0 . UD + Q0. UD = 1.0 + 0.1= 0

Hình 7: Mạch chứa nút nhấn điều khiển lên xuống

Các chân J, K được mắc lên mức logic 1 còn các chân Pre và Clr được nối đất mức logic 0. 12

Chân CLK được nối với nguồn (mức logic 1) và khi bấm nút thì CLK sẽ được

nối đất (mức logic 0) thì sinh ra một xung truyền thẳng vào chân CLK làm đảo ngược

trạng thái hiện tại của ngõ ra Q. Từ đó làm thay đổi mức logic của tín hiệu UD trong

mạch đếm khiến cho mạch đếm thay đổi trạng thái đếm.

3.2.4. Khối hiển thị

- Chức năng: Hiển thị kết quả đầu ra - Lý do lựa chọn:

+ Sử dụng 12 đầu dò logic nối trực tiếp với 12 đầu ra vì cho kết quả rõ nét, độ sáng dễ nhìn .…

+ Để đáp ứng nhu cầu hiển thị kết quả đầu ra dưới dạng nhị phân thông qua led

ứng với màu đỏ là mức logic 1 còn màu xanh là mức logic 0. - Thông số kỹ thuật: + Tests TTL, and CMOS + Tần số DC: 20MHz

+ Logic 1 (đèn LED đỏ): 2.3V +0.2V

+ Logic 0 (đèn LED xanh): 0.8V +0.2V

+ Bảo vệ quá tải đầu vào: 220Vac/DC (15 sec.)

+ Trở kháng đầu vào: 1MΩ 13

CHƯƠNG 4: MÔ PHỎNG MẠCH TRÊN PHẦN MỀM PROTUES

- Khi xung Ck kích cạnh vào Ic4027( chưa cần nhấn nút). Mạch bắt đầu đếm lên từ 000

- Mạch bắt đầu đếm lên 14

- Khi đếm tới FFF, ta nhấn nút nhấn, mạch sẽ chuyển từ trạng thái đếm lên sang đếm xuống

- Mạch tiếp tục đếm xuống 15