Preview text:

lOMoAR cPSD| 61549570 Bài báo cáo lab_3

Thực hành điện tử CNTT cho LAB

Họ và tên: Ngô Hoàng Phúc MSSV: 20225903

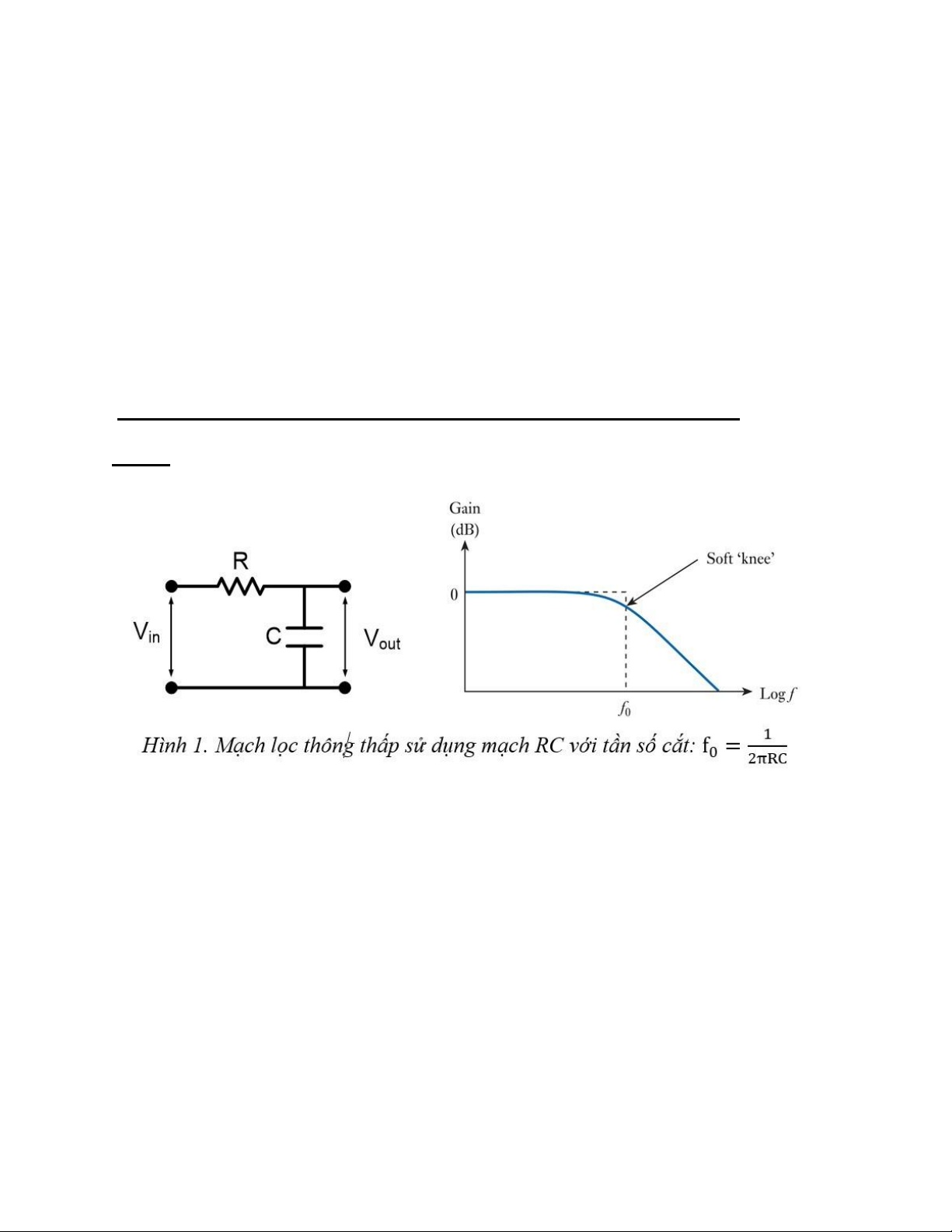

Bài 1: Khảo sát tính chất các mạch lọc RC thông thấp và thông cao đơn giản.

- Giá trị các dữ liệu linh kiện sử dụng: R ≈ 1 (kΩ), C ≈ 1 (μF). a) lOMoAR cPSD| 61549570

Kết quả đo mạch lọc thông thấp: Lần đo V out thực tế V out lí thuyết (V) (V) 10 Hz 4.75 4.975 lOMoAR cPSD| 61549570 100 Hz 4.5 4.203 1 kHz 0.5 0.783 10 kHz ~0 0.079 100 kHz ~0 0.008 Nhận xét:

-Kết quả đo của Vout tương đối sát so với Vout tính lí thuyết

=> Mạch lắp đã mô phỏng lại được mạch lọc thông thấp

-Tần số cắt f0 = 159.15Hz

-Khi tần số tăng dần từ 10Hz đến 100kHz, Vout giảm từ xấp xỉ V in xuống còn xấp xỉ 0.

-Tín hiệu ổn định ở tần số f < f0 ~159.15Hz

Điều này phản ánh tính chất của mạch lọc thông thấp, nơi nó cho phép

tín hiệu ở các tần số thấp hơn truyền qua mạch mà không bị suy giảm đáng kể.

=>Mạch lọc hoạt động tốt ở tần số thấp.

-Tần số Vin để sao cho: = Bi ê n độ Vout Bi ê n độ Vin

thực hành đo đạc là: ≈ 150Hz. -Với công thức:

2π RCta tính theo lý thuyết được f ≈ 159.15 Hz

-Với mạch lọc thông thấp RC, độ dịch pha của Vout so với Vin được tính theo công thức:

φ= −arctan(2πfRC) ≈ -45° lOMoAR cPSD| 61549570

-Ở tần số của Vin mà: Bi ê n độ Vout = Bi ê n độ Vin

sử dụng máy hiển thị song ta xác định được

độ dịch pha của φ là -45,25°

+ Tần số f ≈ 150 Hz -> Chu kì T = 1 1 f =150 = 6.67× 10-3 s + ∆t ≈ 8.4 × 10-4

+ Độ dịch pha: ∆ = ϕ − ∆t

T ×360° ≈ -45,25°

⟹ Nhận xét: Kết quả đo đạc xấp xỉ mới kết quả tính toán theo lý

thuyết, sự sai số này do ảnh hưởng bởi sai số dụng cụ và sai số ngẫu

nhiên mỗi lần đo. (do làm tròn trong quá trình đo và tính toán , hao tồn

trên R và C , nhiễu đường truyền…) b) lOMoAR cPSD| 61549570

Kết quả đo mạch lọc thông cao: lOMoAR cPSD| 61549570 Lần đo V out thực tế V out lí thuyết (V) (V) 10 Hz 0.25 0.314 100 Hz 2.5 2.66 1 kHz 4.5 4.9287 10 kHz 5 4.9975 100 kHz 5 4.9985 Nhận xét:

-Kết quả đo của Vout tương đối sát so với Vout tính lí thuyết

=> Mạch lắp đã mô phỏng lại được mạch lọc thông cao

-Tần số cắt f0 = 159.15Hz

- Khi tần số tăng dần từ 10Hz đến 100kHz, V out tăng dần từ xấp xỉ 0 đến xấp xỉ V in.

- Tín hiệu ổn định ở tần số f > f0 ~159.15Hz

Điều này phản ánh tính chất của mạch lọc thông cao, nơi nó cho phép tín

hiệu ở các tần số cao hơn truyền qua mạch mà không bị suy giảm đáng kể.

=> Mạch lọc hoạt động tốt ở tần số cao Tần số Vin để sao cho: = Bi ê n độ Vout Bi ê n độ Vin

thực hành đo đạc là: ≈ 150Hz. -Với công thức:

2π RCta tính theo lý thuyết được f ≈ 159.15 Hz

-Với mạch lọc thông cao RC, độ dịch pha của Vout so với Vin được tính theo công thức: lOMoAR cPSD| 61549570

φ= −arctan(1/(2πfRC)) ≈ -90°

-Ở tần số của Vin mà: Bi ê n độ Vout = Bi ê n độ Vin

sử dụng máy hiển thị song ta xác định được

độ dịch pha của φ là -90,25°

+ Tần số f ≈ 150 Hz -> Chu kì T = 1 1 f =150 = 6.67× 10-3 s + ∆t ≈ 1.67 × 10-3

+ Độ dịch pha: ∆ = ϕ − ∆t

T ×360° ≈ -90,25°

⟹ Nhận xét: Kết quả đo đạc xấp xỉ mới kết quả tính toán theo lý thuyết,

sự sai số này do ảnh hưởng bởi sai số dụng cụ và sai số ngẫu nhiên mỗi

lần đo. (do làm tròn trong quá trình đo và tính toán , hao tồn trên R và

C , nhiễu đường truyền…)

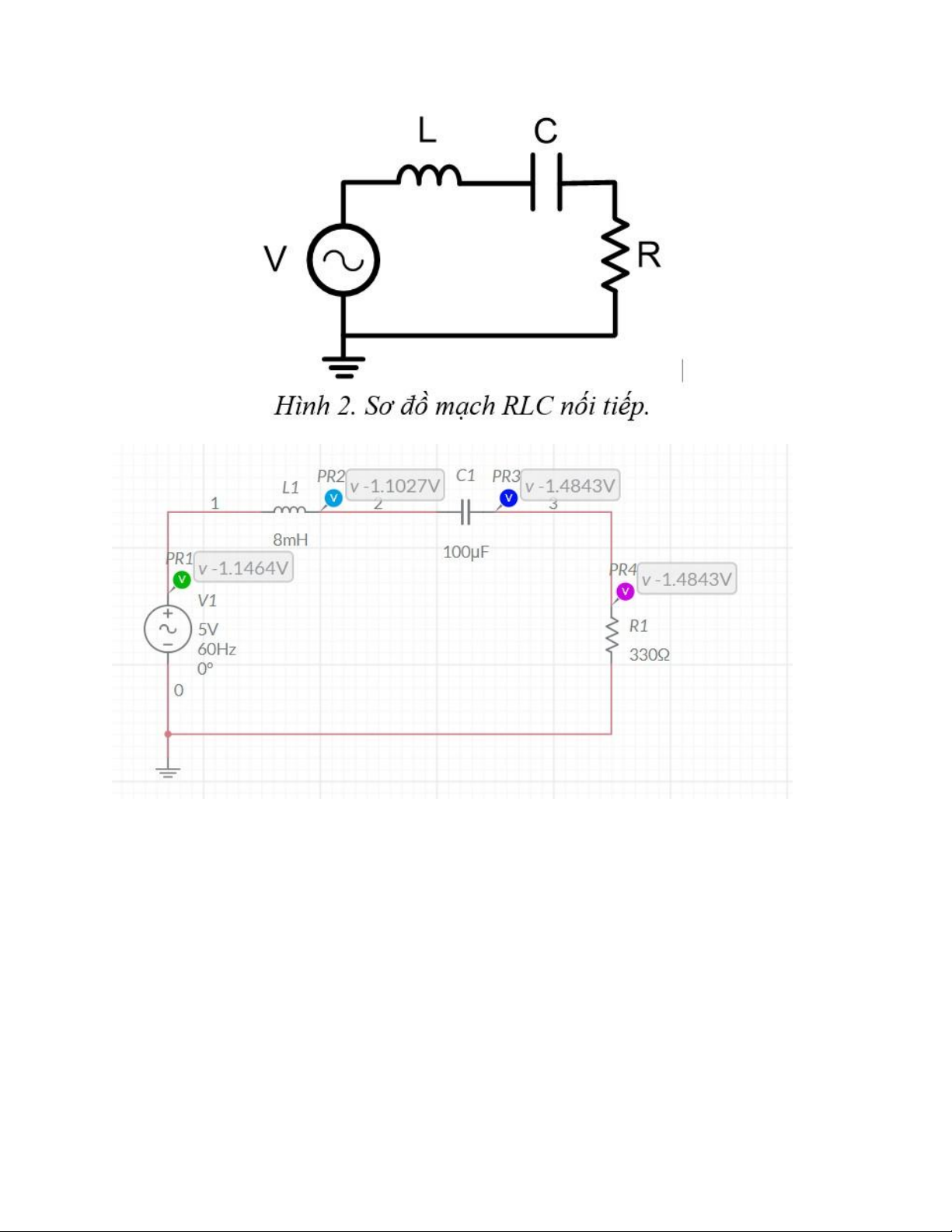

Bài 2: Sử dụng công cụ Multisim Live (https://www.multisim.com/) để

khảo sát tính chất các mạch lọc RLC nối tiếp. lOMoAR cPSD| 61549570

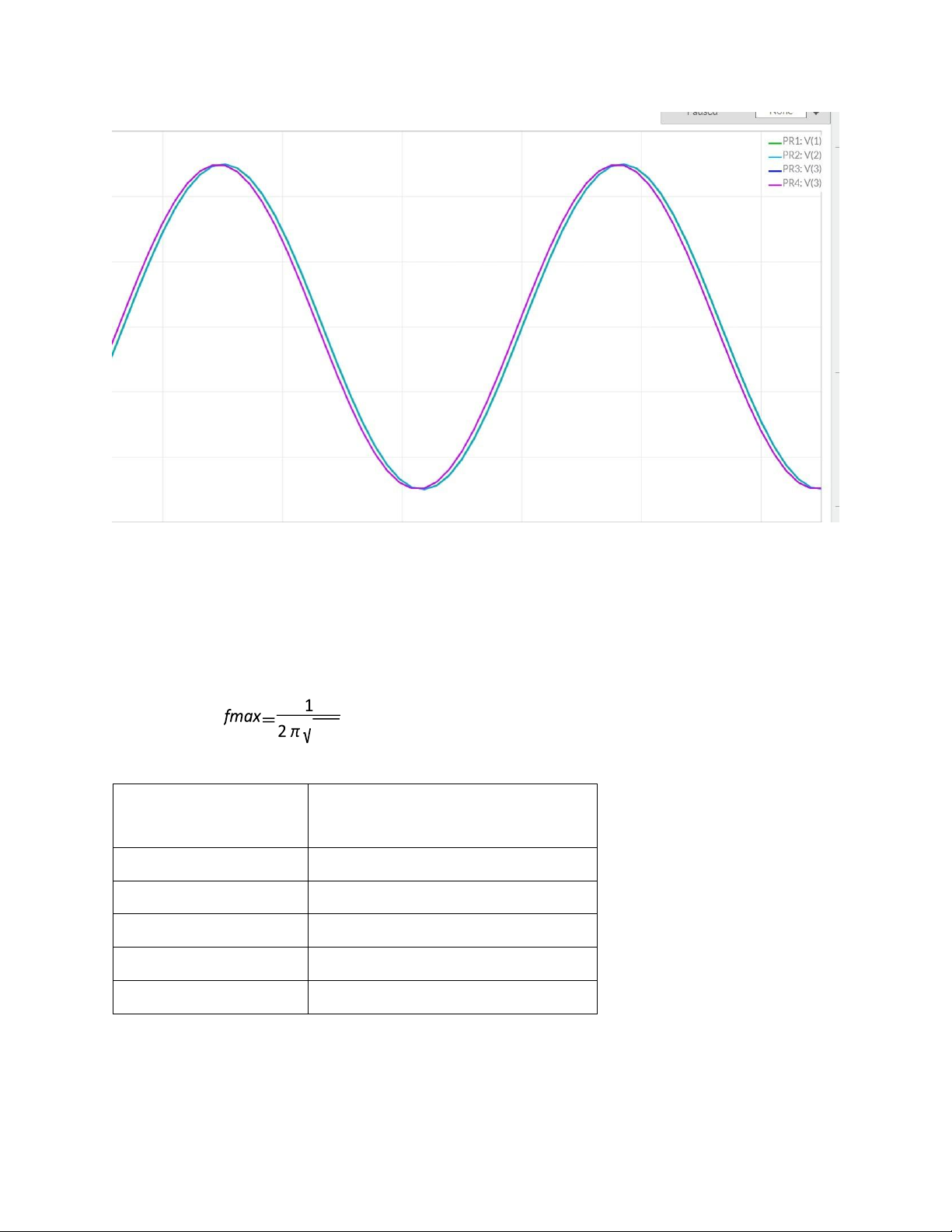

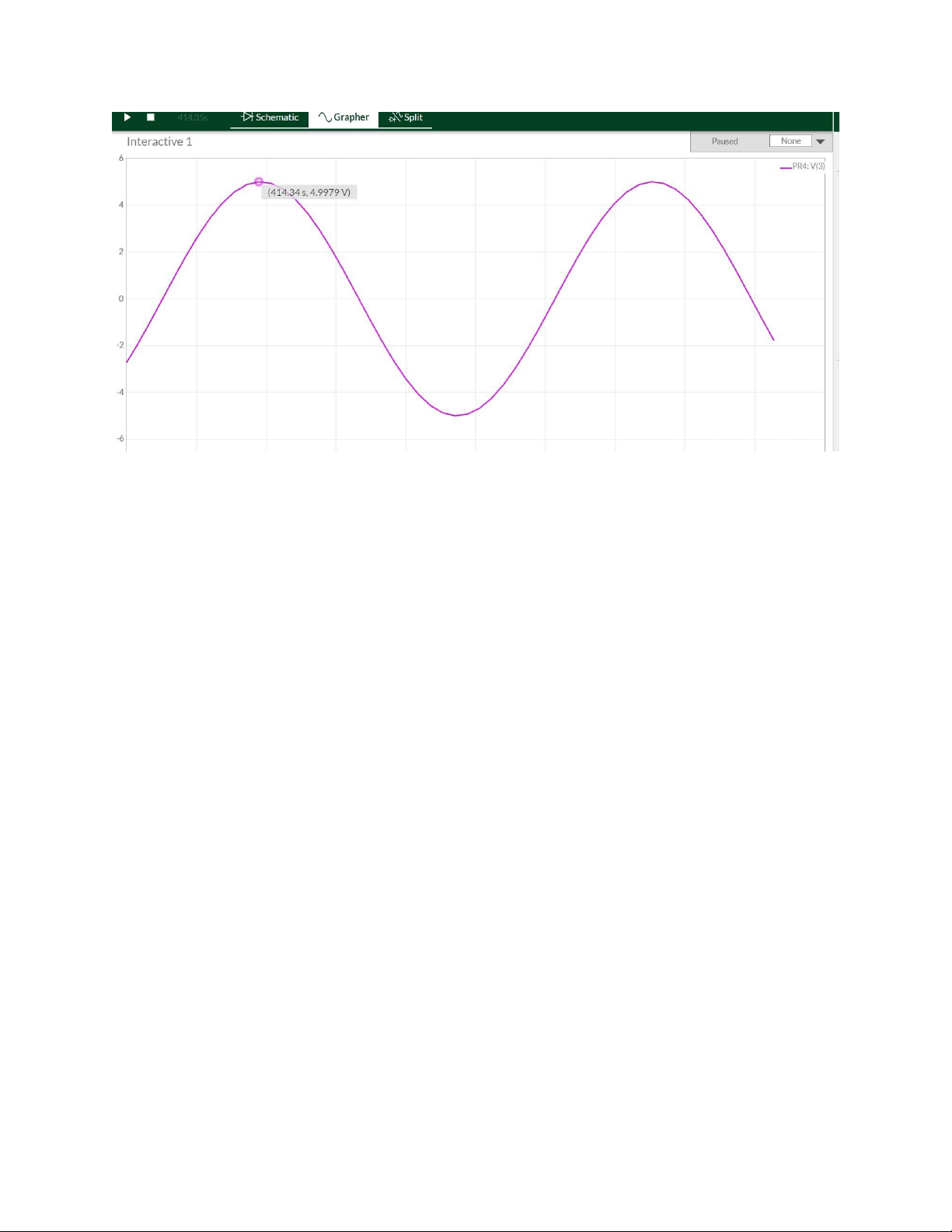

Graph xác định độ lệch pha của VR, VL, VC so với V: lOMoAR cPSD| 61549570 Lý thuyết RC = 177.9 Hz Kết quả đo: Lần đo VRmax (V) 10 Hz 4.4962 100 Hz 4.9914 1 kHz 4.9459 10 kHz 2.7384 177.9Hz 4.9979 lOMoAR cPSD| 61549570 Nhận xét:

-Giá trị của f càng gần với fmax lí thuyết thì VR càng lớn.