Preview text:

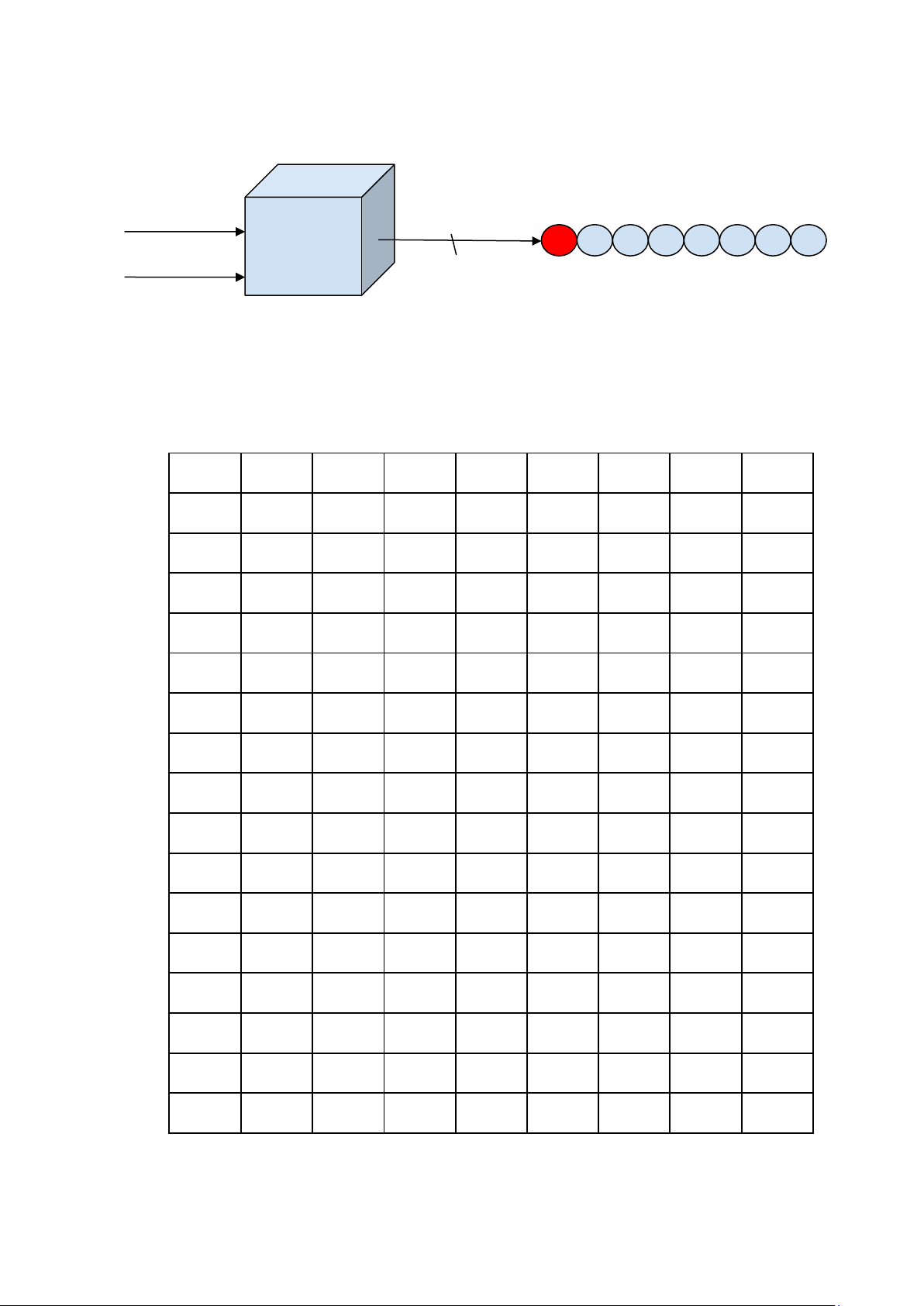

lOMoAR cPSD| 58815430 I. Bài 1: 1. Sơ đồ khối clk 8 leds rst Bộ đếm x 2. Nguyên lý

- Mã Johnson là một loại mã hóa dạng nhị phân. Mã Johnson được tạo ra bằng cách sử

dụng một dãy bit 0 và 1 sao cho chỉ có một bit thay đổi giá trị tại mỗi bước, tạo ra một chu kỳ dịch chuyển.

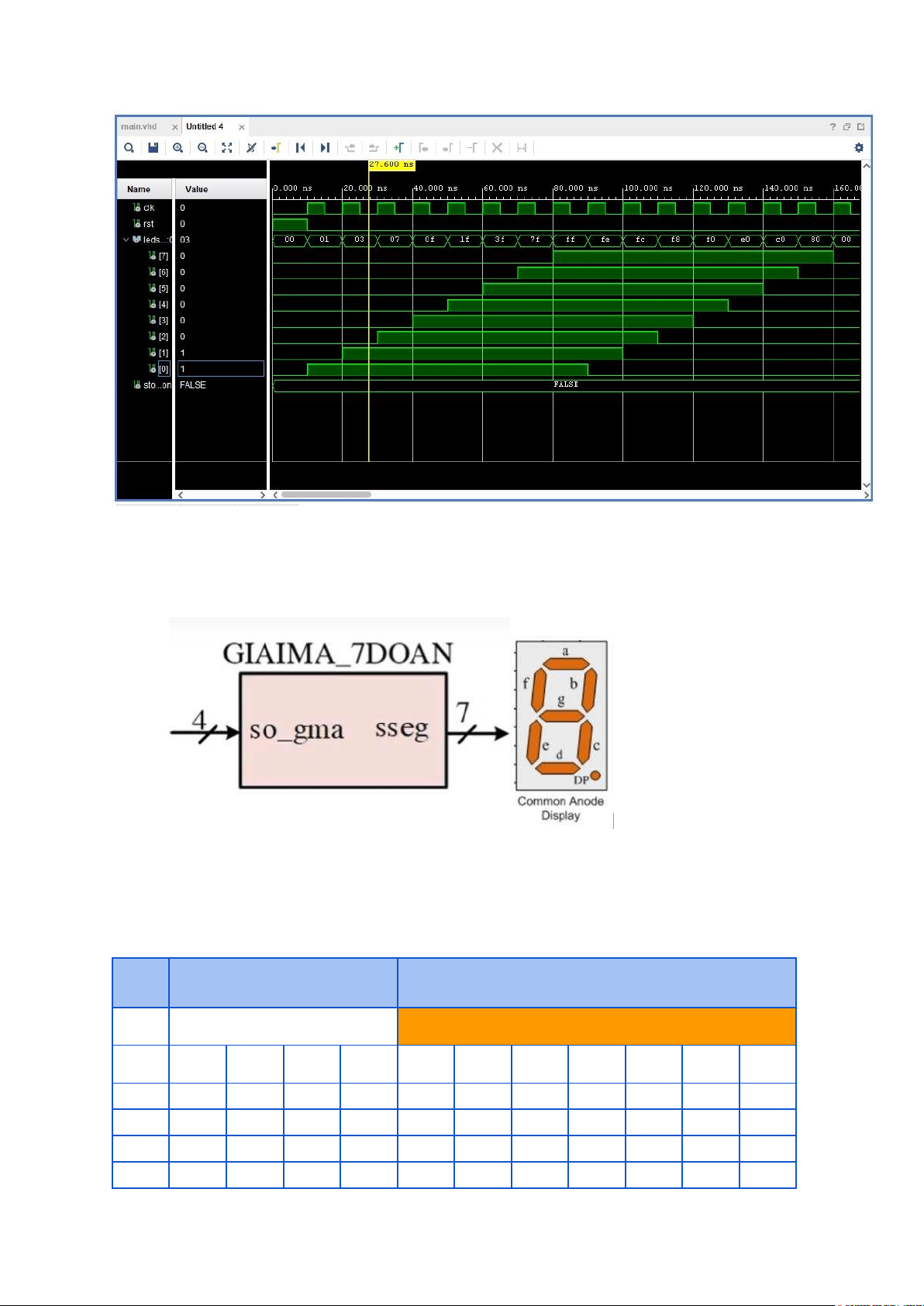

- Dãy mã Johnson 8-bit được biểu diễn như sau: clk led7 led6 led5 led4 led3 led2 led1 led0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 2 0 0 0 0 0 0 1 1 3 0 0 0 0 0 1 1 1 4 0 0 0 0 1 1 1 1 5 0 0 0 1 1 1 1 1 6 0 0 1 1 1 1 1 1 7 0 1 1 1 1 1 1 1 7 1 1 1 1 1 1 1 1 9 1 1 1 1 1 1 1 0 10 1 1 1 1 1 1 0 0 11 1 1 1 1 1 0 0 0 12 1 1 1 1 0 0 0 0 13 1 1 1 0 0 0 0 0 14 1 1 0 0 0 0 0 0 15 1 0 0 0 0 0 0 0 lOMoAR cPSD| 58815430

- Trong dãy mã Johnson 8-bit này, chỉ có một bit thay đổi giá trị tại mỗi bước. Khi dãy

này dịch chuyển qua một chu kỳ, nó sẽ trở lại giá trị ban đầu, tạo thành một chu kỳ lặp lại.

- Sử dụng mã Johnson để điều khiển 8 LED theo chuỗi mã Johnson 8-bit, mỗi LED

biểu thị một bit trong dãy mã Johnson. Mỗi khi chu kỳ clock qua, dãy mã Johnson

được dịch chuyển một bit sang phải, tạo ra hiệu ứng nháy đèn theo mã Johnson. 3. Quá trình thực hiện - Main library IEEE;

use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity main is Port ( clk : in STD_LOGIC; rst : in STD_LOGIC;

leds : out STD_LOGIC_VECTOR (7 downto 0)); end main;

architecture Behavioral of main is begin process(clk,rst)

variable x:integer range 0 to 15; begin if rst='1' then x:=0; elsif rising_edge(clk) then if x=15 then x:=0; else x:=x+1; end if; end if; case x is

when 0 => leds<= "00000000";

when 1 => leds<= "00000001"; when 2 =>

leds<= "00000011"; when 3 => leds<=

"00000111"; when 4 => leds<= "00001111";

when 5 => leds<= "00011111"; when 6 =>

leds<= "00111111"; when 7 => leds<=

"01111111"; when 8 => leds<= "11111111";

when 9 => leds<= "11111110"; when 10 =>

leds<="11111100"; when 11 =>

leds<="11111000"; when 12 => leds<="11110000"; lOMoAR cPSD| 58815430

when 13=> leds<= "11100000";

when 14 => leds<="11000000";

when 15 => leds<="10000000"; end case; end process; end Behavioral; - Testbench library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use IEEE.NUMERIC_STD.ALL;

entity testbech is end testbech;

architecture Behavioral of testbech is COMPONENT main Port ( clk : in STD_LOGIC; rst : in STD_LOGIC;

leds : out STD_LOGIC_VECTOR (7 downto 0)); END COMPONENT; SIGNAL clk : std_logic:='0'; SIGNAL rst : std_logic:='0';

SIGNAL leds : std_logic_vector(7 downto 0);

signal stop_simulation : BOOLEAN; begin uut: main PORT MAP( clk => clk , rst => rst, leds => leds ); process begin rst <= '1'; wait for 10 ns; rst <= '0';

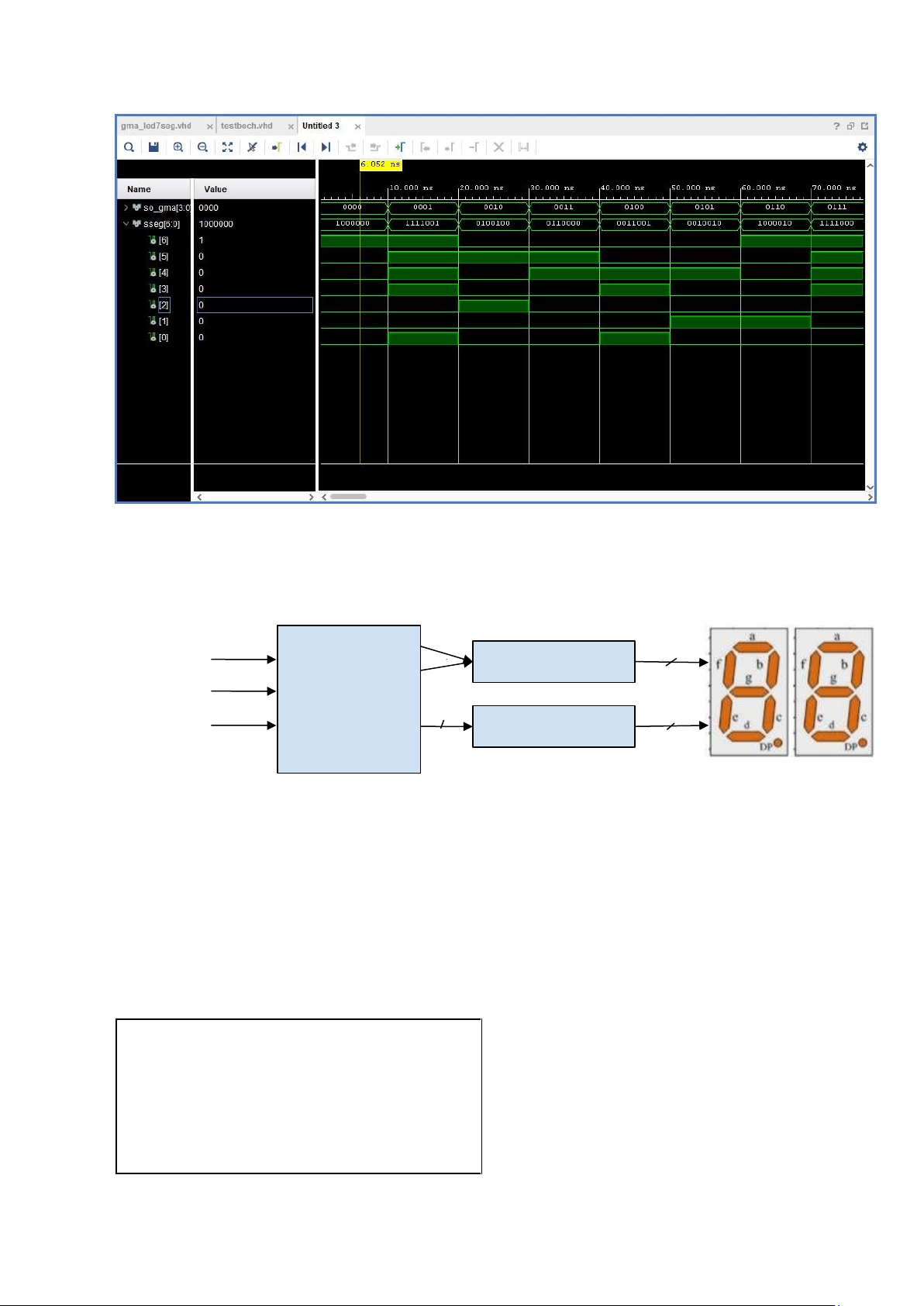

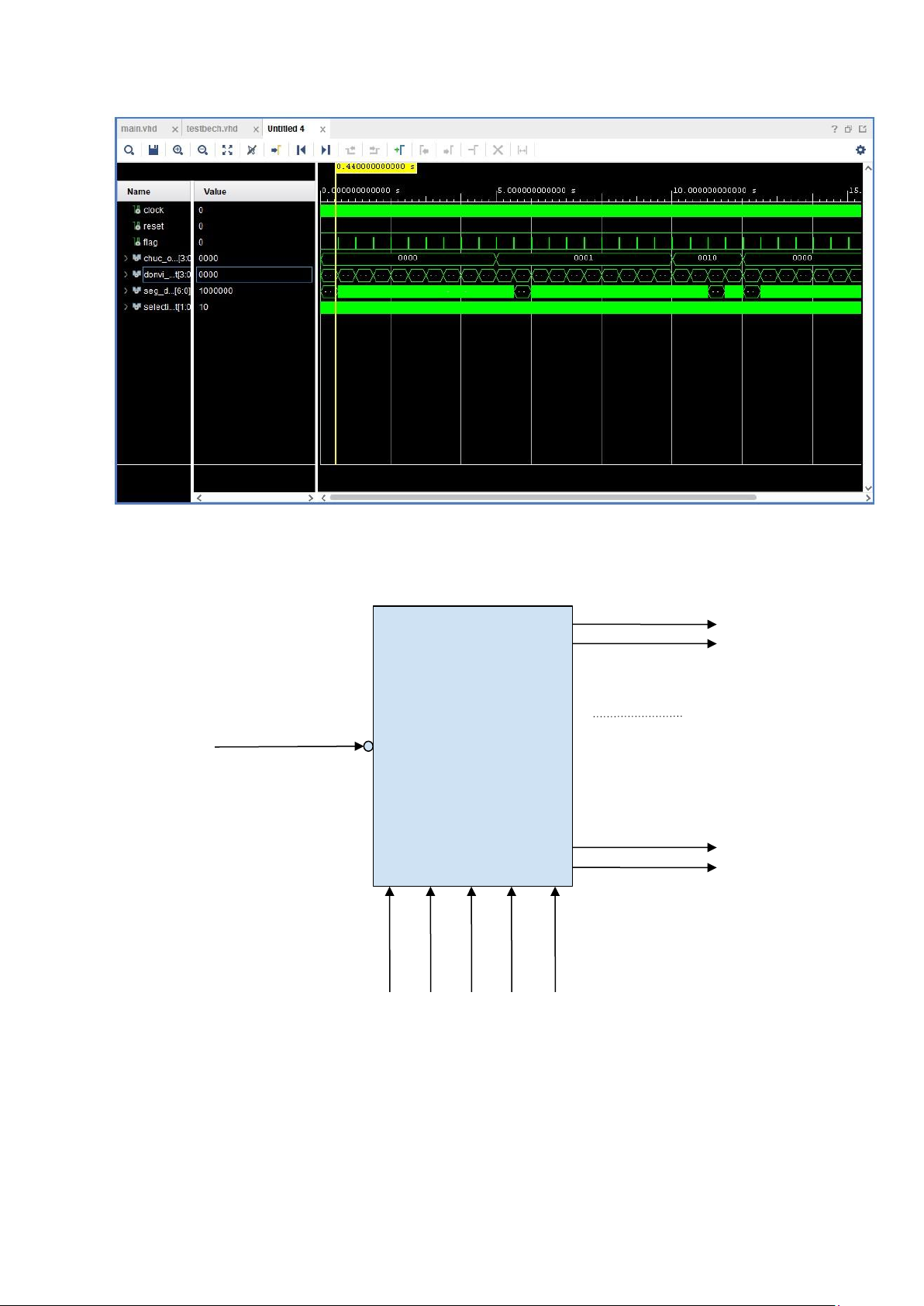

while not stop_simulation loop clk <= not clk; wait for 5 ns; end loop; lOMoAR cPSD| 58815430 wait; end process; end Behavioral; 4. Kết quả lOMoAR cPSD| 58815430 II. Bài2: 1. Sơ đồ khối 2. Cách làm -

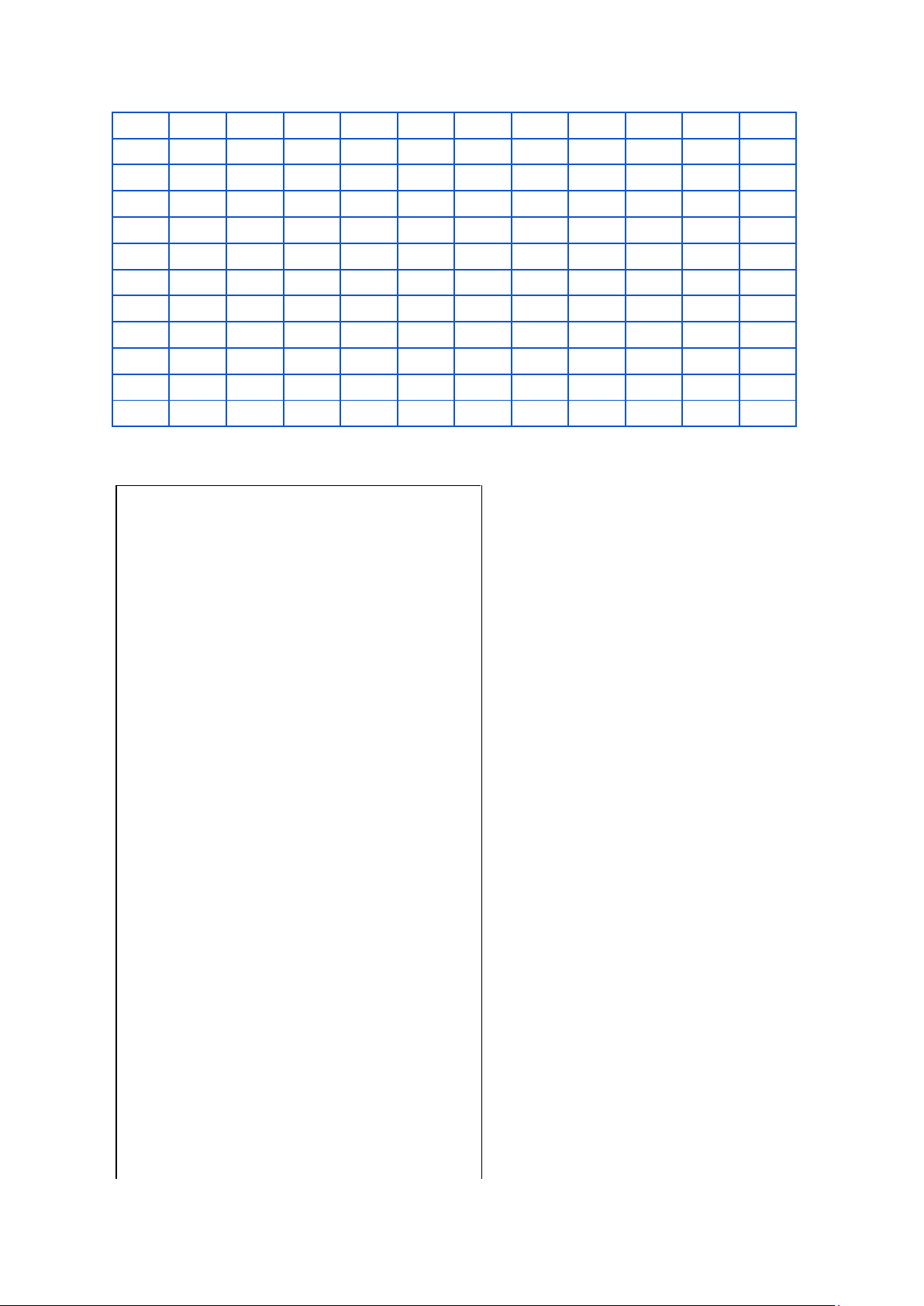

Dùng led 7 đoạn Anode chung.

- Đầu dương nối với nguồn cấp.

- Đầu âm là các tín hiệu ngõ ra. Bảng trạng thái: Số Ngõ vào số nhị Ngõ ra là mã 7 đoạn phân tp so_gma sseg (3) (2) (1) (0) g f e d c b a 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 1 1 1 0 0 1 2 0 0 1 0 0 1 0 0 1 0 0 3 0 0 1 1 0 1 1 0 0 0 0 lOMoAR cPSD| 58815430 4 0 1 0 0 0 0 1 1 0 0 1 5 0 1 0 1 0 0 1 0 0 1 0 6 0 1 1 0 0 0 0 0 0 1 0 7 0 1 1 1 1 1 1 1 0 0 0 8 1 0 0 0 0 0 0 0 0 0 0 9 1 0 0 1 0 0 1 0 0 0 0 10 1 0 1 0 0 0 0 1 0 0 0 11 1 0 1 1 0 0 0 0 0 1 1 12 1 1 0 0 1 0 0 0 1 1 0 13 1 1 0 1 0 1 0 0 0 0 1 14 1 1 1 0 0 0 0 0 1 1 0 15 1 1 1 1 0 0 0 1 1 1 0 3. Quá trình thực hiện - Main library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity gma_led7seg is Port ( so_gma : in

STD_LOGIC_VECTOR (3 downto 0);

sseg : out STD_LOGIC_VECTOR (6 downto 0)); end gma_led7seg; architecture Behavioral of gma_led7seg is begin process(so_gma) begin case so_gma is when x"0" => sseg <= "1000000"; –”0”

when x"1" => sseg <= "1111001"; –”1” when x"2" =>

sseg <= "0100100"; –”2”

when x"3" => sseg <= "0110000"; –“3” when x"4" =>

sseg <= "0011001"; –”4”

when x"5" => sseg <= "0010010"; –”5” when x"6" =>

sseg <= "1000010"; –”6”

when x"7" => sseg <= "1111000"; –”7” when x"8" =>

sseg <= "0000000"; –”8”

when x"9" => sseg <= "0010000"; –”9” when x"a" =>

sseg <= "0001000"; –”a”

when x"b" => sseg <= "0000011"; lOMoAR cPSD| 58815430 –”b” when x"c" =>

sseg <= "1000110"; –”c”

when x"d" => sseg <= "0100001"; –”d”

when x"e" => sseg <= "0000110"; –”e”

when others => sseg <= "0001110"; –”f” end case; end process; end Behavioral; - Testbench lOMoAR cPSD| 58815430 library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity testbech is end testbech;

architecture Behavioral of testbech is

signal so_gma : STD_LOGIC_VECTOR(3 downto 0) := (others => '0');

signal sseg : STD_LOGIC_VECTOR(6 downto 0); component gma_led7seg

Port ( so_gma : in STD_LOGIC_VECTOR (3 downto 0);

sseg : out STD_LOGIC_VECTOR (6 downto 0)); end component; begin uut : gma_led7seg port map ( so_gma => so_gma, sseg => sseg ); process begin -- Test cases

so_gma <= "0000"; -- “0” wait for 10 ns;

so_gma <= "0001"; -- “1” wait for 10 ns;

so_gma <= "0010"; -- “2” wait for 10 ns;

so_gma <= "0011"; -- “3” wait for 10 ns;

so_gma <= "0100"; -- “4” wait for 10 ns;

so_gma <= "0101"; -- “5” wait for 10 ns; lOMoAR cPSD| 58815430

so_gma <= "0110"; -- “6” wait for 10 ns;

so_gma <= "0111"; -- “7” wait for 10 ns;

so_gma <= "1000"; -- “8” wait for 10 ns;

so_gma <= "1001"; -- “9” wait for 10 ns;

so_gma <= "1010"; -- “A” wait for 10 ns;

so_gma <= "1011"; -- “B” wait for 10 ns;

so_gma <= "1100"; -- “C” wait for 10 ns;

so_gma <= "1101"; -- “D” wait for 10 ns;

so_gma <= "1110"; -- “E” wait for 10 ns;

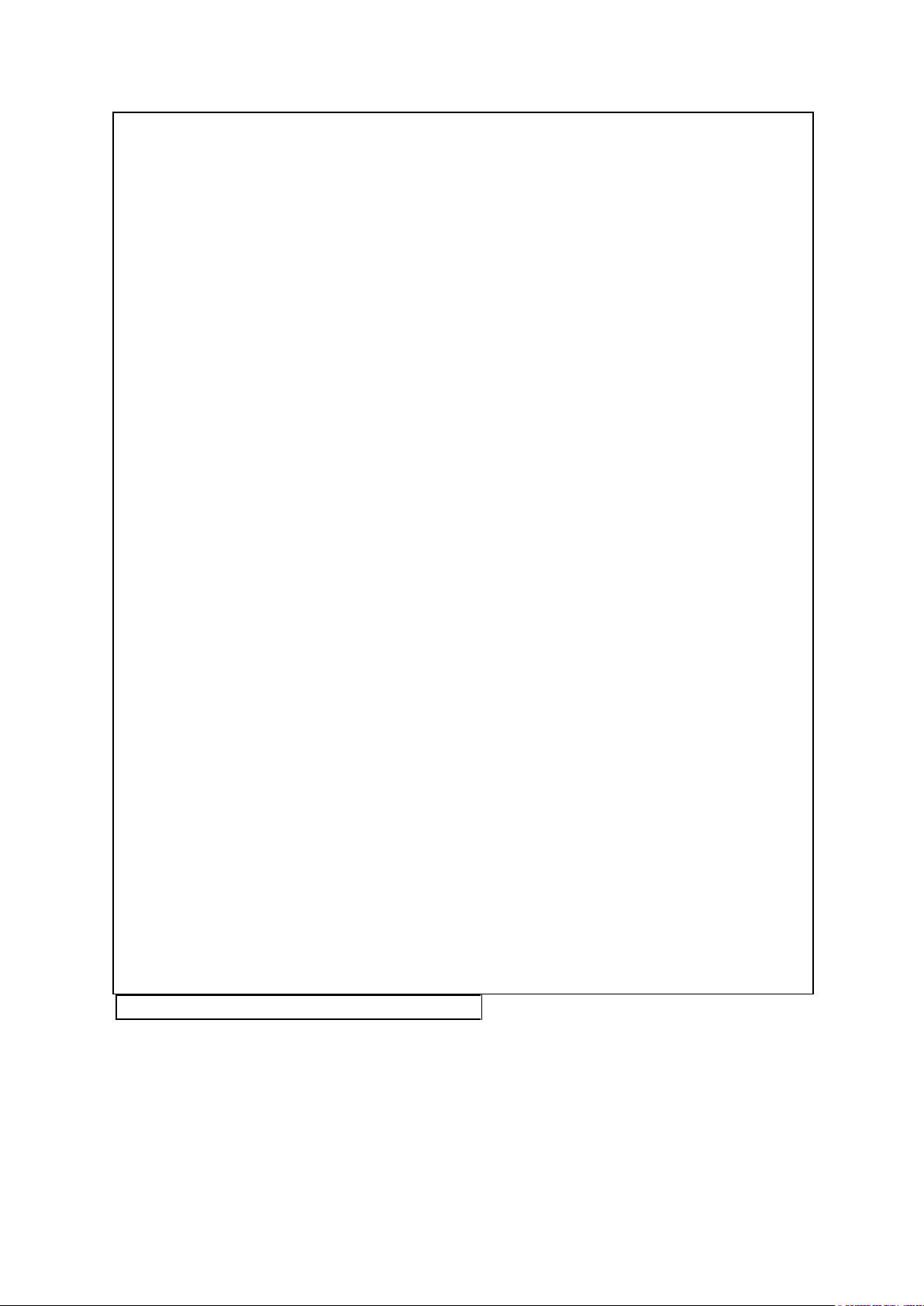

so_gma <= "1111"; – “F” wait for 10 ns; wait; end process; end Behavioral; 4. Kết quả lOMoAR cPSD| 58815430 III. Bài 3: 1. Nguyên lý clock 4 chuc so_gma 7 sseg reset donvi 4 flag seg_active 1 2 selection_port 10 01 2. Cách làm

- Dùng 2 Led 7 đoạn Anode chung.

- Khối giải mã tương tự như bài 2.

- Đầu dương của 2 led được nối với khối Selection_port, dùng phương pháp quét led để

quyết định xem Led hàng chục sáng hay Led hàng đơn vị sáng. 3. Quá trình thực hiện - Main library IEEE;

use IEEE.STD_LOGIC_1164.ALL; use IEEE.std_logic_unsigned.all; entity main is Port ( clock : in STD_LOGIC; reset : in STD_LOGIC; lOMoAR cPSD| 58815430 lOMoAR cPSD| 58815430 flag : in STD_LOGIC;

selection_port : out STD_LOGIC_VECTOR (1 downto

0); chuc_out : out STD_LOGIC_VECTOR (3 downto 0);

donvi_out : out STD_LOGIC_VECTOR (3 downto 0);

sseg : out STD_LOGIC_VECTOR (6 downto 0)); end main;

architecture Behavioral of main is

signal chuc: std_logic_vector(3 downto 0) := "0000";

signal donvi: std_logic_vector(3 downto 0) := "0000";

signal so_gma: STD_LOGIC_VECTOR (3 downto 0);

signal seg_active: std_logic := '0'; begin process(seg_active) begin case seg_active is when '0' => selection_port <= "10";

-- activate chuc and Deactivate donvi so_gma <= chuc; when '1' => selection_port <= "01";

-- activate donvi and Deactivate chuc so_gma <= donvi; when others => null; end case; end process; process(so_gma) begin case so_gma is

when "0000" => sseg <= "1000000"; -- "0"

when "0001" => sseg <= "1111001"; -- "1"

when "0010" => sseg <= "0100100"; -- "2"

when "0011" => sseg <= "0110000"; -- "3"

when "0100" => sseg <= "0011001"; -- "4"

when "0101" => sseg <= "0010010"; -- "5"

when "0110" => sseg <= "0000010"; -- "6"

when "0111" => sseg <= "1111000"; -- "7"

when "1000" => sseg <= "0000000"; -- "8"

when "1001" => sseg <= "0010000"; -- "9" when others => null; end case; end process; process(clock, reset, flag) begin if (rising_edge(clock)) then

seg_active <= not seg_active; lOMoAR cPSD| 58815430 donvi_out <= donvi; chuc_out <= chuc; if(flag = '1') then donvi <= donvi + 1; donvi_out <= donvi; if (donvi + 1 = "1010") then chuc <= chuc + 1; chuc_out <= chuc; donvi <= "0000"; end if; if(donvi + 1 = "0100") then if(chuc ="0010") then chuc <= "0000"; donvi<="0000"; else donvi<=donvi+1; end if; end if; end if; if (reset = '1') then chuc <= "0000"; donvi <= "0000"; end if; end if; end process; end Behavioral; - Testbench lOMoAR cPSD| 58815430 library IEEE; use IEEE.STD_LOGIC_1164.ALL;

USE ieee.std_logic_unsigned.all; USE ieee.numeric_std.ALL; entity testbech is end testbech;

architecture Behavioral of testbech is component main is Port ( clock : in STD_LOGIC; reset : in STD_LOGIC; flag : in STD_LOGIC;

selection_port : out STD_LOGIC_VECTOR (1 downto

0); chuc_out : out STD_LOGIC_VECTOR (3 downto 0);

donvi_out : out STD_LOGIC_VECTOR (3 downto 0);

sseg : out STD_LOGIC_VECTOR (6 downto 0)); end component; lOMoAR cPSD| 58815430 --Inputs

SIGNAL clock : std_logic := '0';

SIGNAL reset : std_logic := '0';

SIGNAL flag : std_logic := '0';

SIGNAL chuc_out : std_logic_vector(3 downto 0);

SIGNAL donvi_out : std_logic_vector(3 downto 0);

SIGNAL sseg : std_logic_vector(6 downto 0);

SIGNAL selection_port : std_logic_vector(1 downto 0); begin

c1: main PORT MAP( clock => clock, reset => reset,

flag => flag, chuc_out => chuc_out, donvi_out =>

donvi_out, selection_port => selection_port, sseg => sseg ); PROCESS BEGIN wait for 500us; clock <= not clock; END PROCESS; PROCESS BEGIN wait for 500ms; flag <= '1'; wait for 1ms; flag <= '0'; END PROCESS; PROCESS BEGIN wait for 200000ms; reset <= '1'; wait for 5000ms; reset <= not reset; wait for 300000ms; reset <= '1'; wait for 1000ms; reset <= not reset; wait; END PROCESS; end Behavioral; 4. Kết quả lOMoAR cPSD| 58815430 IV. Bài 4:

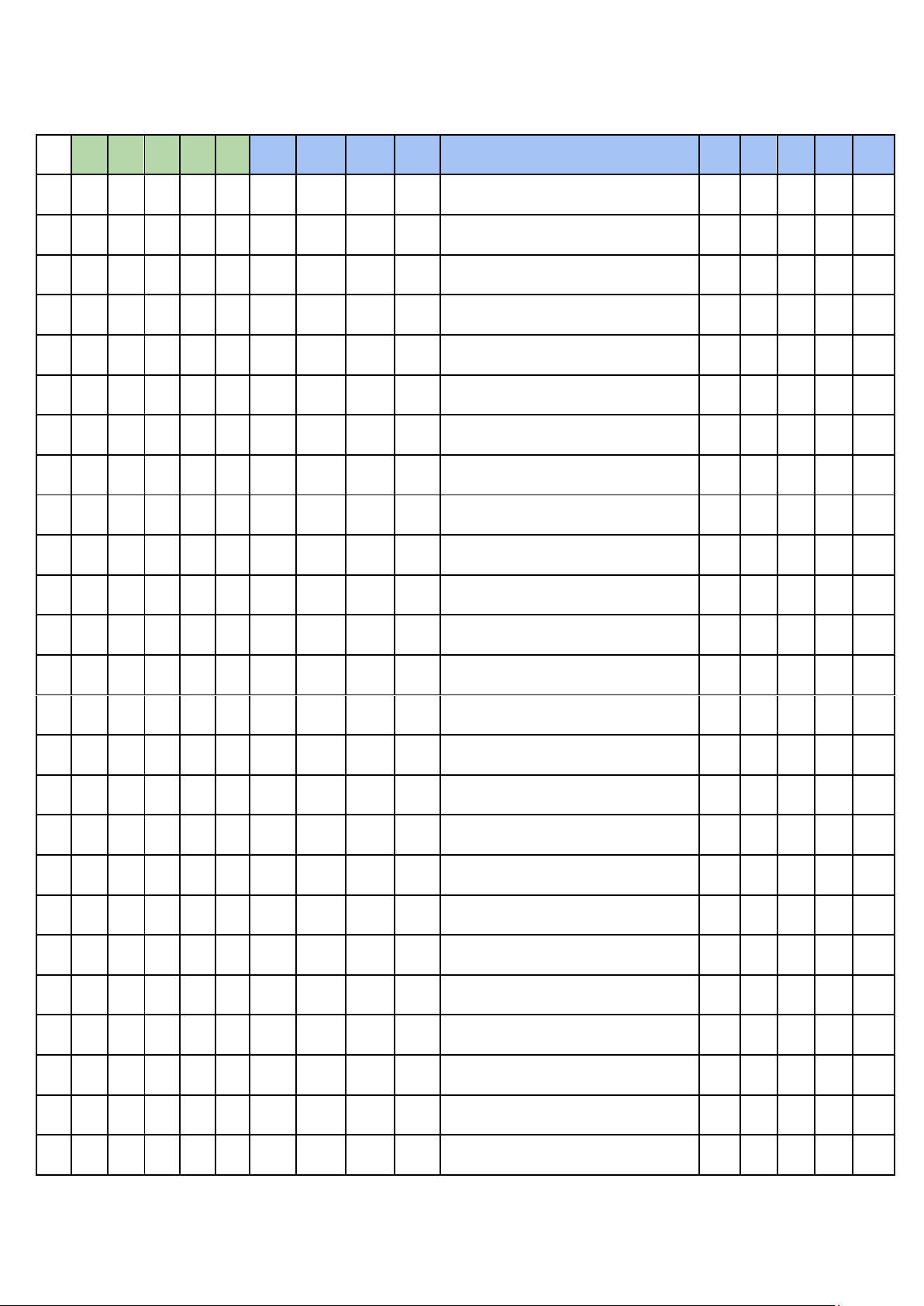

1. Sơ đồ khối DEMUX 1:32 Y(0) Y(1) 1 x 32 E De - Multiplexer Y(30) Y(31) S4 S3 S2 S1S0 2. Cách làm

- Kênh vào Enable hoạt động ở mức thấp.

- Tín hiệu phân kênh 5 bit Sel[4:0]. - 32 kênh ra Channels[31:0]. lOMoAR cPSD| 58815430

E s4 s3 s2 s1 s0 y31 y30 y29 y28 y27………………………..y5 y4 y3 y2 y1 y0 0 0 0 0 0 0 0 0 0 0 00000000000000000000000 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 00000000000000000000000 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 00000000000000000000000 0 0 1 0 0 0 0 0 0 1 1 0 0 0 0 00000000000000000000000 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 00000000000000000000000 1 0 0 0 0 0 0 0 1 0 1 0 0 0 0 00000000000000000000001 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 00000000000000000000010 0 0 0 0 0 0 0 0 1 1 1 0 0 0 0 00000000000000000000100 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 00000000000000000001000 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 00000000000000000010000 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 00000000000000000100000 0 0 0 0 0 0 0 1 0 1 1 0 0 0 0 00000000000000001000000 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 00000000000000010000000 0 0 0 0 0 0 0 1 1 0 1 0 0 0 0 00000000000000100000000 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0 00000000000001000000000 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 00000000000010000000000 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 00000000000100000000000 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 00000000001000000000000 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 00000000010000000000000 0 0 0 0 0 0 1 0 0 1 1 0 0 0 0 00000000100000000000000 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 00000001000000000000000 0 0 0 0 0 0 1 0 1 0 1 0 0 0 0 00000010000000000000000 0 0 0 0 0 0 1 0 1 1 0 0 0 0 0 00000100000000000000000 0 0 0 0 0 0 1 0 1 1 1 0 0 0 0 00001000000000000000000 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 00010000000000000000000 0 0 0 0 0 lOMoAR cPSD| 58815430 0 1 1 0 0 1 0 0 0 0 00100000000000000000000 0 0 0 0 0 0 1 1 0 1 0 0 0 0 0 01000000000000000000000 0 0 0 0 0 0 1 1 0 1 1 0 0 0 0 10000000000000000000000 0 0 0 0 0 0 1 1 1 0 0 0 0 0 1 00000000000000000000000 0 0 0 0 0 0 1 1 1 0 1 0 0 1 0 00000000000000000000000 0 0 0 0 0 0 1 1 1 1 0 0 1 0 0 00000000000000000000000 0 0 0 0 0 0 1 1 1 1 1 1 0 0 0 00000000000000000000000 0 0 0 0 0 3. Chương trình - Main lOMoAR cPSD| 58815430 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Demux_1to32 is Port ( D: in std_logic; enable: in STD_LOGIC;

sel: in STD_LOGIC_VECTOR(4 downto 0);

Y: out STD_LOGIC_VECTOR(31 downto 0) ); end Demux_1to32;

architecture rtl of Demux_1to32 is begin process(D, enable, sel) begin if enable = '1' then Y <= (others => '0'); else Y <= (others => '0'); case sel is

when "00000" => Y(0) <= D;

when "00001" => Y(1) <= D;

when "00010" => Y(2) <= D;

when "00011" => Y(3) <= D;

when "00100" => Y(4) <= D;

when "00101" => Y(5) <= D;

when "00110" => Y(6) <= D;

when "00111" => Y(7) <= D;

when "01000" => Y(8) <= D;

when "01001" => Y(9) <= D;

when "01010" => Y(10) <= D;

when "01011" => Y(11) <= D;

when "01100" => Y(12) <= D;

when "01101" => Y(13) <= D;

when "01110" => Y(14) <= D; lOMoAR cPSD| 58815430

when "01111" => Y(15) <= D;

when "10000" => Y(16) <= D; when

"10001" => Y(17) <= D; when "10010"

=> Y(18) <= D; when "10011" =>

Y(19) <= D; when "10100" => Y(20)

<= D; when "10101" => Y(21) <= D;

when "10110" => Y(22) <= D; when

"10111" => Y(23) <= D; when "11000"

=> Y(24) <= D; when "11001" =>

Y(25) <= D; when "11010" => Y(26)

<= D; when "11011" => Y(27) <= D;

when "11100" => Y(28) <= D; when

"11101" => Y(29) <= D; when "11110"

=> Y(30) <= D; when "11111" =>

Y(31) <= D; when others => Y <= (others => '0'); end case; end if; end process; end rtl; - Testbench library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use IEEE.Numeric_Std.all; entity Testbench is end Testbench;

architecture Behavioral of Testbench is component Demux_1to32 Port ( D : in std_logic; enable : in STD_LOGIC;

sel : in STD_LOGIC_VECTOR(4 downto 0);

Y: out STD_LOGIC_VECTOR(31 downto 0) ); end component; signal D: std_logic;

signal sel: std_logic_vector(4 downto 0); signal enable: std_logic;

signal Y: std_logic_vector(31 downto 0) ; begin uut: Demux_1to32 Port Map (