Preview text:

lOMoAR cPSD| 58815430

HỌC VIỆN CÔNG NGHỆ BƯU CHÍNH VIỄN THÔNG

---------------------------------------------------

BÁO CÁO BÀI TẬP LỚN

MÔN HỌC: THIẾT KẾ LOGIC SỐ Họ và tên

: Đỗ Tuấn Thịnh – B21DCDT214

Trần Ngọc Huy – B21DCDT114 Nhóm lớp : 04 Nhóm bài tập : 16 Đề tài : 21 Giảng viên

: TS. Trần Thúy Hà Hà Nội - 2024 lOMoAR cPSD| 58815430

NHẬN XÉT CỦA GIẢNG VIÊN lOMoAR cPSD| 58815430

Phần tự đánh giá STT Họ và tên Mã sinh viên Công việc Kết quả Tự cho điểm 1 Đỗ Tuấn Thịnh B21DCDT214 Câu 1,3,4 2 Trần Ngọc Huy B21DCDT Câu 2,5,6 lOMoAR cPSD| 58815430 lOMoAR cPSD| 58815430

Bài 1: Thiết kế mạch tổ hợp kiểm tra hai từ mã (A và B) 4 bit và hiển thị

kết quả nếu từ mã A nhỏ hơn từ mã B. Viết testbench để kiểm tra hoạt động của mạch.

1.1: Phân tích đề bài.

Đề bài yêu cầu thiết kế mạch tổ hợp (combinational circuit), tức là mạch

không chứa thành phần nhớ (không cần dùng xung clock). Mạch này có chức

năng so sánh hai từ mã 4 bit là A và B và cho ra kết quả nếu từ mã A nhỏ hơn từ mã B.

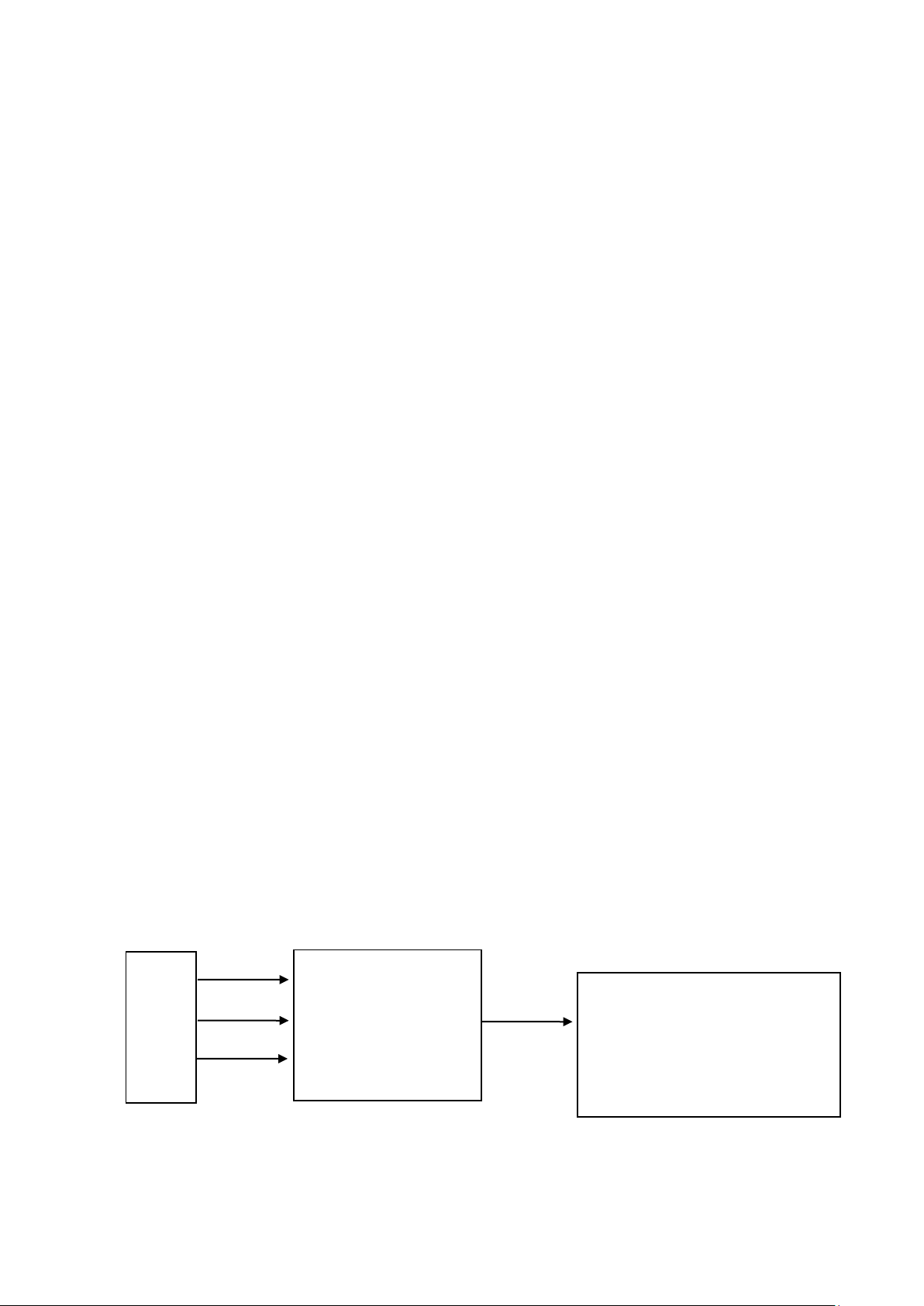

1.2: Mô hình hệ thống. - Sơ đồ khối: -

Khối Input: Nhận các đầu vào A và B, mỗi đầu vào là một từ mã 4 bit. -

Khối So sánh (Comparator): Đây là khối trung tâm của

mạch, thực hiện phép so sánh từng bit của A và B. Cụ thể, khối này sẽ

kiểm tra các bit từ cao nhất (MSB) đến thấp nhất (LSB) để xác định A <

B. Khối này sẽ cho ra một tín hiệu kết quả duy nhất. -

Khối Output: Hiển thị kết quả của phép so sánh. Nếu A < B,

khối output sẽ xuất Out = 1, nếu không thì Out = 0. - Mô hình mạch: A[0;3] Khối so sánh

Out (1 Nếu Atừ mã A và B lại là 0) B[0;3]

1.3: Nguyên lý làm việc.

Mạch hoạt động dựa trên nguyên tắc so sánh từng bit của A và B từ bit

cao nhất (MSB) đến bit thấp nhất (LSB):

So sánh MSB (A3 và B3):

Nếu A3 < B3, kết luận A < B và Out = 1.

Nếu A3 > B3, kết luận A > B và Out = 0.

Nếu A3 = B3, tiếp tục so sánh các bit tiếp theo. lOMoAR cPSD| 58815430

So sánh các bit tiếp theo (A2, A1, A0 với B2, B1, B0):

Nếu bất kỳ Ai < Bi, kết luận A < B và Out = 1.

Nếu bất kỳ Ai > Bi, kết luận A > B và Out = 0.

Nếu tất cả các bit bằng nhau, thì A = B và Out = 0.

Kết quả: Out = 1 nếu A < B, và Out = 0 nếu A >= B.

1.4: Mã VHDL và Testbench. VHDL:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use

IEEE.NUMERIC_STD.ALL; entity Cau1 is Port ( a, b :

in STD_LOGIC_VECTOR (3 downto 0); ketqua : out STD_LOGIC ); end Cau1;

-- kiến trúc của thực thể Cau1

architecture bhv of Cau1 is begin process(a, b) begin

-- Chuyển đổi a và b từ kiểu STD_LOGIC_VECTOR sang kiểu unsigned để thực hiện so

sánh if unsigned(a) < unsigned(b) then ketqua <= '1'; -- Nếu a < b, gán ketqua là

'1' else ketqua <= '0'; -- Ngược lại gán ketqua là '0' end if; end process; end bhv; Testbench:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Cau1_tb

is end Cau1_tb; architecture bhv of Cau1_tb is signal a,b

: STD_LOGIC_VECTOR(3 downto 0); signal ketqua : STD_LOGIC; component Cau1 Port (

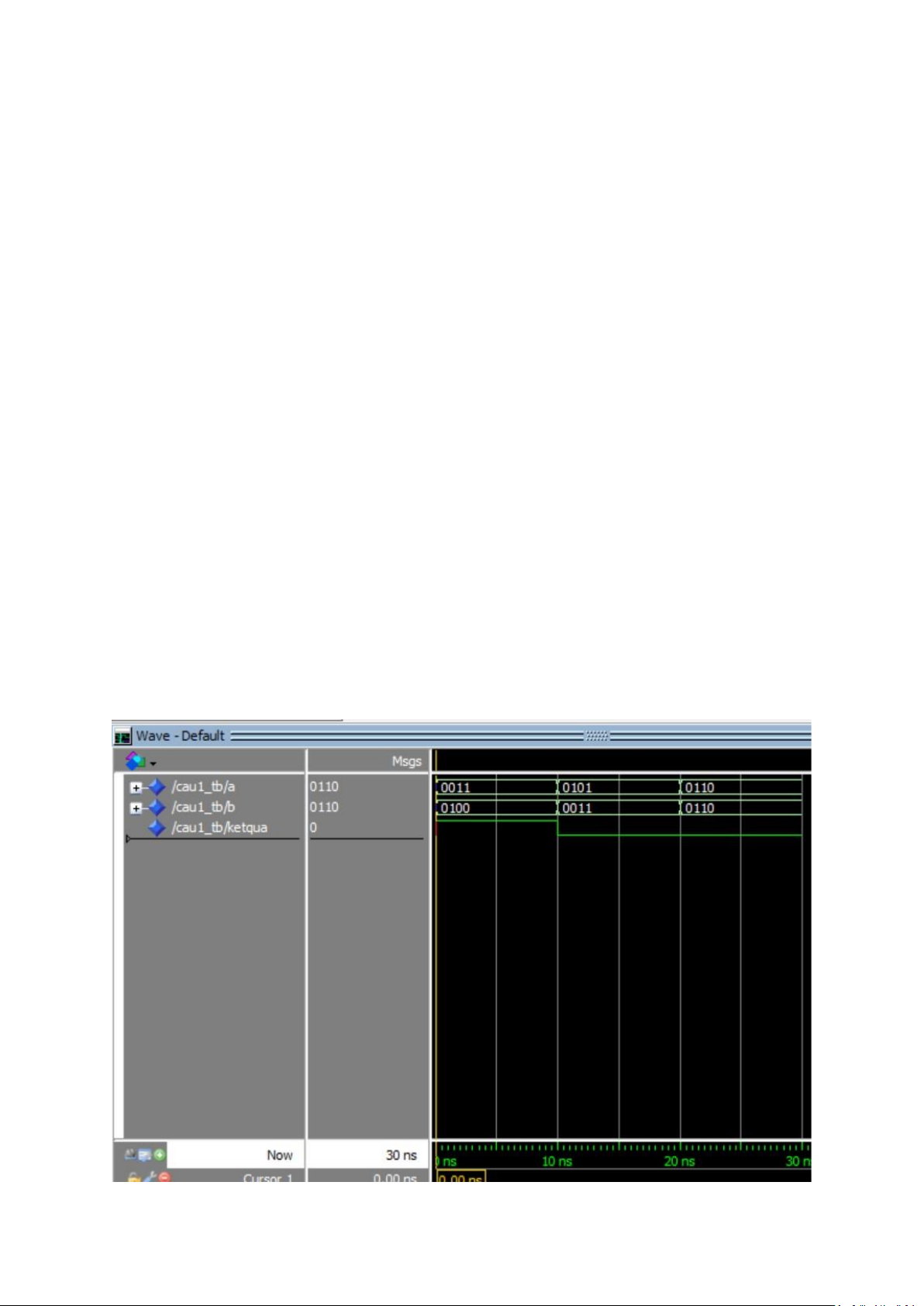

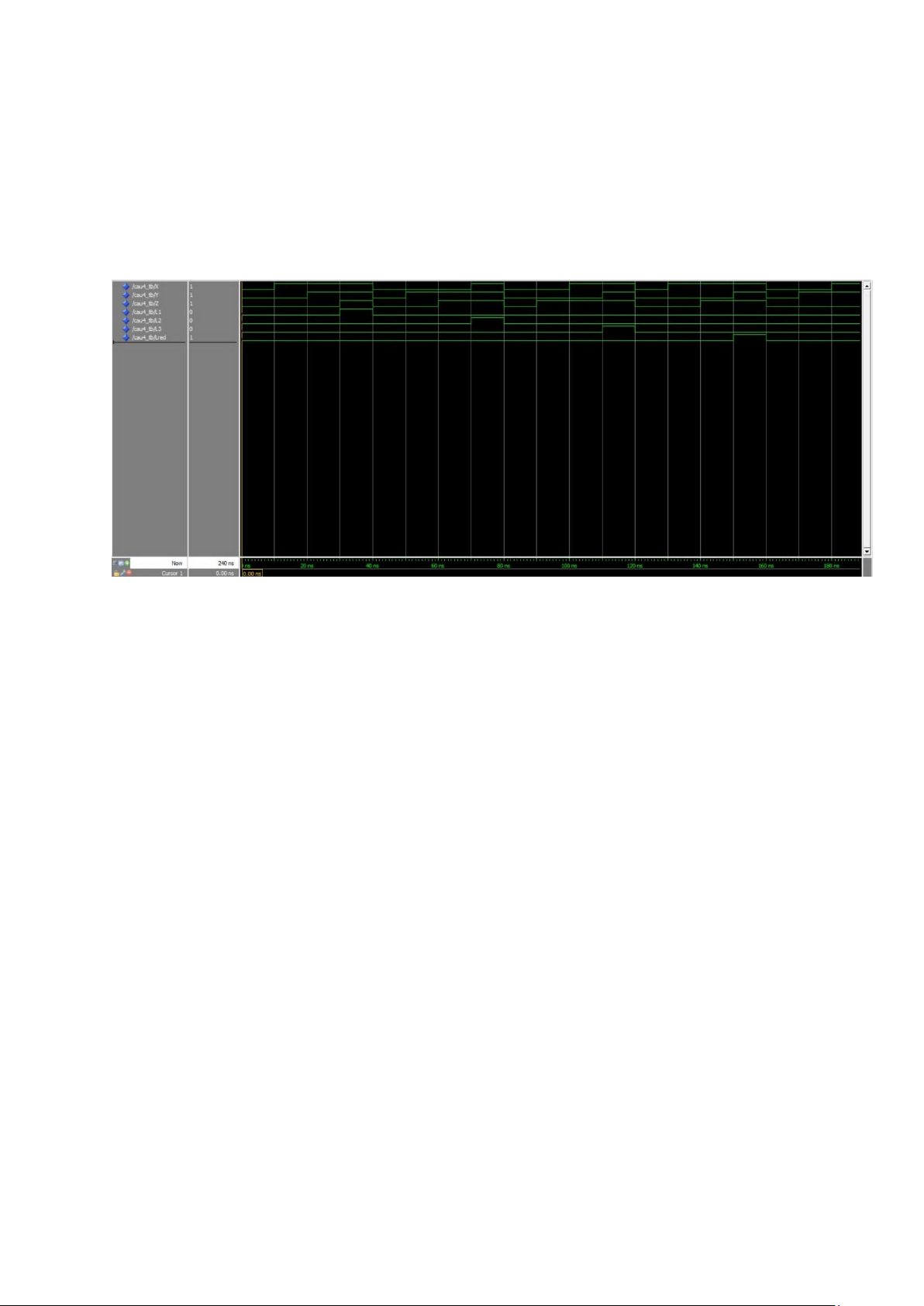

a,b : in STD_LOGIC_VECTOR(3 downto 0); ketqua : out STD_LOGIC ); lOMoAR cPSD| 58815430 end component; begin uut: Cau1 port map ( a => a, b => b, ketqua => ketqua ); process begin a <= "0011"; b <= "0100"; wait for 10 ns; a <= "0101"; b <= "0011"; wait for 10 ns; a <= "0110"; b <= "0110"; wait for 10 ns; wait; end process; end bhv; 1.5: Kết quả. lOMoAR cPSD| 58815430

Bài 3: Một mạch 3 đèn được hoạt động theo sự điều khiển của 3 chuyển

mạch X, Y, Z. Nếu các chuyển mạch được bật theo thứ tự:

X Y Z đèn L1 sáng Y Z X đèn L2 sáng Z X Y đèn L3 sáng

3.1: Phân tích đề bài.

Đề bài yêu cầu viết mã mô tả phần cứng (VDHL) và testbench cho một

mạch điều khiển ba đèn với điều kiện kích hoạt phụ thuộc vào thứ tự bật của ba chuyển mạch X, Y, Z.

3.2: Mô hình hệ thống. - Sơ đồ khối:

Ba công tắc đầu vào: X, Y, Z: Ba công tắc đầu vào, mỗi công tắc có thể ở

trạng thái "bật" hoặc "tắt".

Khối kiểm tra thứ tự bật công tắc:

Khối này có nhiệm vụ theo dõi và nhận biết thứ tự bật của ba

công tắc X, Y, Z. Dựa vào thứ tự này, khối sẽ xác định đèn nào sẽ sáng. Ba đèn đầu ra:

L1: Sáng khi thứ tự bật công tắc là X Y Z.

L2: Sáng khi thứ tự bật công tắc là Y Z X.

L3: Sáng khi thứ tự bật công tắc là Z X Y. -Mô hình mạch: Công tắc Khối kiểm tra Ba đèn đầu ra X Công tắc X Đèn L1 sáng(X Y Z) Y Công tắc Y Đèn L2 sáng(Y Z X) Z Công tắc Z Đèn L3 sáng(Z X Y)

3.3: Nguyên lí làm việc.

Nguyên lí làm việc: lOMoAR cPSD| 58815430

Mạch điều khiển ba đèn dựa vào thứ tự bật ba công tắc X, Y, Z:

L1 sáng khi thứ tự bật là X → Y → Z.

L2 sáng khi thứ tự bật là Y → Z → X. L3 sáng

khi thứ tự bật là Z → X → Y.

Khối logic trong mạch sẽ ghi nhận thứ tự bật của các công tắc. Khi thứ tự

đúng, khối logic phát tín hiệu để bật đèn tương ứng. Nếu thứ tự không khớp

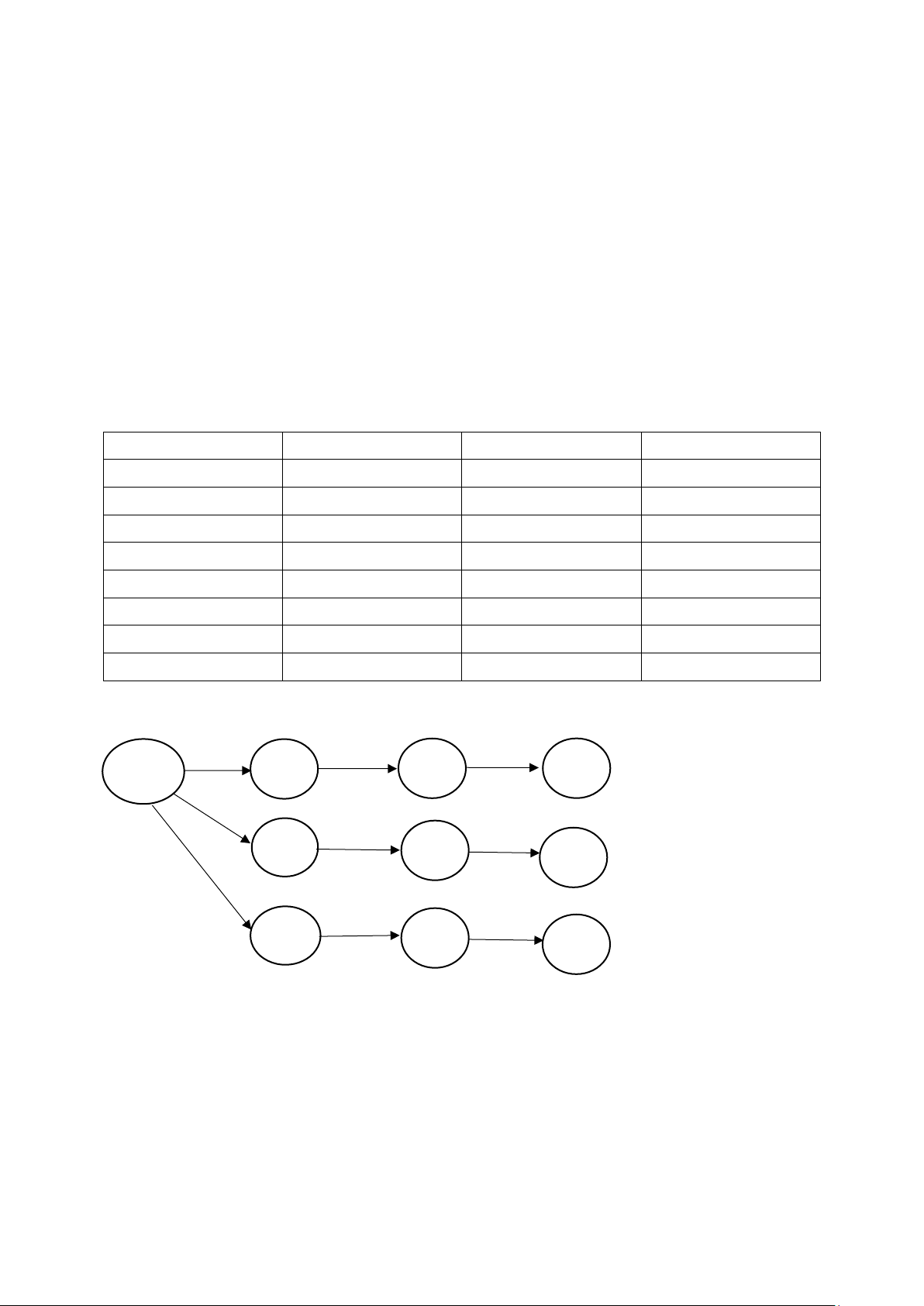

với các điều kiện đã nêu, tất cả đèn sẽ tắt. Bảng trạng thái: X Y Z Trạng thái 0 0 0 S0 0 0 1 S1 0 1 0 S2 0 1 1 S3 1 0 0 S4 1 0 1 S5 1 1 0 S6 1 1 1 S7

Đồ hình trạng thái: S L1: sáng S S 0 S 4 6 7 S 2 S 3 S 7 L2: sáng S 1 S 5 S L3: sáng 7

3.4: Mã VHDL và Testbench. VHDL: lOMoAR cPSD| 58815430 library IEEE; use

IEEE.STD_LOGIC_1164.ALL; entity Cau3 is port ( X, Y, Z : in std_logic; L1, L2, L3 : out std_logic ); end Cau3; architecture bhv of Cau3 is

type type_state is (s0, s1, s2, s3, s4, s5, s6, s7); signal state

: type_state := s0; signal X_pre, Y_pre, Z_pre : std_logic := '0'; begin process (X, Y, Z) begin L1 <= '0'; L2 <= '0'; L3 <= '0'; case state is when s0 =>

if (X = '1' and X_pre = '0') then state

<= s4; elsif (Y = '1' and Y_pre = '0') then

state <= s2; elsif (Z = '1' and Z_pre = '0') then state <= s1; end if; when s4 =>

if (Y = '1' and Y_pre = '0') then state <= s6; end if;

when s6 => if (Z = '1' and Z_pre =

'0') then L1 <= '1'; state <= s0; end if;

when s2 => if (Z = '1' and Z_pre =

'0') then state <= s3; end if;

when s3 => if (X = '1' and X_pre =

'0') then L2 <= '1'; state <= s0; end if; lOMoAR cPSD| 58815430

when s1 => if (X = '1' and X_pre =

'0') then state <= s5; end if;

when s5 => if (Y = '1' and Y_pre =

'0') then L3 <= '1'; state <= s0; end if; when others => state <= s0; end case; X_pre <= X; Y_pre <= Y; Z_pre <= Z; end process; end bhv; Testbench: library IEEE; use

IEEE.STD_LOGIC_1164.ALL; entity

Cau3_tb is end Cau3_tb; architecture

sim of Cau3_tb is signal X, Y, Z :

std_logic := '0'; signal L1, L2, L3 :

std_logic; begin uut: entity work.Cau3 port map ( X => X, Y => Y, Z => Z, L1 => L1, L2 => L2, L3 => L3 ); stim_proc: process begin

X <= '0'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '1'; Y <= '0'; Z <= '0'; wait for 10 ns; lOMoAR cPSD| 58815430

X <= '1'; Y <= '1'; Z <= '0'; wait for 10 ns;

X <= '1'; Y <= '1'; Z <= '1'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '0'; Y <= '1'; Z <= '0'; wait for 10 ns;

X <= '0'; Y <= '1'; Z <= '1'; wait for 10 ns;

X <= '1'; Y <= '1'; Z <= '1'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '1'; wait for 10 ns;

X <= '1'; Y <= '0'; Z <= '1'; wait for 10 ns;

X <= '1'; Y <= '1'; Z <= '1'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '0'; Y <= '1'; Z <= '0'; wait for 10 ns;

X <= '1'; Y <= '1'; Z <= '0'; wait

for 10 ns; X <= '1'; Y <= '1'; Z <= '1';

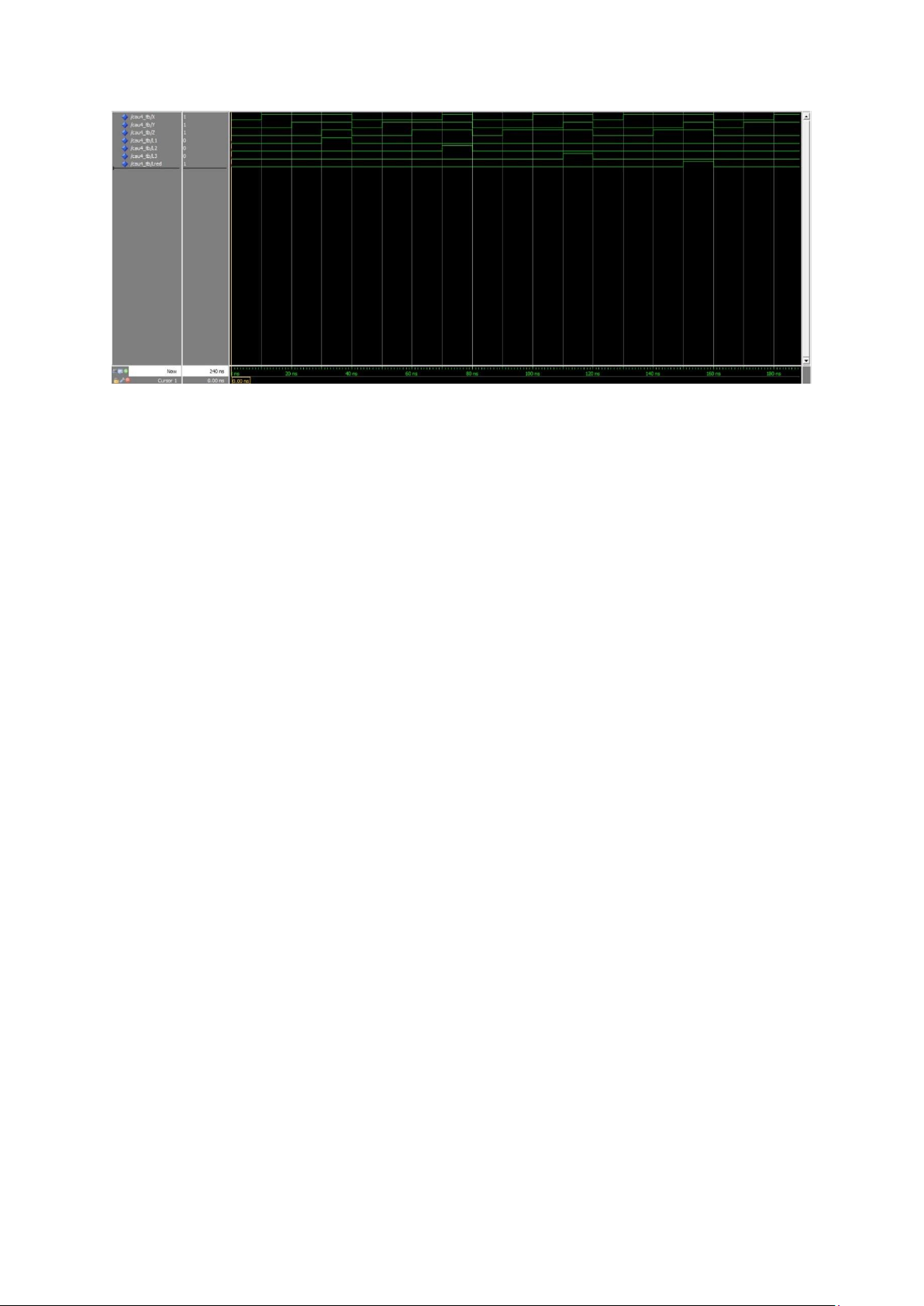

wait for 10 ns; wait; end process; end sim; 3.5: Kết quả lOMoAR cPSD| 58815430

Bài 4: Nếu các chuyển mạch hoạt động sai thứ tự trên thì đèn đỏ sẽ sáng báo

hiệu cho người điều khiển và người điều khiển phải đưa các chuyển mạch về

trạng thái tĩnh ban đầu. Viết testbench để kiểm tra hoạt động của mạch.

4.1: Phân tích đề bài.

Đề bài yêu cầu viết mã mô tả phần cứng (VDHL) và testbench cho một mạch

điều khiển ba đèn với điều kiện kích hoạt phụ thuộc vào thứ tự bật của ba

chuyển mạch X, Y, Z và đèn đỏ sáng báo lỗi khi sai thứ tự.

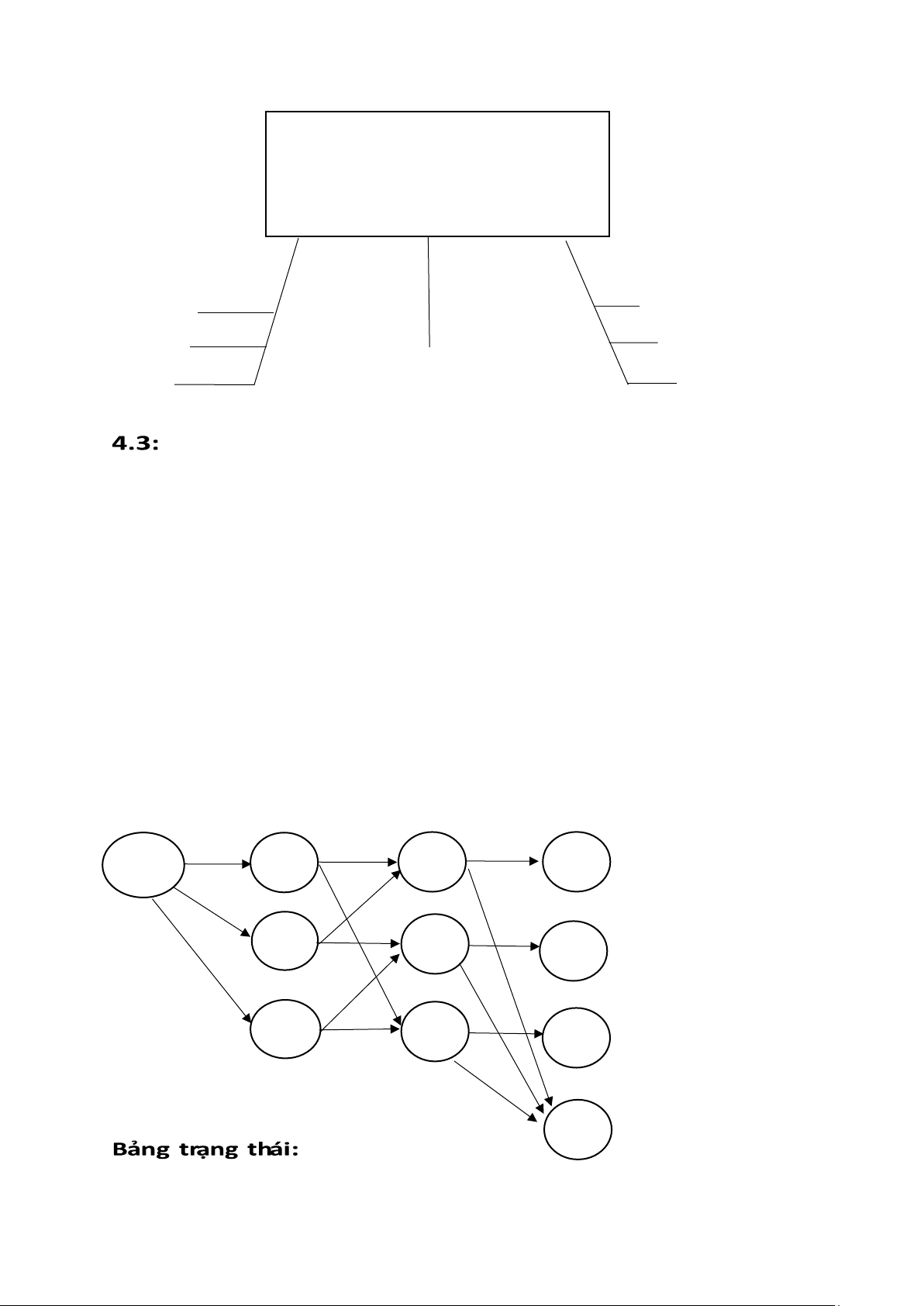

4.2: Mô hình hệ thống. - Sơ đồ khối:

Công tắc X, Y, Z: Đầu vào cho hệ thống, gửi tín hiệu vào khối logic để xác định thứ tự bật.

Khối logic kiểm tra thứ tự: Phân tích thứ tự bật công tắc. Nếu đúng thứ

tự, kích hoạt một trong các đèn L1, L2, L3; nếu sai thứ tự, kích hoạt đèn đỏ báo lỗi.

Đèn L1, L2, L3: Sáng khi các công tắc bật đúng thứ tự tương ứng.

Đèn đỏ: Báo lỗi khi thứ tự bật công tắc không đúng, yêu cầu người điều

khiển đưa các công tắc về trạng thái ban đầu. - Mô hình mạch: lOMoAR cPSD| 58815430

Khối logic kiểm tra thứ tự bật X

L1 sáng khi thứ tự X Y Z Y

L2 sáng khi thứ tự Y Z X

Đèn đỏ báo lỗi khi sai thứ tự Z

L2 sáng khi thứ tự Z X Y

Nguyên lý làm việc.

Nguyên lý làm việc: Đèn đúng thứ tự:

L1 sáng khi bật công tắc theo thứ tự X → Y → Z.

L2 sáng khi bật theo thứ tự Y → Z → X.

L3 sáng khi bật theo thứ tự Z → X → Y. Đèn đỏ báo lỗi:

Sáng khi thứ tự bật công tắc sai.

Chỉ tắt khi các công tắc được đưa về trạng thái ban đầu.

Mô hình trạng thái: S L1: sáng S S 0 S 4 6 7 S 2 S 3 S 7 L2: sáng S 1 S 5 S L3: sáng 7 Lđỏ: sáng S 7 lOMoAR cPSD| 58815430 X Y Z Trạng thái 0 0 0 S0 0 0 1 S1 0 1 0 S2 0 1 1 S3 1 0 0 S4 1 0 1 S5 1 1 0 S6 1 1 1 S7

4.4: Mã VHDL và Testbench. VHDL: library IEEE; use

IEEE.STD_LOGIC_1164.ALL; entity Cau4 is port ( X, Y, Z : in std_logic;

L1, L2, L3, Lred : out std_logic );

end Cau4; architecture bhv of Cau4 is type type_state is (s0,

s1, s2, s3, s4, s5, s6, s7); signal state : type_state := s0;

signal X_pre, Y_pre, Z_pre : std_logic := '0'; begin process (X, Y, Z) begin L1 <= '0'; L2 <= '0'; L3 <= '0'; Lred <= '0';

case state is when s0 => if (X = '1'

and X_pre = '0') then state <= s4;

elsif (Y = '1' and Y_pre = '0') then state <=

s2; elsif (Z = '1' and Z_pre = '0') then state <= s1; end if;

when s4 => if (Y = '1' and Y_pre = '0') then state <= s6; lOMoAR cPSD| 58815430 else state <= s7; end if; when s6 =>

if (Z = '1' and Z_pre = '0') then L1 <= '1'; state <= s0; else state <= s7; end if;

when s2 => if (Z = '1' and Z_pre = '0') then state <= s3; else state <= s7; end if;

when s3 => if (X = '1' and X_pre = '0')

then L2 <= '1'; state <= s0; else state <= s7; end if;

when s1 => if (X = '1' and X_pre = '0') then state <= s5; else state <= s7; end if;

when s5 => if (Y = '1' and Y_pre =

'0') then L3 <= '1'; state <= s0; else state <= s7; end if;

when s7 => Lred <= '1'; state <= s0; lOMoAR cPSD| 58815430 when others => state <= s0; end case; X_pre <= X; Y_pre <= Y; Z_pre <= Z; end process; end bhv; Testbench:

library IEEE; use IEEE.STD_LOGIC_1164.ALL;

entity Cau4_tb is end Cau4_tb;

architecture sim of Cau4_tb is signal X, Y,

Z : std_logic := '0'; signal L1, L2, L3, Lred :

std_logic; begin uut: entity work.Cau4 port map ( X => X, Y => Y, Z => Z, L1 => L1, L2 => L2, L3 => L3, Lred => Lred ); stim_proc: process begin

X <= '0'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '1'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '1'; Y <= '1'; Z <= '0'; wait for 10 ns;

X <= '1'; Y <= '1'; Z <= '1'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '0'; lOMoAR cPSD| 58815430 wait for 10 ns;

X <= '0'; Y <= '1'; Z <= '0'; wait for 10 ns;

X <= '0'; Y <= '1'; Z <= '1'; wait for 10 ns;

X <= '1'; Y <= '1'; Z <= '1'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '1'; wait for 10 ns;

X <= '1'; Y <= '0'; Z <= '1'; wait for 10 ns;

X <= '1'; Y <= '1'; Z <= '1'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '1'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '1'; Y <= '0'; Z <= '1'; wait

for 10 ns; X <= '1'; Y <= '1'; Z <= '1'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '0'; Y <= '1'; Z <= '0'; wait for 10 ns;

X <= '1'; Y <= '1'; Z <= '0'; wait for 10 ns;

X <= '1'; Y <= '1'; Z <= '1'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '0'; wait for 10 ns;

X <= '0'; Y <= '0'; Z <= '1'; wait for 10 ns;

X <= '0'; Y <= '1'; Z <= '1'; wait for 10 ns; lOMoAR cPSD| 58815430

X <= '1'; Y <= '1'; Z <= '1';

wait for 10 ns; wait; end process; end sim; 4.5: Kết quả.

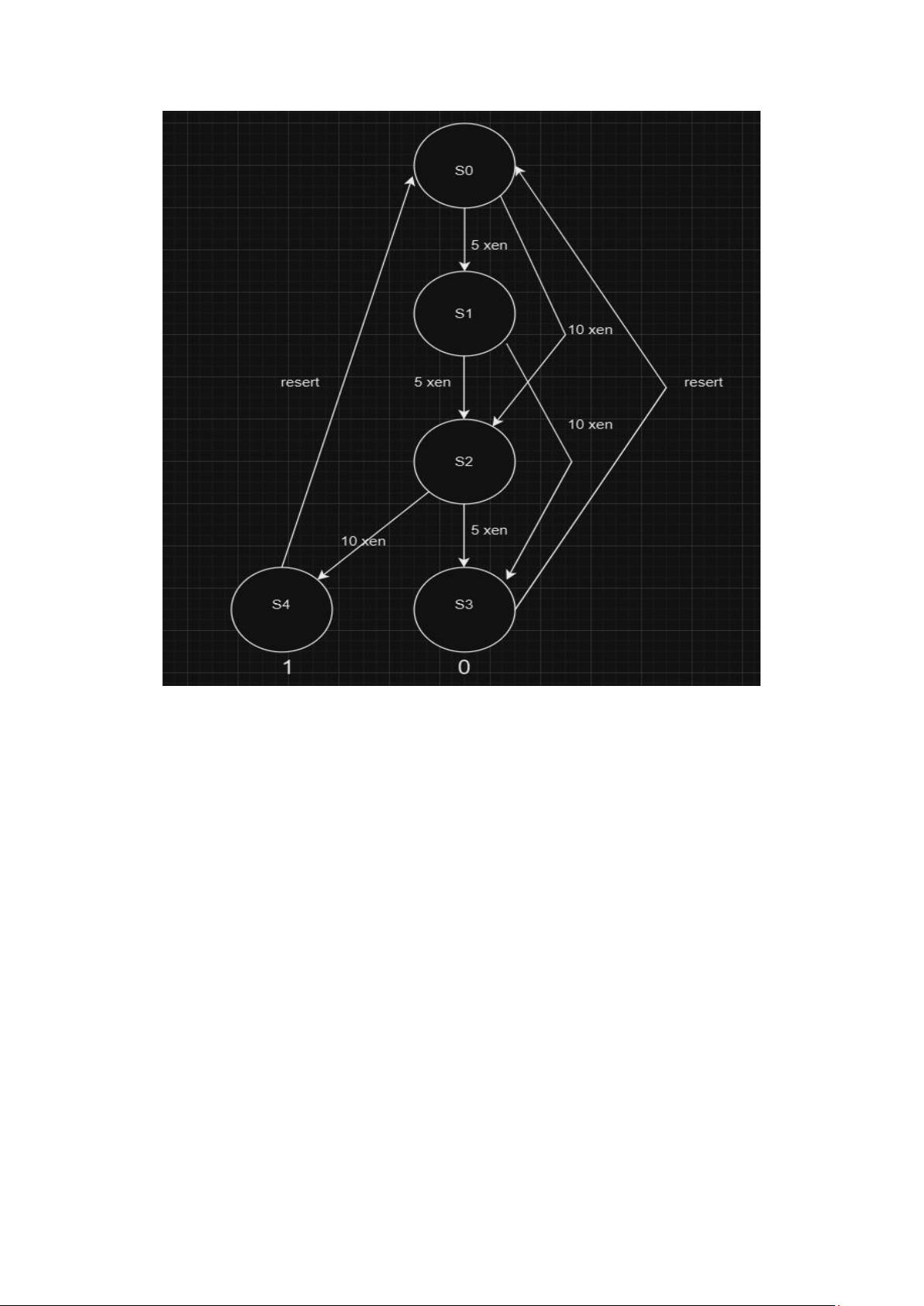

bài 5. Viết mô tả VHDL (Entity và Architecture) và testbench để kiểm tra hoạt

động của mạch có chức năng như sau: Một máy bán hàng tự động chấp nhận 2

loại tiền xu khác nhau: đồng 5 xen và đồng 10 xen. Sản phẩm có giá là 15 xen

và máy chỉ cho phép người mua cho từng đồng xu một vào. Khi có ít nhất 15

xen được cho vào, sản phẩm sẽ được đưa ra. Nếu có nhiều hơn 15 xen được đưa

vào, máy sẽ trả lại tiền thừa. Khi sản phẩm đã được đưa ra, máy sẽ quay trở lại

trạng thái đợi để sản phẩm tiếp theo được mua. Viết testbench để kiểm tra hoạt động của mạch. 1. Ý tưởng: -giá sản phẩn 15 xen

-tín hiệu vào CLK, resert,coin pay(5 xen , 10 xen)

-SP ra, return( trả tiền thừa)

-các trạng thái s0,s1,s2,s3,s4

Từ s0-s2 cần thêm tiền và s3,s4 đưa ra sp trả tiền thừa và resert lại s0 2. Sơ đồ trạng thái: lOMoAR cPSD| 58815430 3. VHDL code library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL;

----------------------------------- Entity bai5 IS Port (clk: in std_logic; Reset: in std_logic; CoinPay: in std_logic; SP : out std_logic; CoinReturn: out std_logic ); End bai5;

----------------------------------architecture Behavioral of bai5 IS

Type status is (S0, S1, S2, S3, S4);

Signal Sreg, next_Sreg: status:= s0; signal flag : std_logic:='0'; begin