Preview text:

lOMoAR cPSD| 58815430

HỌC VIỆN CÔNG NGHỆ BƯU CHÍNH VIỄN THÔNG

---------------------------------------------------

BÁO CÁO BÀI TẬP LỚN

MÔN HỌC: THIẾT KẾ LOGIC SỐ Họ và tên

: Đoàn Như Đăng - B21DCDT035

: Nguyễn Việt Hoàng – B21DCDT101 Nhóm lớp : 03 Nhóm bài tập : 05

Giảng viên : TS. Trần Thị Thúy Hà Hà Nội - 2024 lOMoAR cPSD| 58815430 MỤC LỤC

Bài 1: Viết chương trình điều khiển 8 LED nháy dịch theo mã vòng. Viết testbench

để kiểm tra hoạt động của mạch...................6

1.1. Mô hình hệ thống.......................................................................................6

1.2. Sơ đồ khối...................................................................................................6

1.3. Nguyên lý làm việc.....................................................................................6

1.4. Mã VHDL và Testbench............................................................................7

1.4.1. Mã VHDL............................................................................................7

1.4.2. Testbench.............................................................................................7

1.5. Kết quả.......................................................................................................9

Bài 2: Viết chương trình mô tả bộ đếm lùi Mod 9 (CLK, CLR, Pause) dùng trigơ JK.

Viết testbench để kiểm tra hoạt động của mạch.........................9

2.1. Mô hình hệ thống.......................................................................................9

2.2. Sơ đò khối.................................................................................................10

2.3. Nguyên lý làm việc...................................................................................10

2.4. Mã VHDL và Tesstbench.........................................................................11

2.4.1 Mã VHDL...........................................................................................11

2.4.2. Testbench...........................................................................................14

2.5. Kết quả.....................................................................................................15

Bài 3: Viết chương trình mô tả bộ đếm lùi BCD từ 59 đến 00 - hiển thị trên LED 7

đoạn Anode chung (CLK, CLR). Viết testbench để kiểm tra hoạt động

của mạch.........................................................................................................15

3.1. Mô hình hệ thống.....................................................................................15

3.2. Sơ đồ khối.................................................................................................16

3.3. Nguyên lý làm việc...................................................................................16

3.4. Mã VHDL và Testbench..........................................................................17

3.4.1. Mã VHDL..........................................................................................17

3.4.2. Testbench...........................................................................................18

3.5. Kết quả.....................................................................................................20

Bài 4: Viết chương trình mô tả bộ phân kênh 1:16 (Enable hoạt động ở mức thấp).

Viết testbench để kiểm tra hoạt động của mạch..............................................20

4.1. Mô hình hệ thống.....................................................................................20

4.2. Sơ đồ khối.................................................................................................21 lOMoAR cPSD| 58815430

4.3. Nguyên lý làm việc...................................................................................21

4.4. Mã VHDL và Testbench..........................................................................22

4.4.1. Mã VHDL..........................................................................................22

4.4.2. Testbench...........................................................................................23

4.5. Kết quả.....................................................................................................24

Bài 5. Viết mô tả VHDL (Entity và Architecture) cho mạch đó. Viết testbench để

kiểm tra hoạt động của mạch..........................................................................24

5.1 sơ đồ khối..................................................................................................24

5.2 Phân tích....................................................................................................25

5.2.1 Trigger JK...........................................................................................25

5.2.2 Toàn mạch..........................................................................................25

5.3 nguyên lý làm việc....................................................................................25

5.4 Mã VHDL và Testbench...........................................................................26

5.4.1 Mã VHDL...........................................................................................26

5.4.2 Testbench............................................................................................28

5.5 Kết quả......................................................................................................29 lOMoAR cPSD| 58815430

Bài 1: Viết chương trình điều khiển 8 LED nháy dịch theo mã vòng. Viết

testbench để kiểm tra hoạt động của mạch. 1 .

.1 Mô hình hệ thống Mục tiêu của bài tập 1

này là thiết kế một mạch điều khiển 8 LED nháy theo mã vòng. 8 2 7 3 6 4 Hoạt

động theo mã vòng: Có nghĩa là 8 led hoạt 5

động theo tính chất quay và tuần hoàn của mã vòng, ví dụ 8bit

trên mỗi bit là 1 con led, bit MSB đang là 0

sẽ quay trái, 0 chuyển về làm bit LSB các bit còn lại tịnh tiến về bên trái, công việc

này được thực hiện tuần hoàn.

● Testbench: Một môi trường thử nghiệm được tạo ra để kiểm tra hoạt động của mạch điều khiển 8 led. 1.2. Sơ đồ khối -

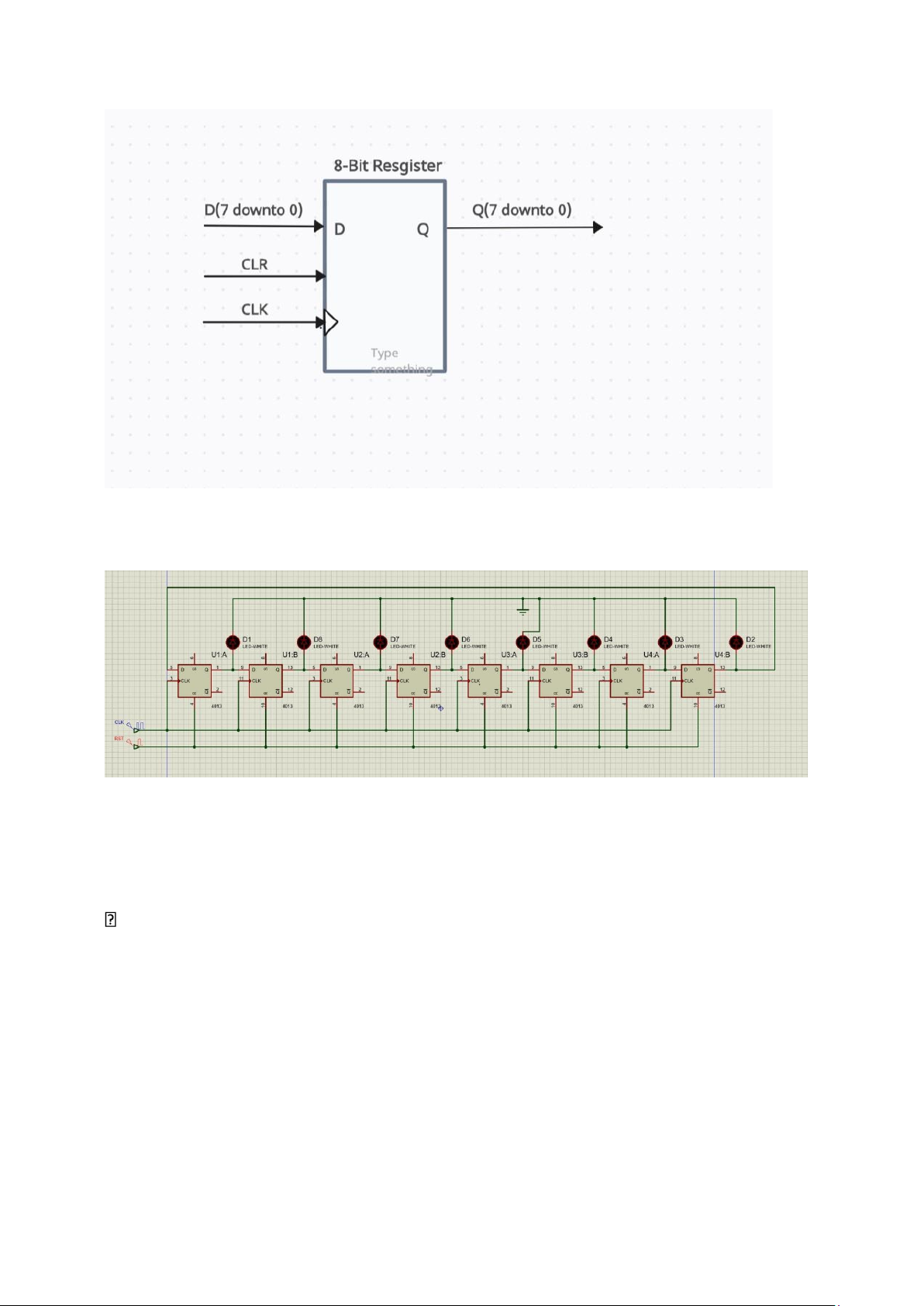

Bài sử dụng thanh ghi dịch 8 bit được cấu tạo từ các trigger D nối tiếp nhau.

Nhưng để 8 led có thể nháy dịch vòng thì đầu ra của trigger D thứ 8 phải nối vào

đầu vào của trigger đầu tiên.

Sơ đồ khối của thanh ghi dịch 8 bit: lOMoAR cPSD| 58815430 -

Sơ đồ khối của mạch dịch vòng 8 led:

1.3. Nguyên lý làm việc của mạch dịch vòng

8 Flip-Flop D: Mỗi flip-flop điều khiển một LED. Đầu ra Q của mỗi flipflop sẽ

điều khiển một LED. Các flip-flop được mắc nối tiếp nhau để tạo thành mạch dịch vòng. ●

CLK: Xung nhịp được đưa vào để điều khiển flip-flop dịch chuyển giá trị từ

đầu vào D sang đầu ra Q. ●

CLR: Khi tín hiệu reset được kích hoạt, trạng thái ban đầu của các flipflop sẽ

được thiết lập (ví dụ: flip-flop đầu tiên có giá trị "1", các flip-flop còn lại có giá trị "0"). lOMoAR cPSD| 58815430 ● Q: Là đầu ra.

Mạch hoạt động theo nguyên tắc sau: ●

Khi bắt đầu (hoặc khi có tín hiệu reset), flip-flop đầu tiên (D0) có giá trị "1"

và các flip-flop còn lại có giá trị "0". ●

Sau mỗi xung clock, giá trị "1" sẽ được dịch chuyển từ flip-flop này sang flip-

flop khác, tạo ra hiệu ứng nháy dịch trên 8 LED theo thứ tự.

●Khi giá trị "1" dịch đến flip-flop cuối cùng (D7), nó sẽ quay lại flip-flop đầu tiên

(D0) và tiếp tục dịch vòng. lOMoAR cPSD| 58815430

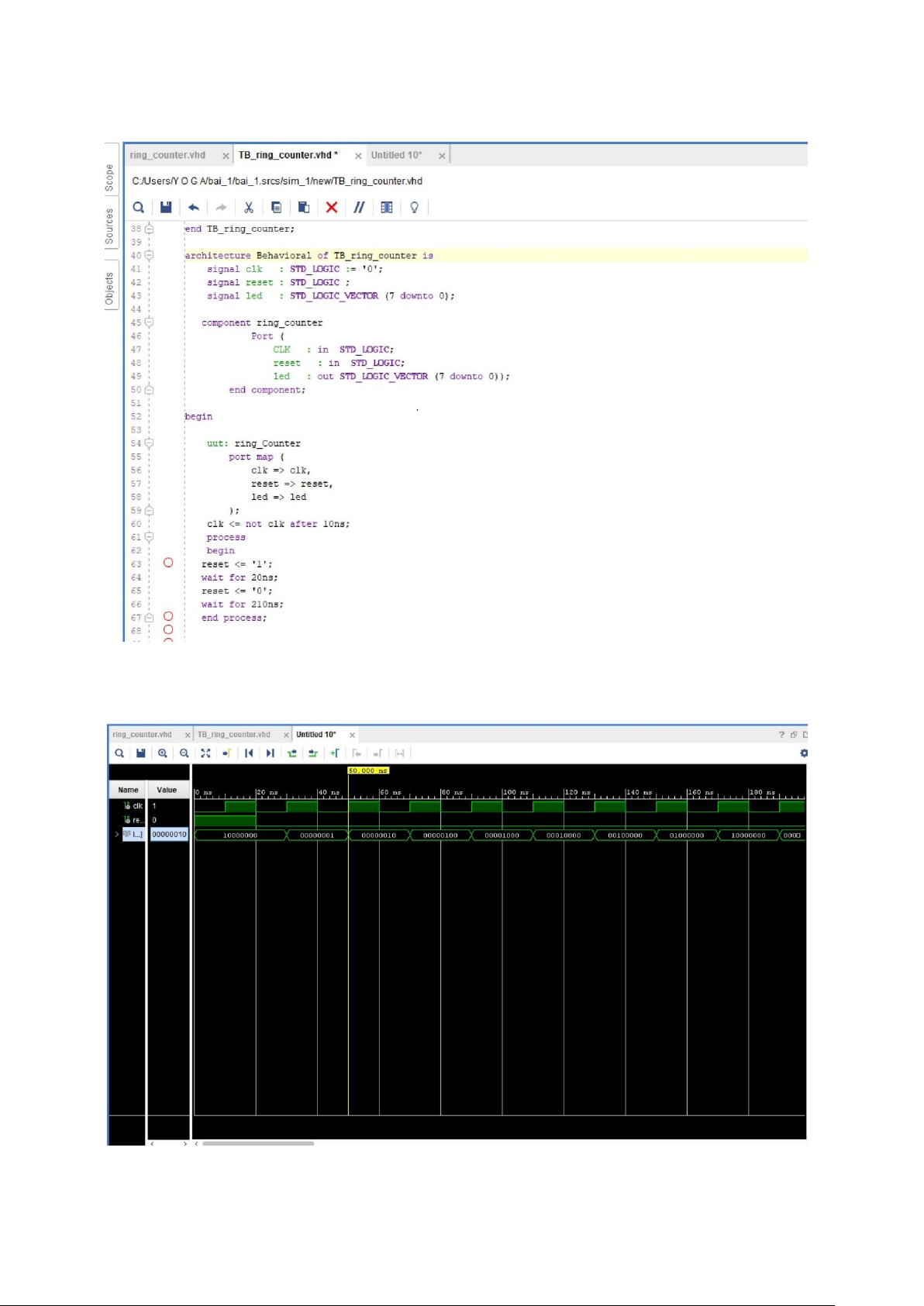

1.4. Mã VHDL và Testbench 1.4.1. Mã VHDL lOMoAR cPSD| 58815430 1.4.2. Testbench 1.5. Kết quả lOMoAR cPSD| 58815430

Bài 2: Viết chương trình mô tả bộ đếm lùi Mod 9 (CLK, CLR, Pause) dùng trigơ JK.

Viết testbench để kiểm tra hoạt động của mạch.

2.1. Phân tích hệ thống

Hệ thống bao gồm một bộ đếm lùi MOD 9 sử dụng Flip-flop JK. Bộ đếm này có

khả năng đếm lùi từ 8 về 0 và có tính năng tạm dừng (Pause) và xóa (Clear).

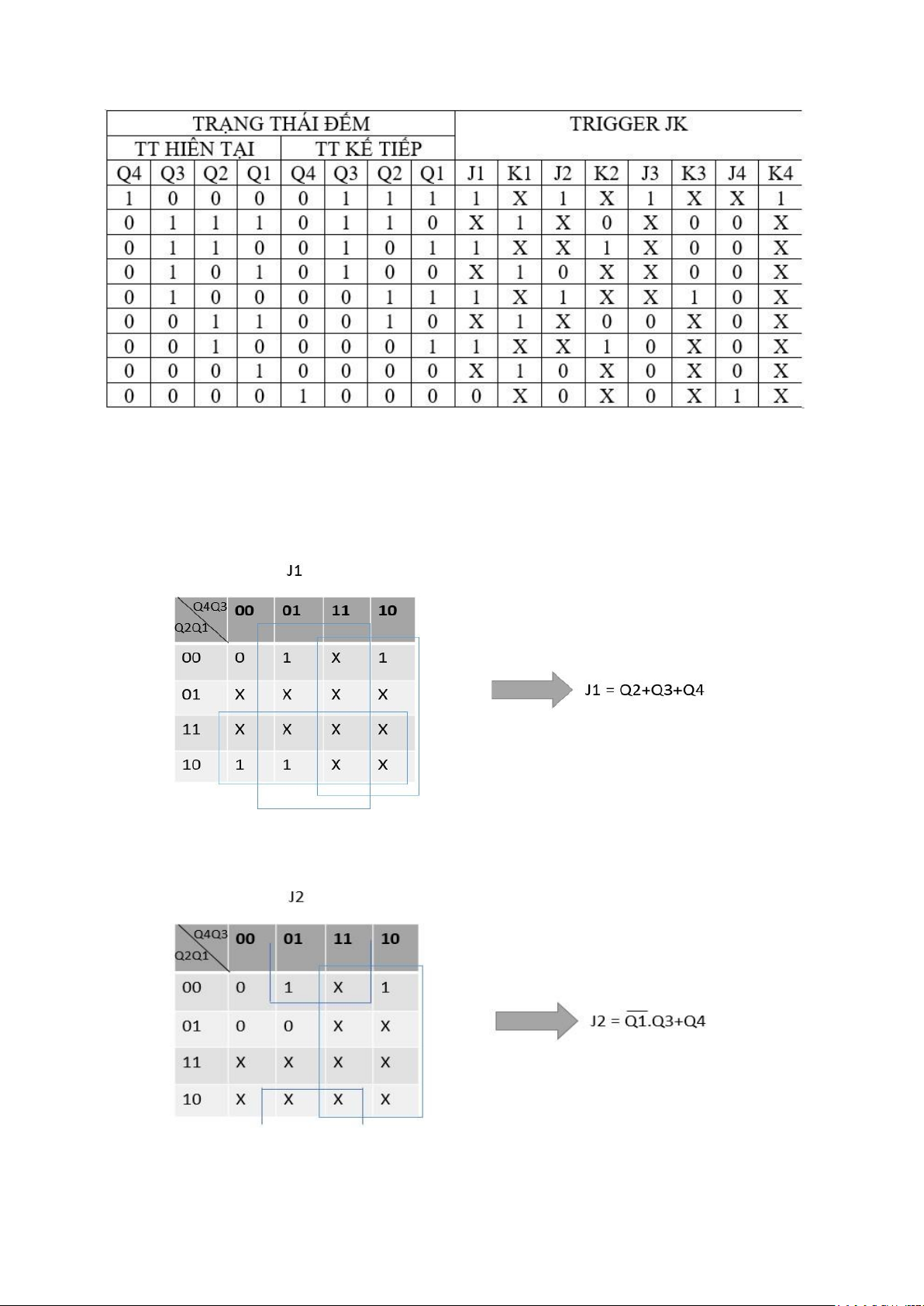

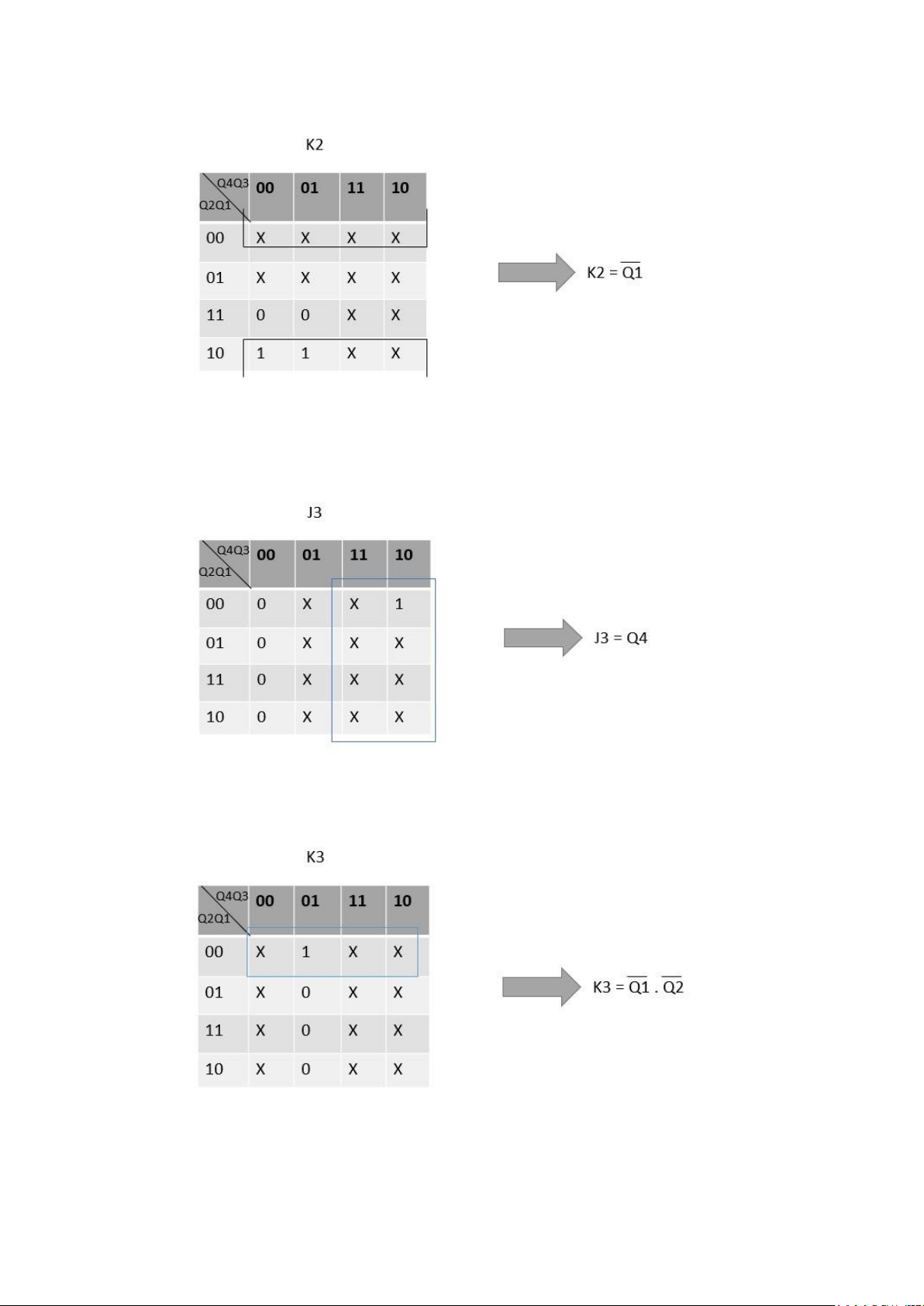

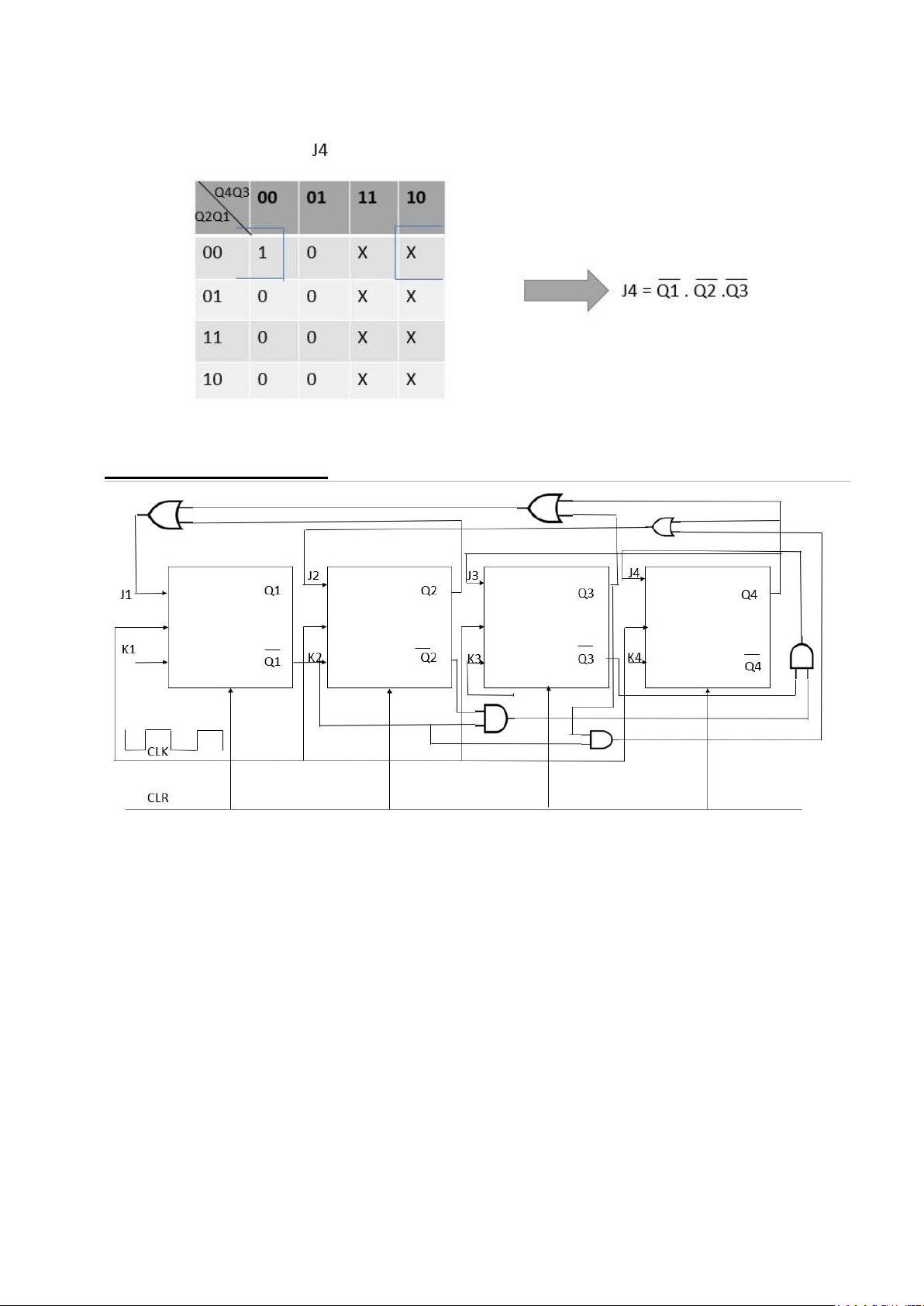

Mạch chính của hệ thống này bao gồm bốn Flip-flop JK (FF1, FF2, FF3 và FF4)

được kết nối để tạo thành bộ đếm MOD 9. Mỗi Flip-flop JK nhận tín hiệu Clock

(CLK), tín hiệu J và K, tín hiệu Clear (CLR) và tín hiệu Pause từ mạch điều khiển.

Khi Pause được kích hoạt, bộ đếm sẽ tạm dừng và không thực hiện bất kỳ hoạt

động nào. Khi Clear được kích hoạt, bộ đếm sẽ được đặt lại về giá trị ban đầu.

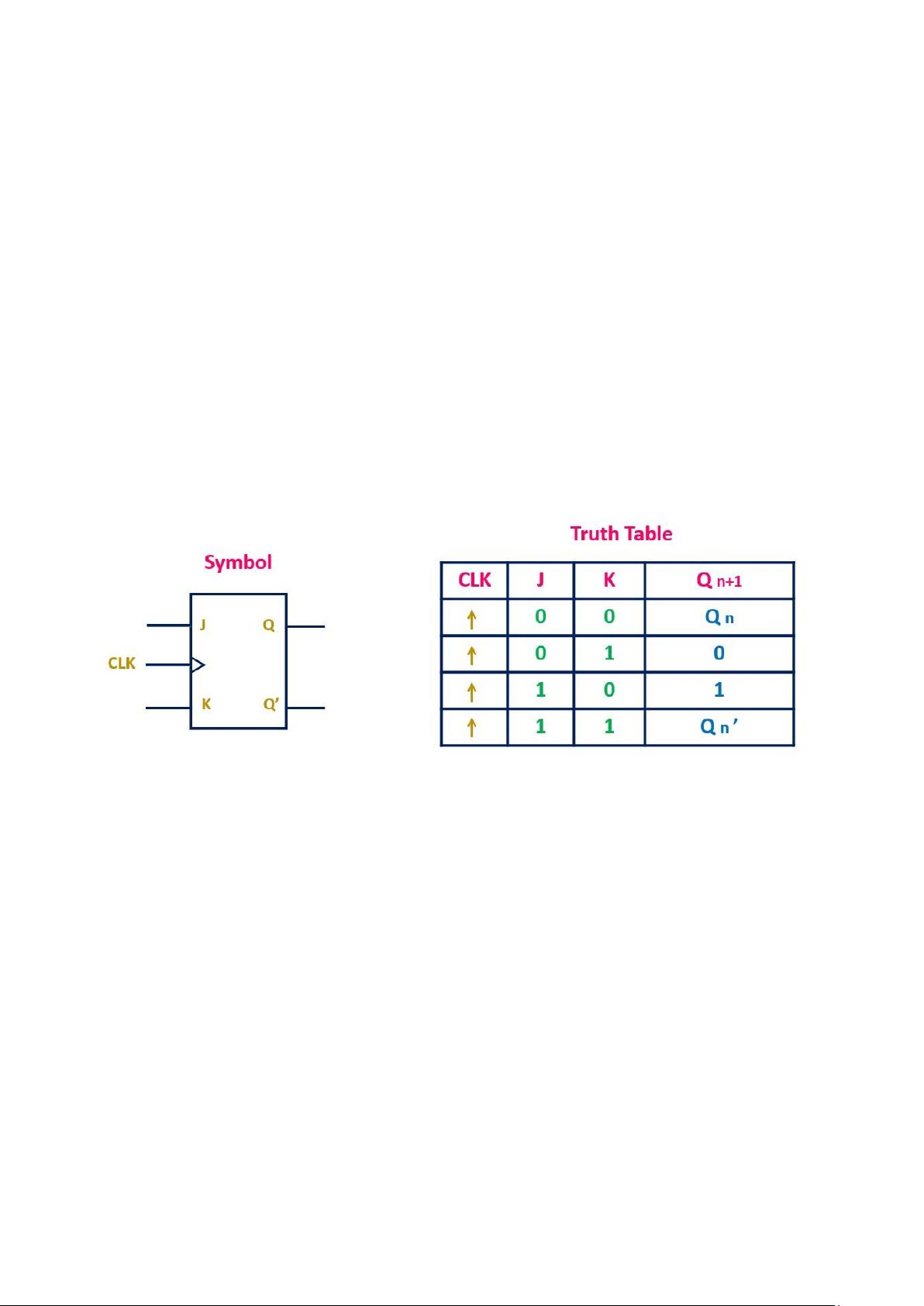

2.2. Mô hình hệ thống Trigger JK:

2.3. Nguyên lý làm việc ●

Bộ đếm lùi MOD 9 sử dụng trigger JK được xây dựng bằng cách kết nối 4 trigger JK lại với nhau. ●

Mỗi trigger JK nhận tín hiệu Clock (CLK) chung. ●

Tín hiệu Clear (CLR) được sử dụng để đặt lại bộ đếm về giá trị ban đầu khi được kích hoạt. ●

Tín hiệu J và K cho trigger JK được tính toán dựa trên các đầu ra của trigger khác. lOMoAR cPSD| 58815430

Tín hiệu Clock (CLK):

Tín hiệu Clock được cung cấp từ bên ngoài và là tín hiệu đồng hồ chính để đồng bộ

hóa hoạt động của bộ đếm. Mỗi lần xung Clock (lên và xuống cạnh dương), mạch

đếm sẽ thực hiện một bước đếm.

Tín hiệu Clear (CLR):

Tín hiệu Clear có tác dụng đặt lại bộ đếm về giá trị ban đầu. Khi CLR được kích

hoạt (giá trị '1'), tất cả các Flip-flop JK trong bộ đếm sẽ được đặt về giá trị '0'.

Tín hiệu Pause:

Tín hiệu Pause cho phép tạm dừng hoạt động của bộ đếm. Khi Pause được kích

hoạt (giá trị '1'), các Flip-flop JK sẽ không thực hiện bất kỳ bước đếm nào, và bộ

đếm sẽ tạm dừng tại giá trị hiện tại.

Tín hiệu J và K cho trigger JK:

Tín hiệu J và K cho mỗi Flip-flop JK được tính toán dựa trên các đầu ra của Flip-

flop trước đó và các tín hiệu Clear và Pause.

Bộ đếm lùi MOD 9:

Các Flip-flop JK được kết nối với nhau để tạo thành bộ đếm lùi MOD 9.

Khi chạy mạch, ứng với mỗi xung Clock, bộ đếm sẽ thực hiện một bước đếm, và

giá trị đếm lùi MOD 9 sẽ được cập nhật tương ứng. Khi Pause được kích hoạt, bộ

đếm tạm dừng, và khi Clear được kích hoạt, bộ đếm sẽ đặt lại về giá trị ban đầu.

Nguyên lý này đảm bảo tính chính xác và kiểm soát của bộ đếm lùi MOD 9 trong mạch.

Bảng trạng thái: 00 → 0X 10 → X1 01 → 1X 11 → X0 lOMoAR cPSD| 58815430 Lập bảng karnaugh: K1 = ‘1’ K4 = ‘1’ lOMoAR cPSD| 58815430 lOMoAR cPSD| 58815430 MÔ HÌNH HỆ THỐNG lOMoAR cPSD| 58815430

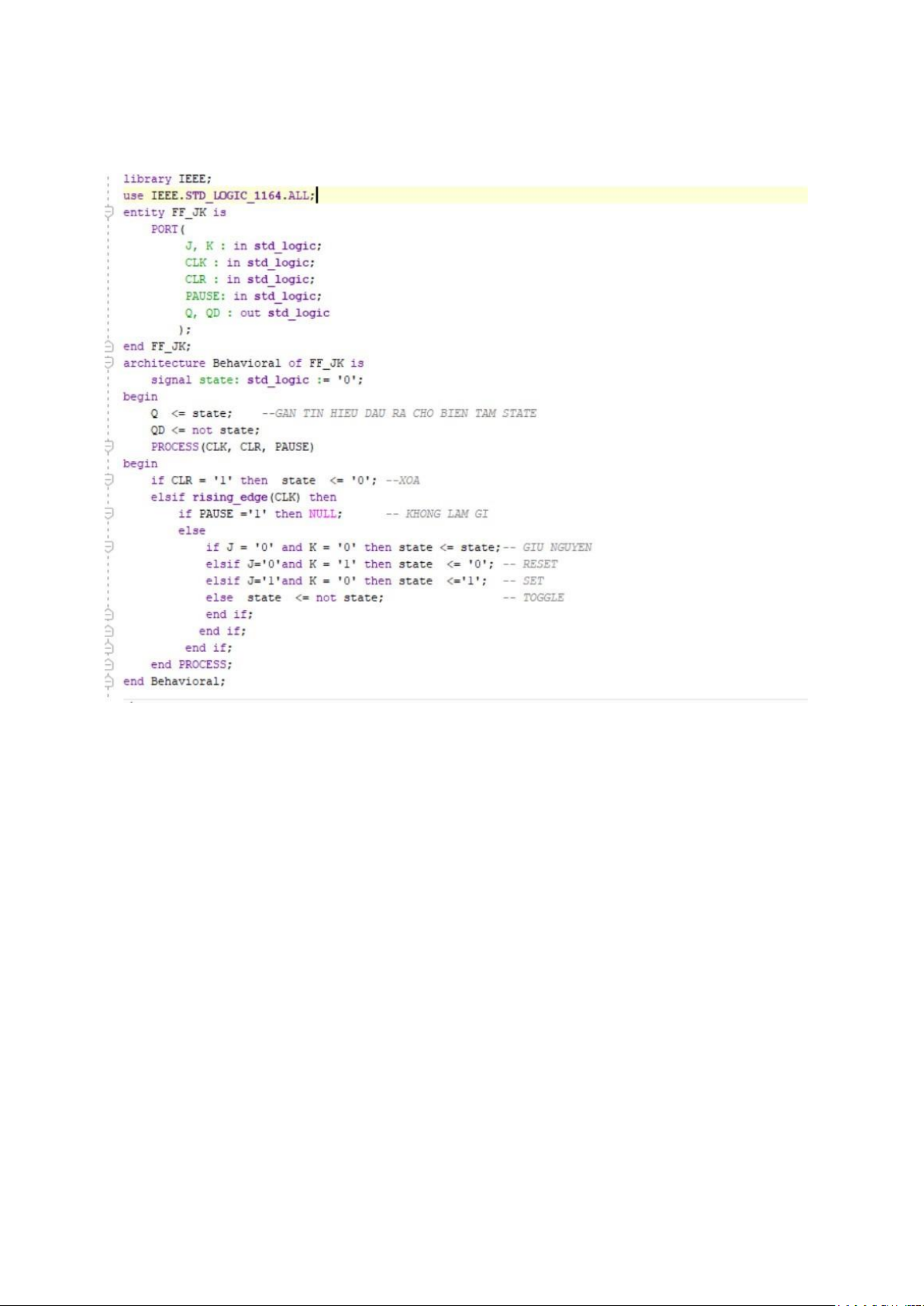

2.4. Mã VHDL và Tesstbench 2.4.1 Mã VHDL Trigger JK lOMoAR cPSD| 58815430

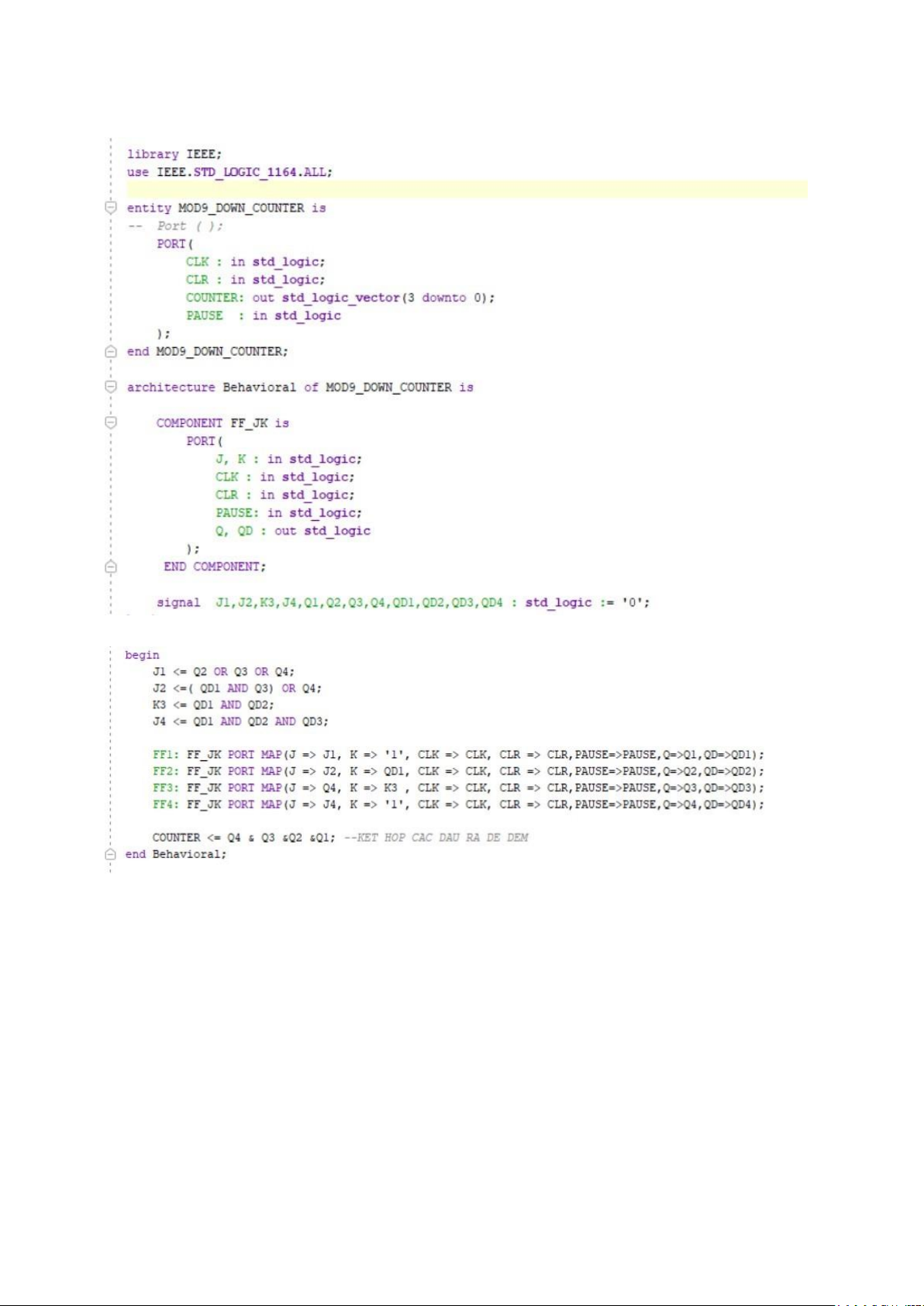

2.4.2. Mã VHDL của chương trình chính lOMoAR cPSD| 58815430

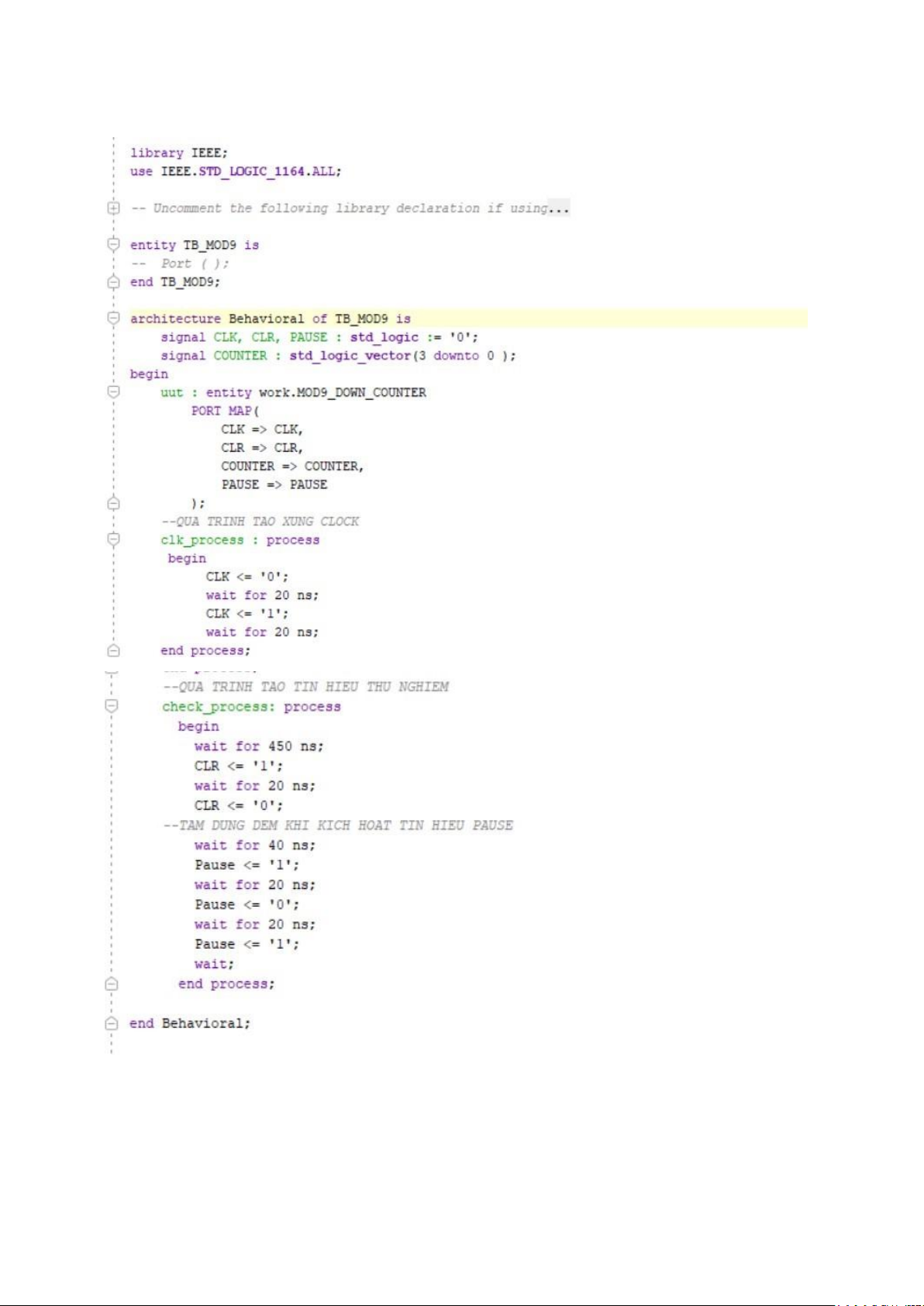

2.4.3. Mã VHDL của chương trình chính lOMoAR cPSD| 58815430 2.5. Kết quả

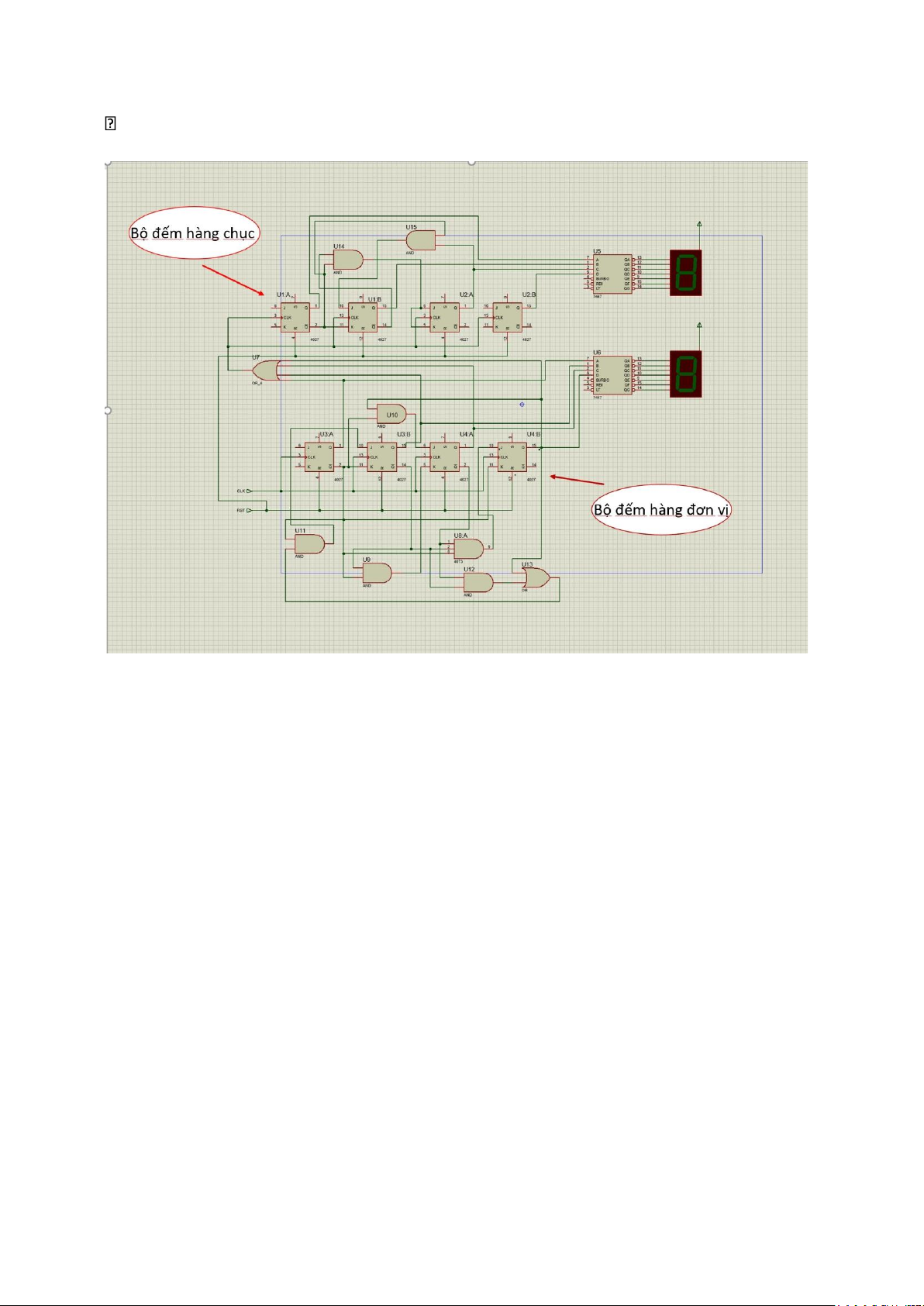

Bài 3: Viết chương trình mô tả bộ đếm lùi BCD từ 59 đến 00 - hiển thị trên LED 7

đoạn Anode chung (CLK, CLR).

Viết testbench để kiểm tra hoạt động của mạch.

3.1. Mô hình hệ thống

Mục tiêu của bài tập này là thiết kế bộ đếm lùi BCD và hiển thị kết quả trên một

Led 7 đoạn với Anode chung. Hệ thống bao gồm các phần sau: ●

Bộ đếm lùi BCD (): Mạch này đếm từ 9 về 0 theo kiểu BCD (Binary -

Coded Decimal) và hiên thị kết quả trên LED 7 đoạn. Nó nhận tín hiệu clock

(CLK) để kiểm soát việc đếm, tín hiệu Clear (CLR) dể đặt lai bộ đếm. ●

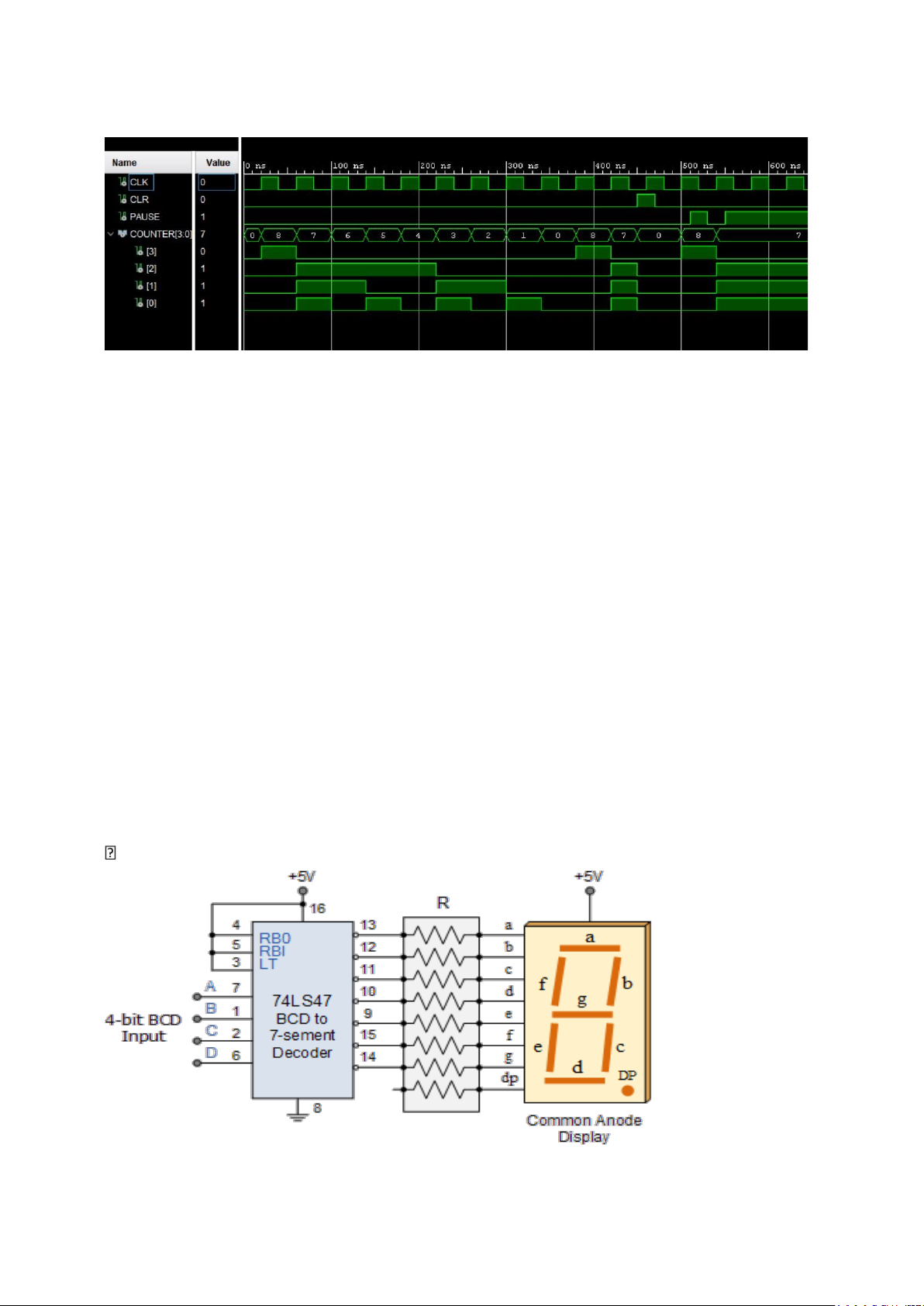

Led 7 đoạn Anode chung: khi đếm số sẽ được hiển thị trên led 7 đoạn

thông qua bộ giả mã binary to seg 3.2. Sơ đồ khối

Khối giải mã binary 4bit sang (Binary Coded Decimal) sang 7 đoạn lOMoAR cPSD| 58815430

Sơ đồ mạch điện

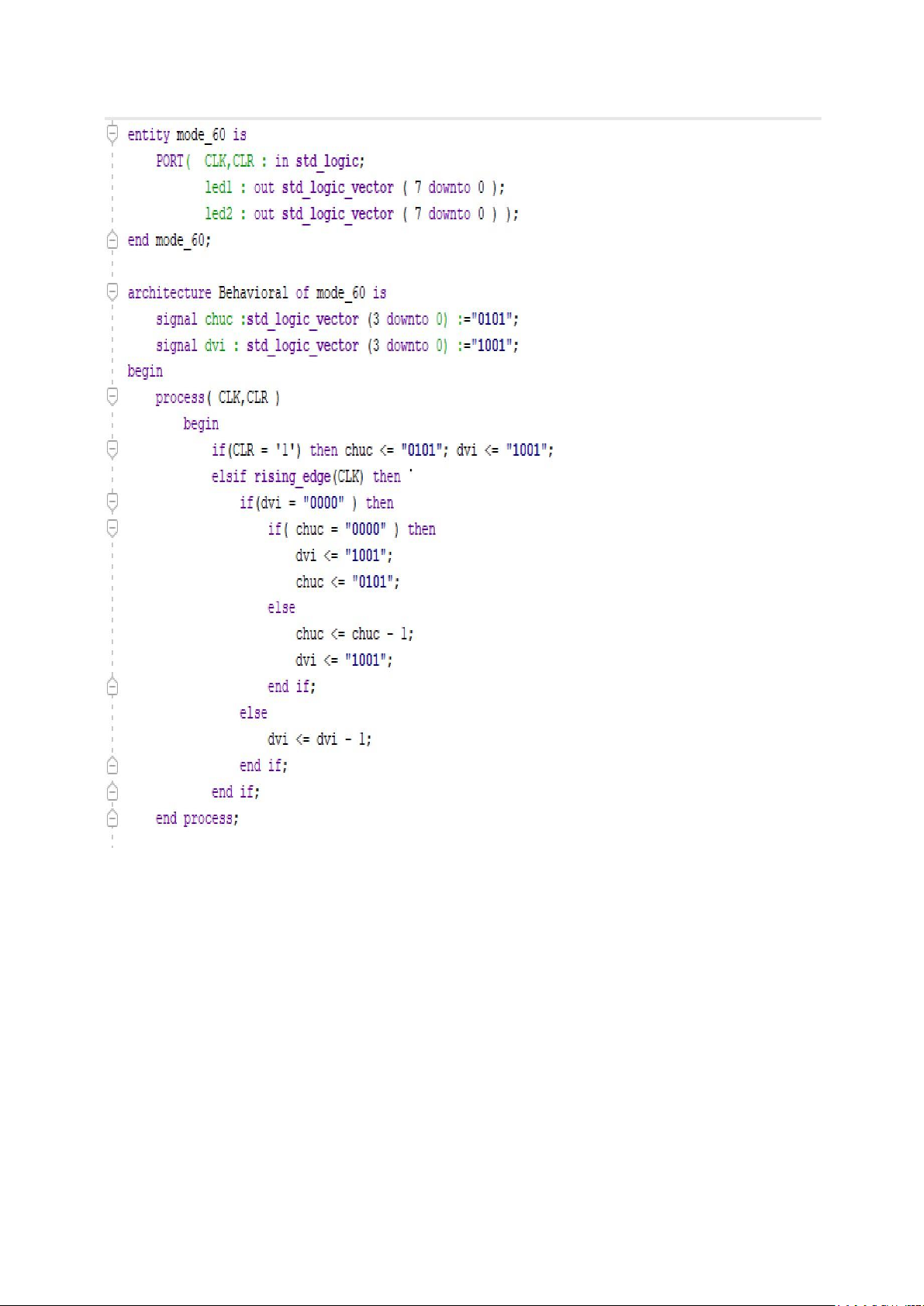

3.3. Nguyên lý làm việc

Bộ đếm lùi BCD (BCD_DownCounter_SSDAnode) ● CLK:

Tín hiệu clock điều khiển việc đếm. ●

CLR: Tín hiệu Clear dùng để đặt lại bộ đếm về trạng thái ban đầu. Trong bài

này trạng thái ban đầu led hàng chục là 5, led hàng đơn vì là 9. ●

Led_out: Đầu ra đến LED 7 đoạn để hiển thị kết quả

Mạch bộ đếm lùi BCD hoạt động theo nguyên tắc sau: ●

Khi tín hiệu CLR được kích hoạt (CLR = 1), bộ đếm sẽ đặt lại về trạng thái

ban đầu ( hàng chục bằng 5, hàng đơn vị sẽ bằng 9) . lOMoAR cPSD| 58815430 ●

Khi có tín hiệu xung CLK bộ đếm hàng đơn vị sẽ thực hiện đếm lùi từ 9 về 0. ●

Sau khi bộ đếm hàng đơn vị đếm đến 0 thì cấp xung clock cho bộ đếm hàng

chục, nghĩa là sau 1 chu kì đếm của bộ đếm hàng đơn vị thì bộ đếm hàng chục mới

thay đổi trạng thái 1 lần.

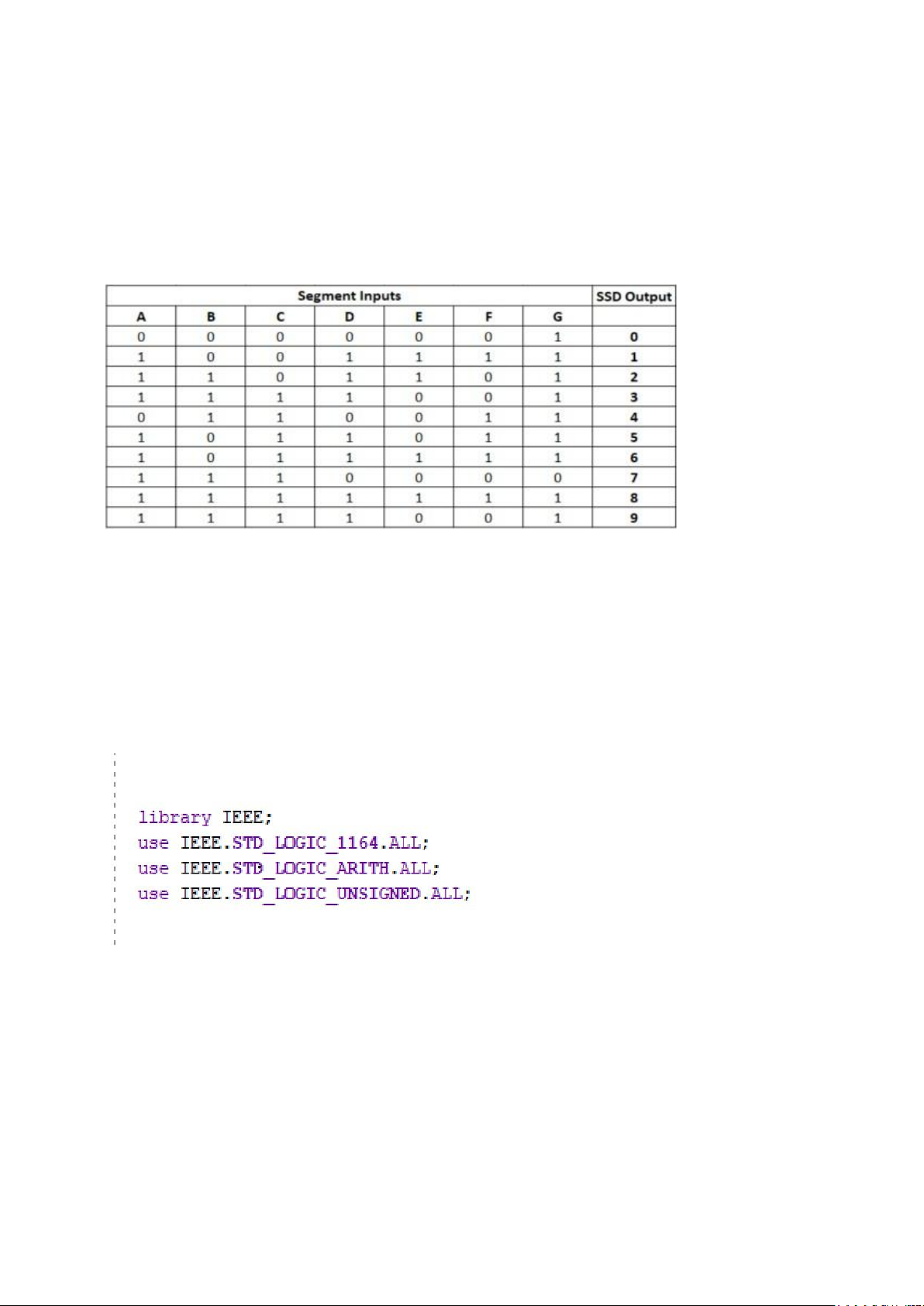

Bảng trạng thái của Led Anode chung

3.4. Mã VHDL và Testbench 3.4.1. Mã VHDL lOMoAR cPSD| 58815430