Preview text:

lOMoAR cPSD| 61548706 BÁO CÁO THỰC HÀNH

IT2140 – 152026 – THỰC HÀNH ĐIỆN TỬ CHO CNTT NỘI DUNG

Tuần 3: Khảo sát mạch lọc RC và mạch RLC nối tiếp Họ và tên Đặng Hoàng Minh Mã số sinh viên 20235777 Nhóm 3

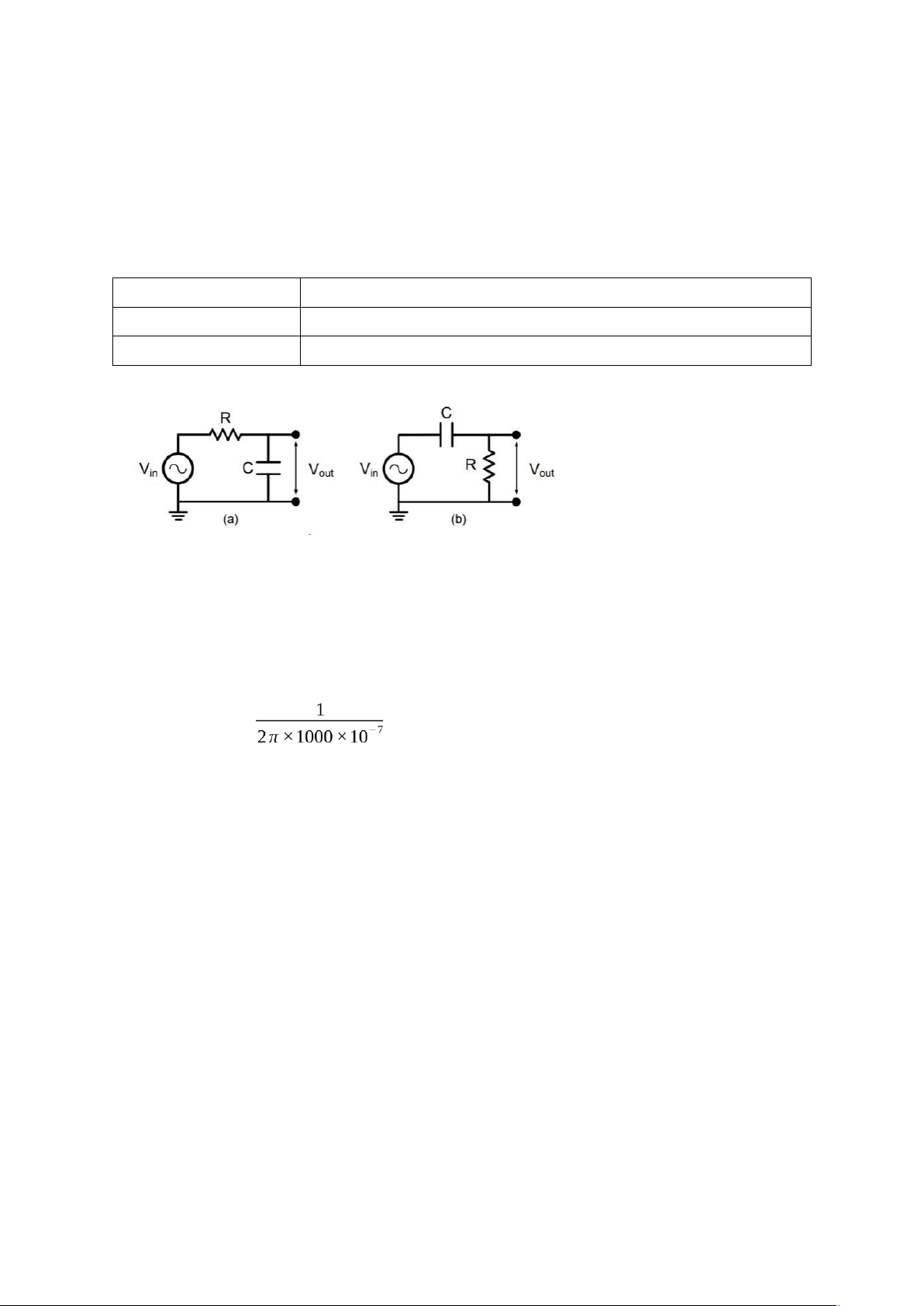

Bài 1: Khảo sát mạch lọc RC thông thấp và thông cao đơn giản

Hình 1 Mạch mô phỏng -

Tính toán tần số tương ứng với mỗi R và C + R: 1kΩ + C: 0.1uF

Tần số cắt lý thuyết : fo = = = 1591,55Hz -

Lắp mạch theo sơ đồ trên với Vs= 5V – chụp mạch hoàn thiện lOMoAR cPSD| 61548706 - Kết quả đo: f (Hz) 1 10 100 10k 100k

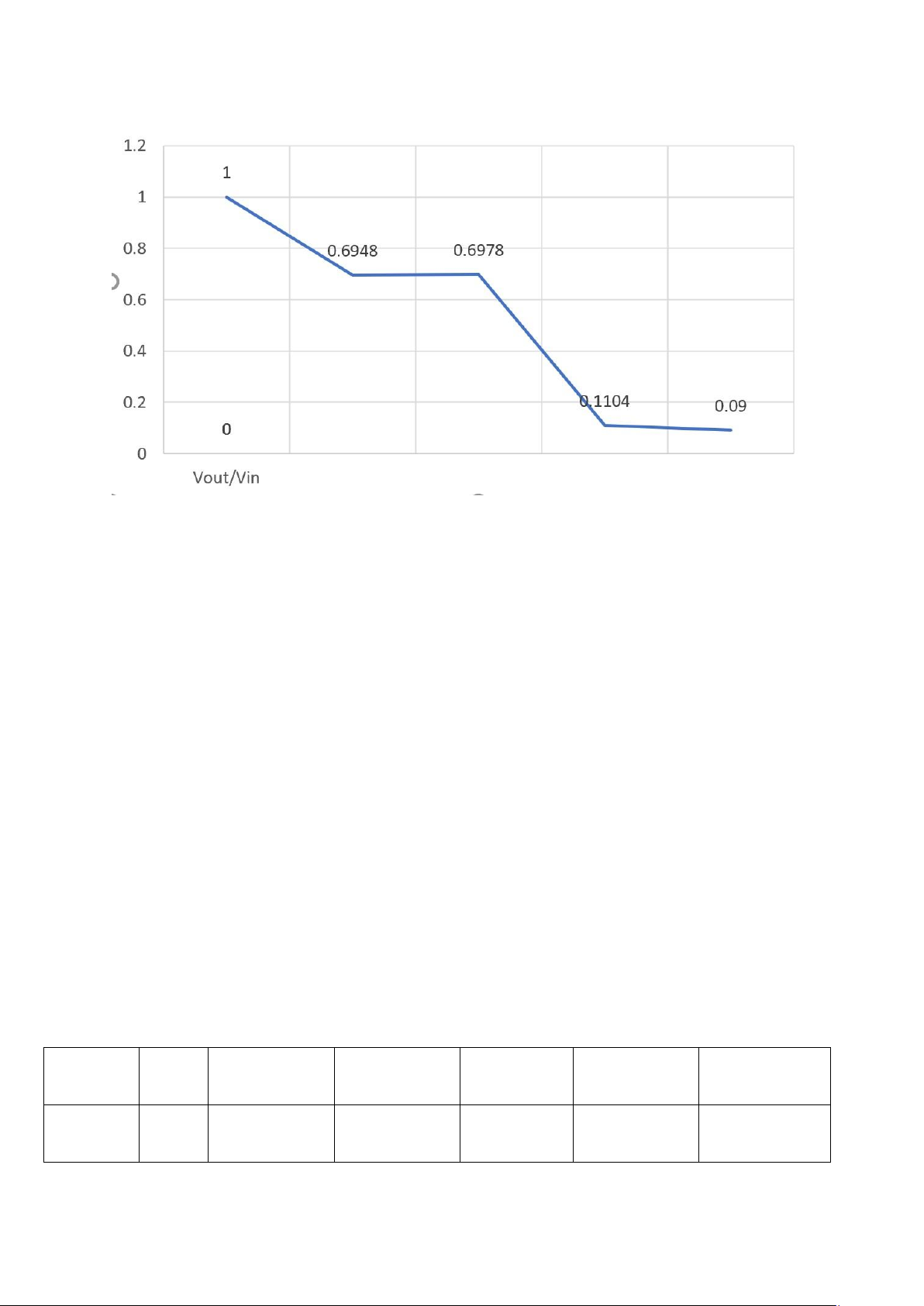

Lý thuyết V0/Vin 4.9999999/5 4.9999/5 4.99/5 0.786/5 0.0796/5 Không đo 0.6948 0.6978 0.1104 0.09 Thực tế V0/Vin được -

Đồ thị mạch lọc thông thấp dựa trên kết quả đo: lOMoAR cPSD| 61548706 -

So sánh với kết quả lý thuyết và nhận xét: Nhận xét : -

Về lý thuyết : Mạch lọc thông thấp cho phép tín hiệu tần số thấp đi quamà

không bị suy giảm đáng kể, trong khi tín hiệu có tần số cao hơn Tần số cắt

sẽ bị suy giảm. Tần số cắt lý thuyết được tính là khoảng 159 kHz, đây là

tần số tại ứng dụng đầu tiên bằng một nửa ứng dụng đầu vào. -

So sánh lý thuyết và thực tế : Kết quả thực tế cho thấy sự khác biệt nhỏ so

với lý thuyết ở tần số thấp (1 Hz đến 100 Hz), với các giá trị điện áp đầu ra

gần như không suy giảm so với điện áp vào. Tuy nhiên, ở tần số 10kHz và

100kHz, điện áp đầu ra suy giảm đáng kể, phù hợp với đặc điểm của mạch lọc thông thấp. - Giải thích sai số :

+ Ở các tần số thấp, kết quả đo khá chính xác, gây nhiễu ảnh hưởng và

sai số công cụ đo ở mức thấp.

+ Ở tần số cao hơn, sai lệch giữa lý thuyết và thực tế xuất hiện. Điều này

có thể gây nhiễu từ môi trường bên ngoài và đặc tính tuyến tính của các tình

huống như điện trở lại và tụ điện khi hoạt động ở tần số cao. Sự nhiễu và suy

hao trên đường truyền cũng góp phần tạo ra sai số. f (Hz) 1 10 100 10k 100k

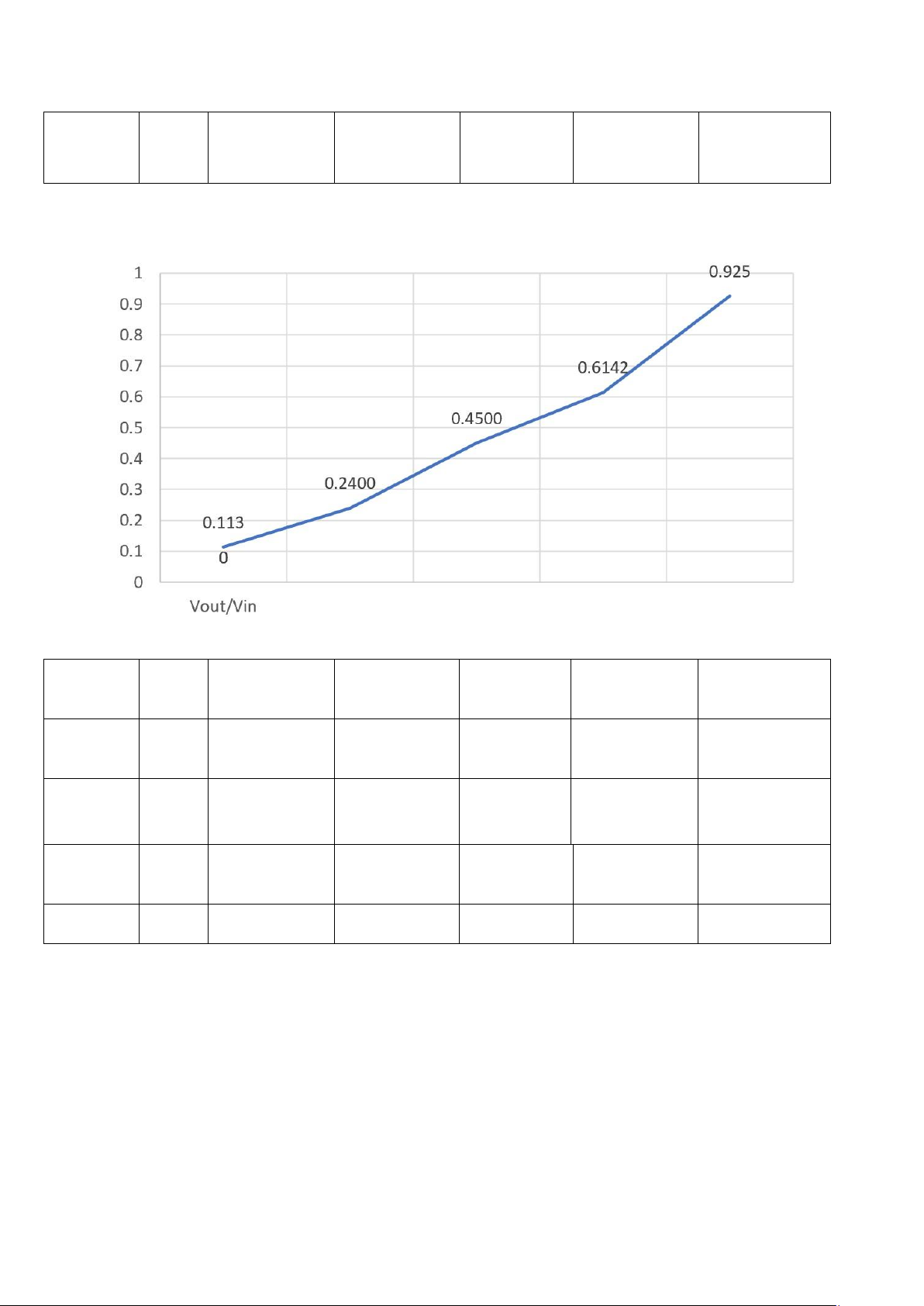

Lý thuyết V0/Vin 4.9999999/5 4.9999/5 4.99/5 0.786/5 0.0796/5 lOMoAR cPSD| 61548706 Không đo 0.6948 0.6978 0.1104 0.09 Thực tế V0/Vin được -

Đồ thị mạch lọc thông cao dựa trên kết quả đo: -

So sánh với kết quả lý thuyết và nhận xét: f (Hz) 1 10 100 10k 100k Lý thuyết V0/Vin 0.003142/5 0.031415/5 0.31354/5 4.93785/5 4.999367/5 Không đo Không đo Không đo 0.925 0.958 Thực tế V0/Vin được được được f (Hz) 1000 2000 3000 3678 10k Thực tế V0/Vin 0.113 0.2400 0.4500 0.6142 0.925 -

Tính toán lý thuyết và so sánh với thực nghiệm kết quả độ lệch pha của

mạch lọc thông thấp và cao, đưa ra nhận xét:

+ Với mạch lọc thông thấp RC, độ dịch pha của Vout so với Vin được tính theo công thức:

φ= −arctan(2πfRC) ≈ - 45°

+ Với mạch lọc thông cao RC, độ dịch pha của Vout so với Vin được tính theo công thức: lOMoAR cPSD| 61548706

φ= −arctan(2πfRC) ≈ - 45° ⟹ Nhận xét: -

Về lý thuyết : Mạch lọc thông cao chỉ cho phép các tần số tín hiệu cao đi

qua, trong khi các tần số tín hiệu bị suy giảm. Đặc điểm này rõ ràng nhất ở

tần số cao, khi điện áp đầu ra đạt gần giá trị điện áp đầu vào. -

So sánh lý thuyết và thực tế : Kết quả đo cho thấy điện áp đầu ra ở tần số

thấp (1 Hz, 10 Hz, 100 Hz) không đo được, điều này phù hợp với lý thuyết

vì mạch lọc thông cao làm suy giảm tần số tín hiệu mạnh. Khi tần số tăng

lên (từ 10kHz đến 100kHz), điện áp đầu tiên bắt đầu tăng lên và tiến gần

đến giá trị điện áp đầu vào, cho thấy chức năng lọc phù hợp của mạch hoạt động. - Giải thích sai số :

Ở tần số thấp, tín hiệu bị suy giảm quá mức không thể đo được. Điều này

phù hợp với lý thuyết vì mạch lọc hiệu quả thông cao trong việc ngăn chặn tần số tín hiệu thấp.

Ở các tần số cao, mặc dù dù điện áp đầu tăng lên gần với lý thuyết giá trị,

vẫn có một số khác biệt nhỏ gây nhiễu và ảnh hưởng của các yếu tố như độ

chính xác của linh kiện và nhiễu đường truyền. Các tình huống không lý tưởng

có thể làm suy giảm tín hiệu ở các tần số cao hơn.

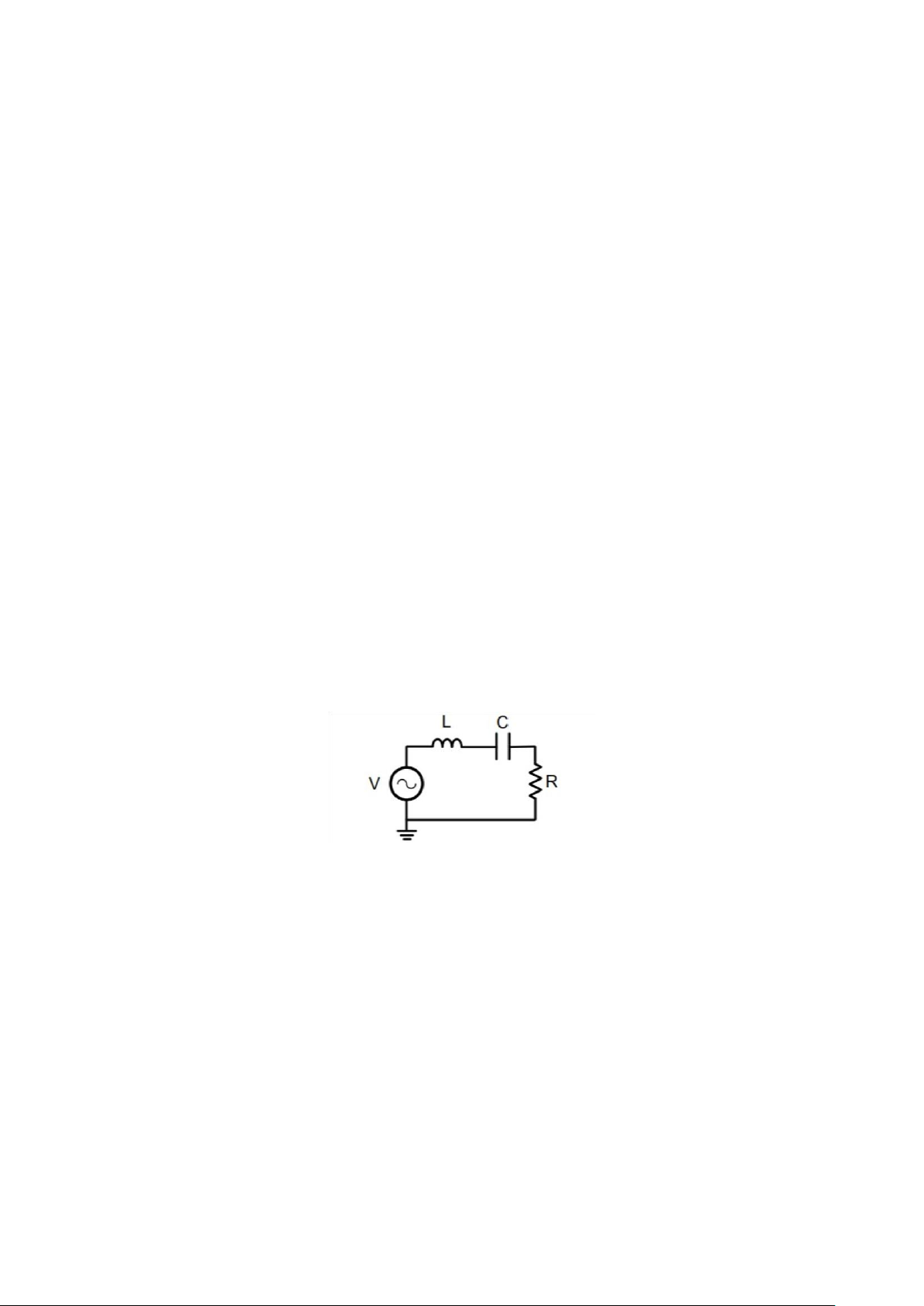

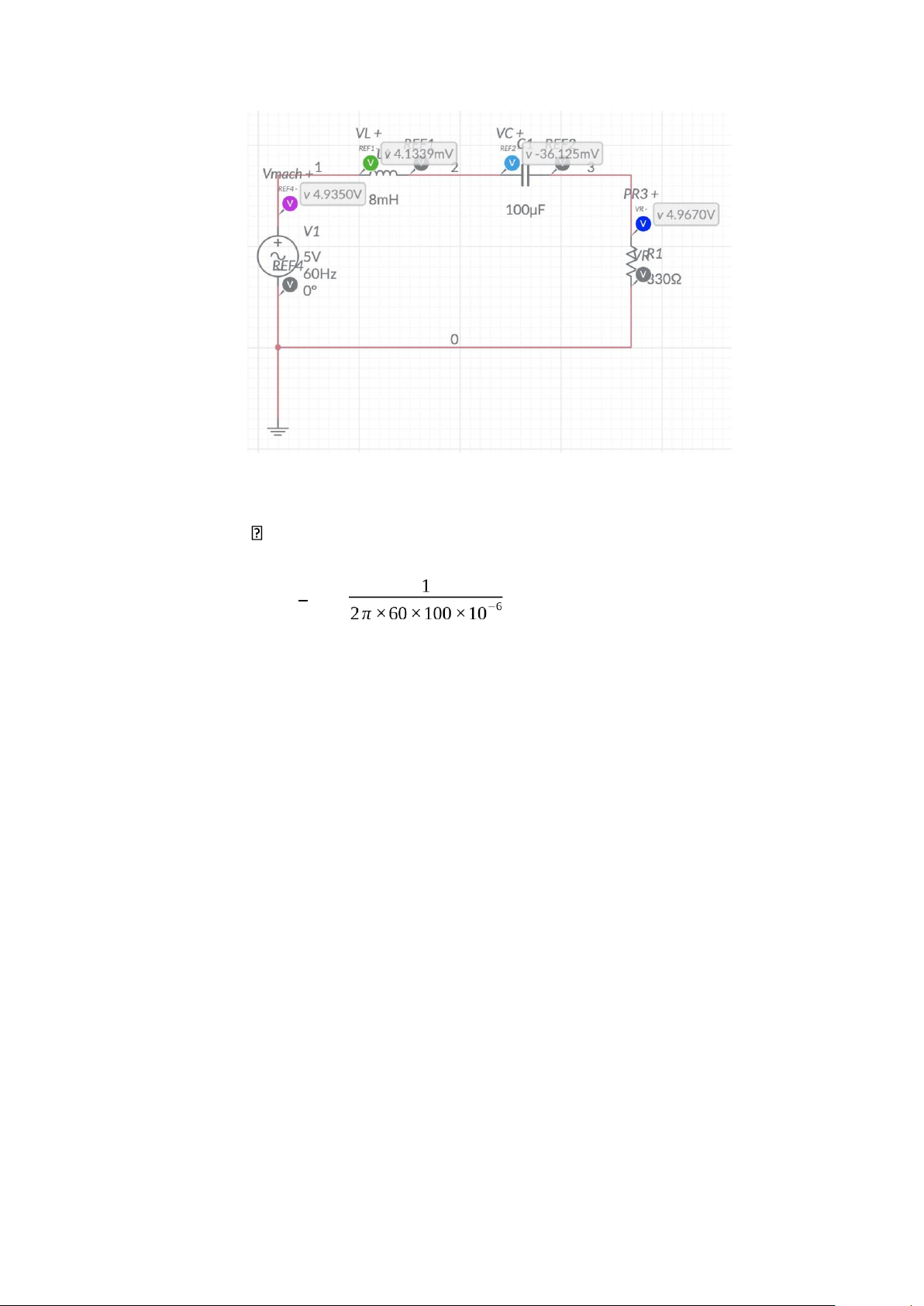

Bài 2: Dùng công cụ mô phỏng khảo sát tính chất mạch RLC a) -

Mô phỏng mạch điện trên (hình mô phỏng): lOMoAR cPSD| 61548706 b) -

Đo độ lệch pha VL, VR, VC so với V, so sánh với kết quả lý thuyết Tính toán lí thuyết

+ ZL = 2πfL = 2π×60×8×10-3 = 3.016Ω 1 + Zc = 2πfC = = 26.52 Ω lOMoAR cPSD| 61548706

+ Độ lệch pha VR so với V : tanϕr = Z LR−Zc =

3.016330−26.52= - 0.071 -> ϕr = -4.07°

→VR nhanh pha hơn V là 4.07°

→VL nhanh pha hơn V là 90° + 4.07° =94.07°

→VC chậm pha hơn V là 90° - 4.07° =85.93°

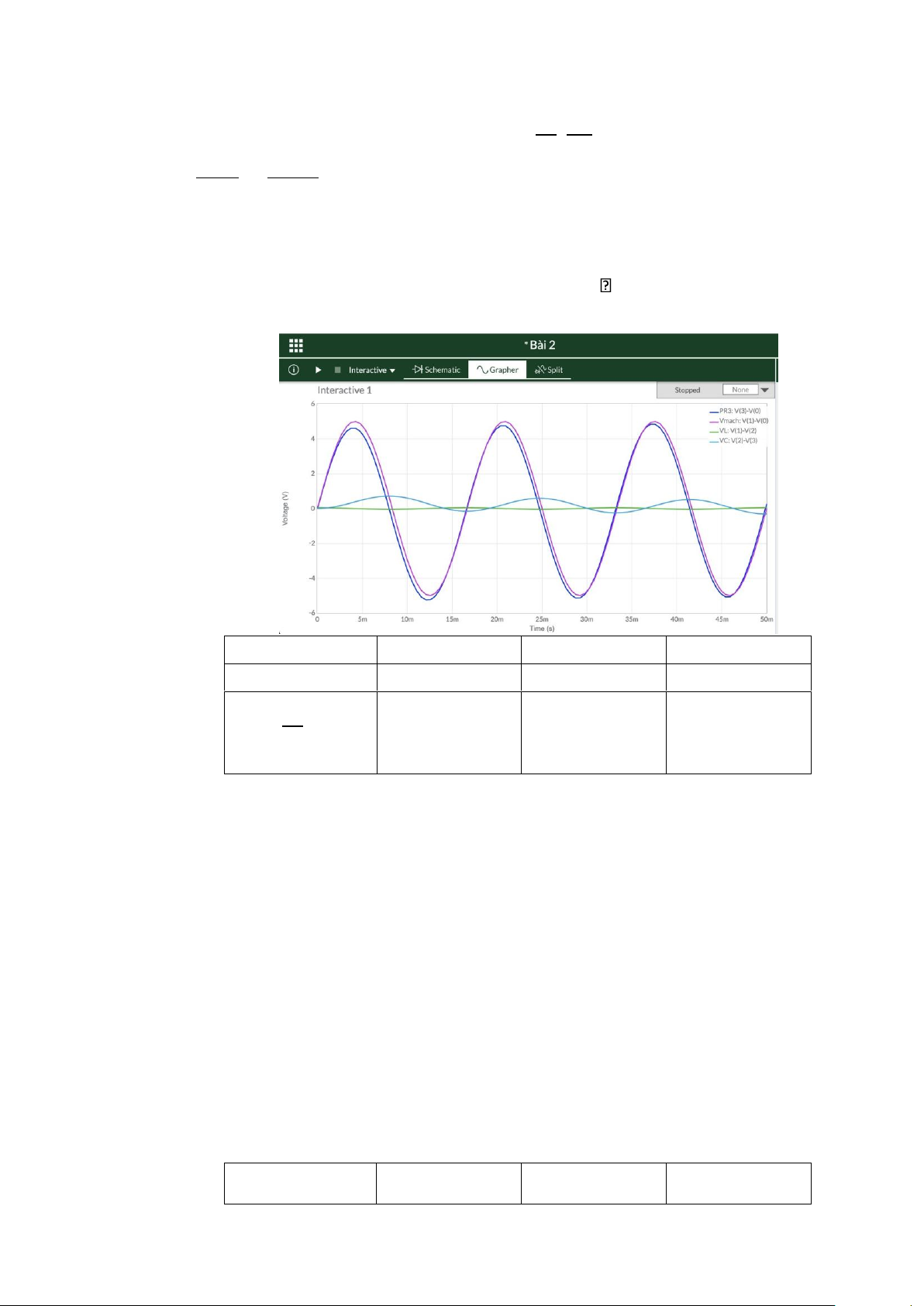

Độ lệch pha theo mô phỏng ∆t 0.00033 0.0045 0.0037 T 0.01667 0.01667 0.01667 5.22o 98.21o 81.18o ∆t ∆ = ϕ T ×360o - Nhận xét

+ Số liệu tính được gần đúng so với thực tế. Tuy nhiên vẫn có sai số do

làm tròn trong quá trình đo và tính toán L.

+ VL và VC lệch pha nhau góc : 98.21+ 81.18=179.39o ~ 180o -> VL nhanh, ngược pha VC .

+ VL và VR lệch pha nhau góc : 98.21 – 7.22 = 90.99o ~90o -> VL nhanh, vuông pha VR .

+ Kết quả đo được đúng với lý thuyết. Từ đó rút ra được các tính chất về

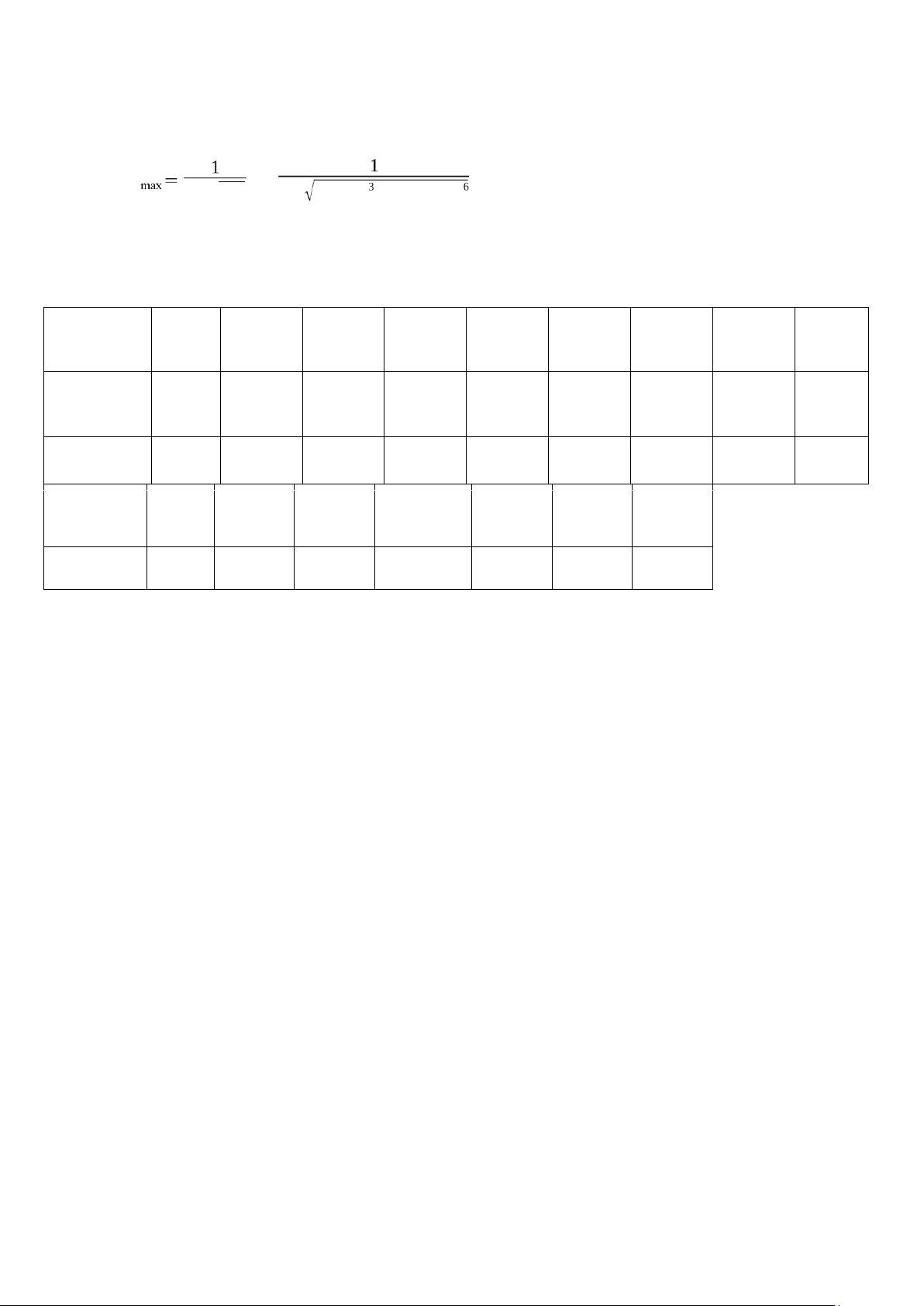

độ lệch pha đều được nghiệm đúng. c) - Thay đổi f, tìm fch R L C lOMoAR cPSD| 61548706

Tần số cộng hưởng lý thuyết: f = = 177,94 (Hz) − − 2π√LC

2π 8×10 ×100×10 f (Hz) 1 10 100 177.94 500 1000 5000 10000 Lý thuyết VR 1.015 4.506 4.997 5 4.989 4.946 3.98 2.744 Thực tế VR 7000(Cự f (Hz) 5000 6000 c đại) 7500 8000 10000 Thực tế VR 1.254 1.405 1.469 1.458 1.417 1.086

- So sánh với kết quả lý thuyết

Dựa vào giá trị f thay đổi thu được, có thể dự đoán fmax sẽ rơi trong khoảng 6000 – 7500Hz. - Nhận xét

+ VR tăng khi f chạy từ 1 đến fmax và giảm khi f chạy từ fmax đến 10kHz. +

Kết quả fmax đo được gần đúng với lí thuyết do sai số do cách chọn điểm cực đại trong multisim

+ Kết quả đo bé hơn so với kết quả tính toán theo lý thuyết, sự sai số này

do ảnh hưởng bởi sai số dụng cụ ,linh kiện lớn và sai số ngẫu nhiên mỗi lần

đo. (do làm tròn trong quá trình đo và tính toán , hao tổn trên R, L và C ,

nhiễu đường truyền…). Từ đó rút ra được tính chất về tần số cộng hưởng

được nghiệm đúng. +Giải thích sai số :

Sự khác biệt giữa tần số cộng hưởng lý thuyết (17,794 Hz) và tần số cực

đại đo thực tế (khoảng 7.000 Hz) có thể làm sai số của các tình huống trong

thực tế, đặc biệt là sai số của cuộn tròn và tụ điện. Ngoài ra, sai số có thể xuất ra

từ môi trường đo, cách kết nối dây hoặc sai lệch nhỏ trong quá trình chọn điểm

cực đại khi thực hiện mô phỏng.

Mạch RLC cũng rất nhạy cảm với tần số nhiễu từ môi trường, có thể ảnh

hưởng đến kết quả đo.