Preview text:

lOMoAR cPSD| 58815430

HỌC VIỆN CÔNG NGHỆ BƯU CHÍNH VIỄN THÔNG

KHOA KỸ THUẬT ĐIỆN - ĐIỆN TỬ

BÁO CÁO BÀI TẬP LỚN

MÔN: THIẾT KẾ LOGIC SỐ

Giảng viên hướng dẫn : TS. Trần Thúy Hà Nhóm lớp : 04 Nhóm bài tập: 30

Sinh viên thực hiện: Cao Duy Hậu lOMoAR cPSD| 58815430

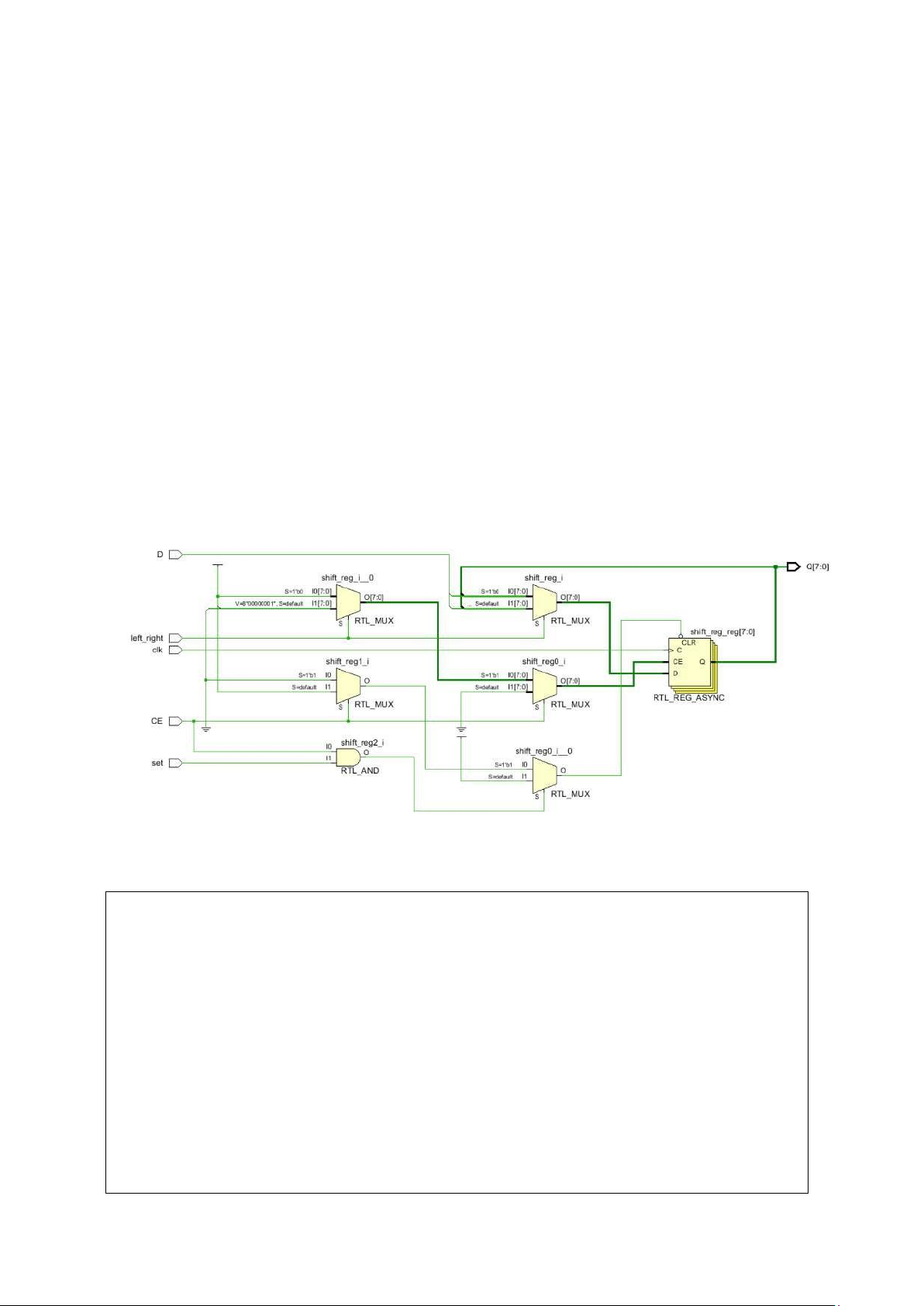

Bài 1 :Viết mô tả VHDL cho IC ghi dịch 8 bit hoạt ộng tại sườn dương của

Clock, có tín hiệu chốt Clock (CE) mức tích cực cao, Tín hiệu lập không ồng bộ

mức tích cực cao. Viết testbench ể kiểm tra hoạt ộng của mạch Ý tưởng :

- Đây là mạch ghi dịch 8 bit và hoạt ộng tại sườn dương của clock

- Có tín hiệu chốt CE ở mức tích cực cao ( CE=’1’)

- Thiết lập tín hiệu lập không ông bộ (set=’1’ thì tất cả dữ liệu thanh ghi trả về 0)

- Thiết lập tín hiệu left_right ể thấy sự dịch bit Mạch dự kiến Code VHDL library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity shift_register is

Port ( D : in STD_LOGIC; CE : in STD_LOGIC; clk : in

STD_LOGIC; set : in STD_LOGIC; left_right: in STD_LOGIC;

Q : out STD_LOGIC_VECTOR (7 downto 0)); end shift_register; lOMoAR cPSD| 58815430

architecture Behavioral of shift_register is signal shift_reg :

STD_LOGIC_VECTOR (7 downto 0); begin process (CLK, CE, set) begin if CE='1' then

if set='1' then shift_reg<=(others=>'0'); elsif ( clk'event and clk='1') then if (left_right='0')then

shift_reg<=shift_reg(6 downto 0)& D; else

shift_reg<= shift_reg(7 downto 1) & D; end if; end if; end if; end process;

Q<= shift_reg; end Behavioral; Testbench library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity shift_register_tb is end shift_register_tb;

architecture Behavioral of shift_register_tb is component shift_register

Port ( D, CE, CLK, set, left_right: in STD_LOGIC; Q : out

STD_LOGIC_VECTOR (7 downto 0)); end component;

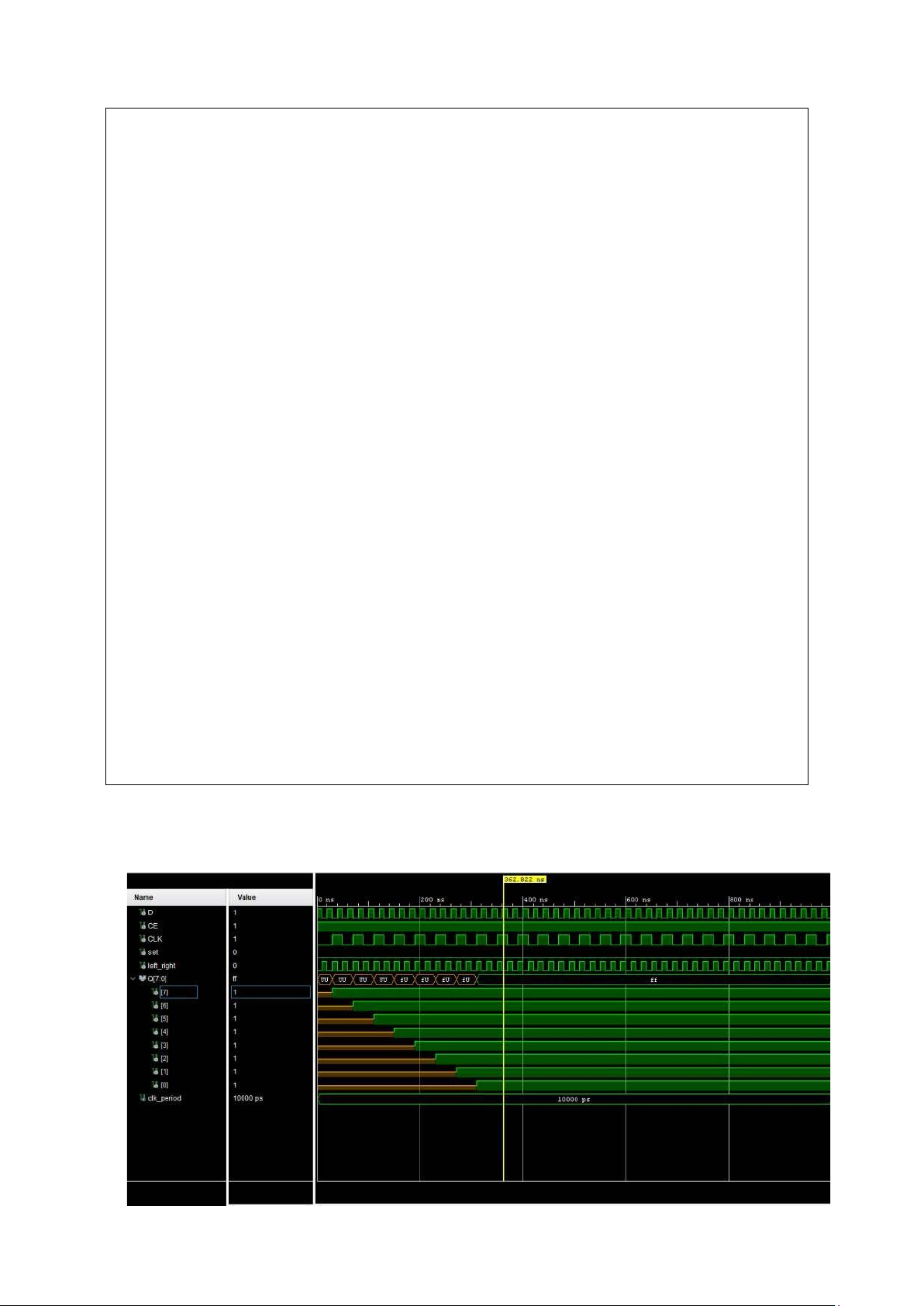

signal D: std_logic :='0'; signal CE :std_logic :='0'; signal CLK

:std_logic :='0'; signal set :std_logic :='0'; signal left_right :std_logic

:='0'; signal Q :std_logic_vector (7 downto 0); constant clk_period : time := 10ns; begin

uut: shift_register port map ( clk=>clk, lOMoAR cPSD| 58815430

CE=>CE, set=>set, D=>D,

left_right=>left_right, Q=>Q); stimulus_process: process begin

D<='1'; CE<='1'; set<='0'; left_right<='0'; wait for 10 ns ;

D<='0'; left_right <='1'; wait for 10 ns;

CLK<=not CLK after 10ns; end process; ENd; Kết quả lOMoAR cPSD| 58815430 Bài 2: Ý tưởng

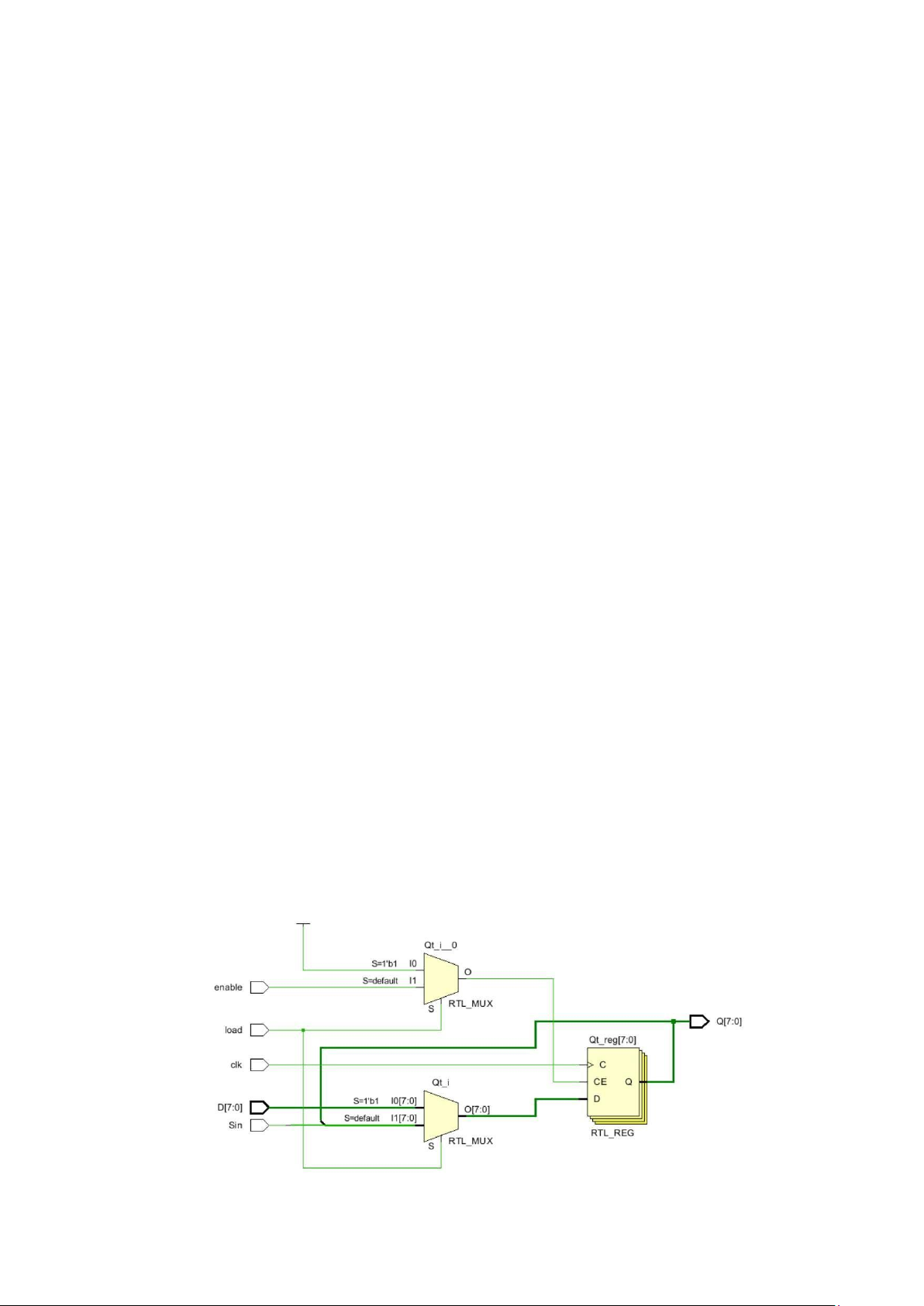

- Bài toán cần 5 ầu vào

- Tín hiệu Sin óng vai trò là tín hiệu ầu vào

- Tín hiệu Q là tín hiệu logic có N-1 bit

- Tín hiệu clock tạo xung

- Tín hiệu enable là tín hiệu kích hoạt dịch trái hay phải

- Tín hiệu load là tín hiệu nạp

- Bài toán chỉ hoạt ộng ở sườn dương ở xung clock khi tín hiệu load ược

kích hoạt thì dữ liệu của ầu vào sẽ ược gán vào giá trị của thanh ghi ,

ngược lại nếu tín hiệu enable ược kích hoạt sẽ tiến hành dịch trái hoặc

phải tùy vào tín hiệu của shift_right Mạch dự kiến lOMoAR cPSD| 58815430 CODE VHDL

Thanh ghi dịch N bit nối tiếp, nạp song song library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity reg_shift is generic ( N : integer := 8 ); port ( Sin : in std_logic;

D : in std_logic_vector (N-1 downto 0); clk, load, enable : in std_logic;

Q : out std_logic_vector (N-1 downto 0) ); end reg_shift;

architecture Behavioral of reg_shift is

signal Qt : STD_LOGIC_VECTOR(N - 1 downto 0); begin

process(clk) begin if (clk'event and clk = '1') then if (load = '1') then Qt <= D;

elsif enable = '1' then for i in 0 to N-2 loop Qt(i) <= Qt(i+1); end loop; Qt(N-1) <= Sin; end if;

end if; end process; Q <= Qt; end Behavioral; Testbench lOMoAR cPSD| 58815430 library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity tb_ShiftRight is end tb_ShiftRight;

architecture behavior OF tb_ShiftRight IS component reg_shift port ( Sin : in std_logic;

D: in std_logic_vector(7 downto 0);

clk : in std_logic ; load : in std_logic ; enable : in std_logic ;

Q : out std_logic_vector (7 downto 0) ); end component;

-- inputs signal Sin : std_logic := '0'; signal D : std_logic_vector(7 downto

0) := (others => '0'); signal clk : std_logic := '0'; signal load : std_logic :=

'0'; signal enable : std_logic := '0';

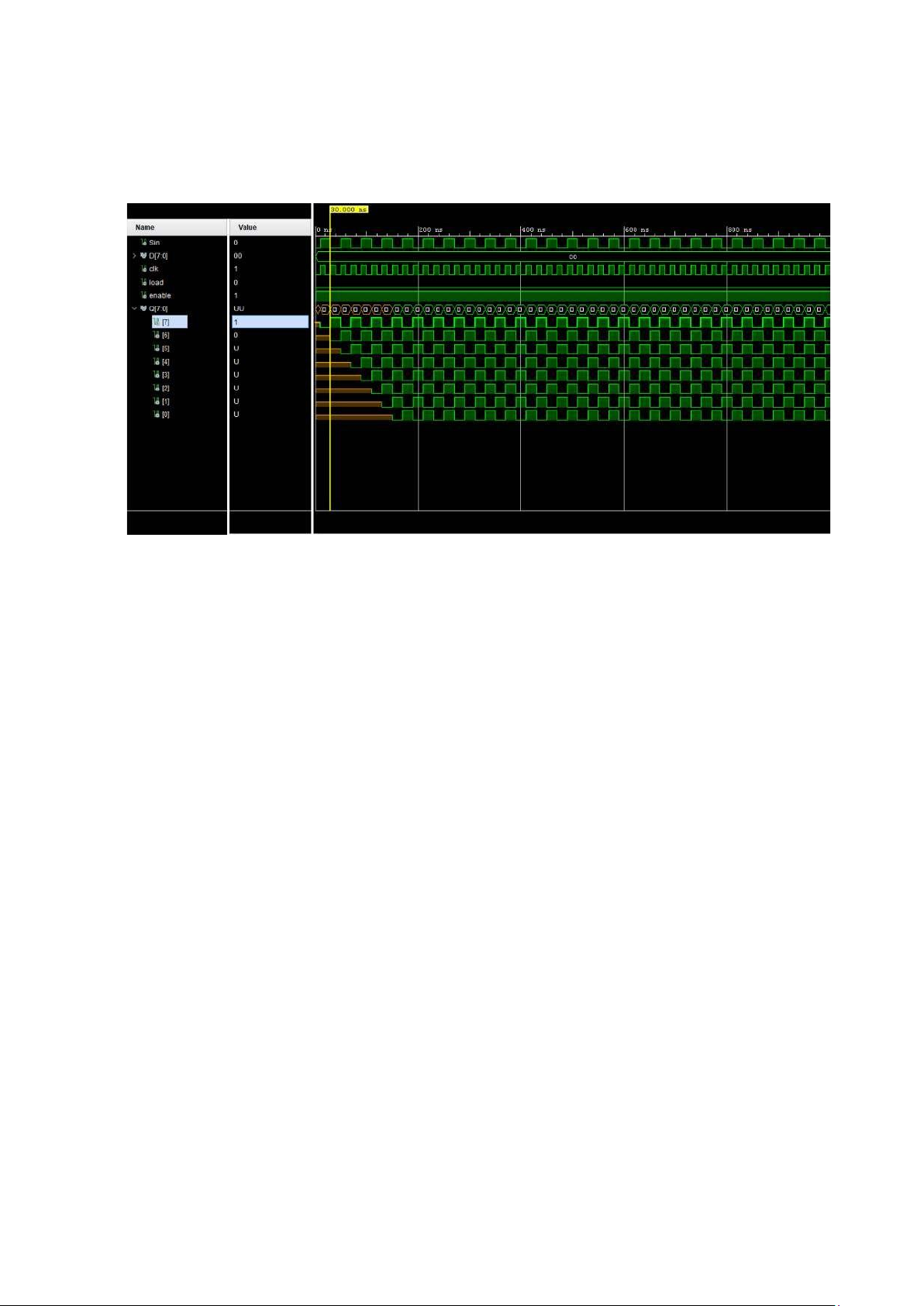

--outputs signal Q : std_logic_vector (7 downto 0) := (others => '0'); begin process(clk) begin if rising_edge(clk) then Sin <= not Sin; end if; end process;

reg_shift_inst : reg_shift PORT MAP ( Sin => Sin, D => D, clk =>

clk, load => load, enable => enable, Q => Q );

enable <= '1'; clk <= not clk after 10ns; END architecture; lOMoAR cPSD| 58815430 Kết quả

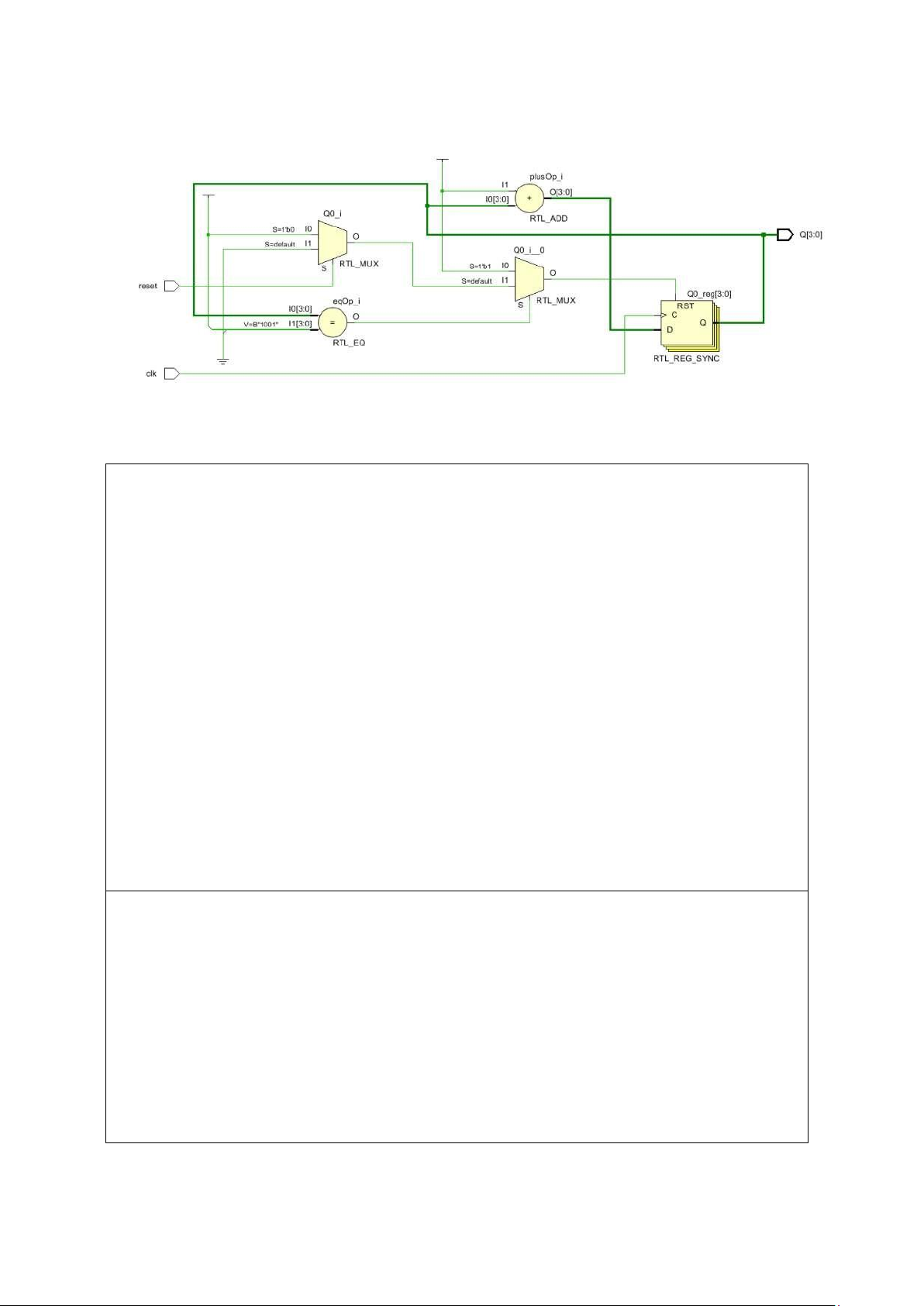

Bài 2.1 Bộ ếm lên thập phân 1 digit ơn giản, Reset ồng bộ tích cực thấp. Ý tưởng

-Bộ ếm ếm từ 0 ến 9 và tiến hành reset khi ếm ến 9 Mạch dự kiến lOMoAR cPSD| 58815430 VHDL library IEEE;

use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL; entity count_digit is

Port ( clk : in STD_LOGIC; reset : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR (3 downto 0)); end count_digit;

architecture Behavioral of count_digit is signal Q0 :

STD_LOGIC_VECTOR (3 downto 0) := "0000"; begin process(clk) begin if rising_edge(clk) then

if (reset = '0')then Q0<= "0000"; else Q0<=Q0+1; end if ;

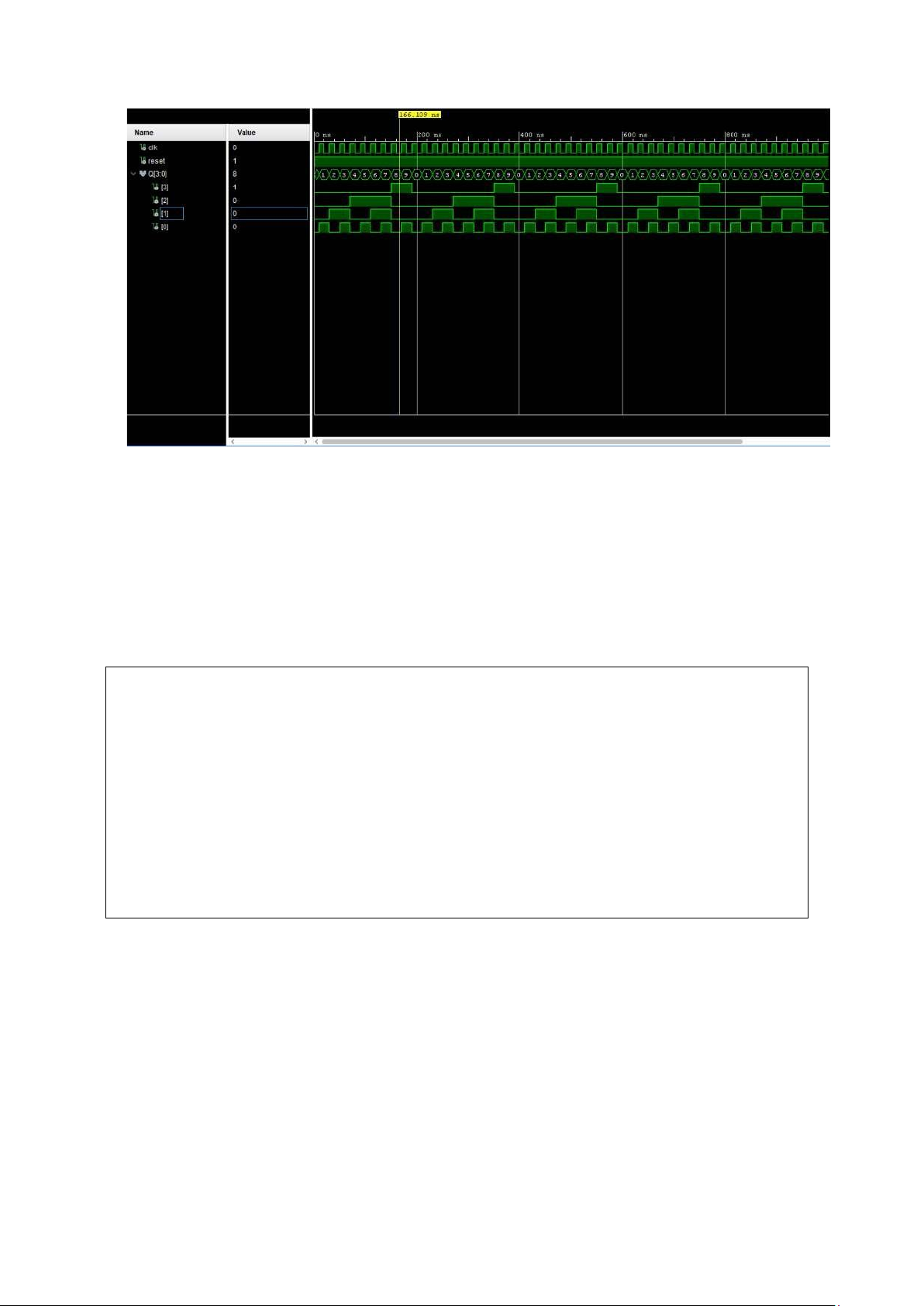

if (Q0="1001") then Q0<="0000"; end if; end if; end process; Q<=Q0; end Behavioral; Testbench lOMoAR cPSD| 58815430 library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity tb_count is end tb_count;

architecture Behavioral of tb_count is component count_digit port( clk :

in std_logic; reset : in std_logic;

Q : out std_logic_vector (3 downto 0) ); end component; -- inputs

signal clk : std_logic:='0'; signal reset : std_logic := '0'; -- outputs

signal Q: std_logic_vector (3 downto 0); begin utt: count_digit port map ( clk => clk, reset=> reset, Q=>Q );

clk <= not clk after 10ns; reset <='1'; END; Kết quả lOMoAR cPSD| 58815430

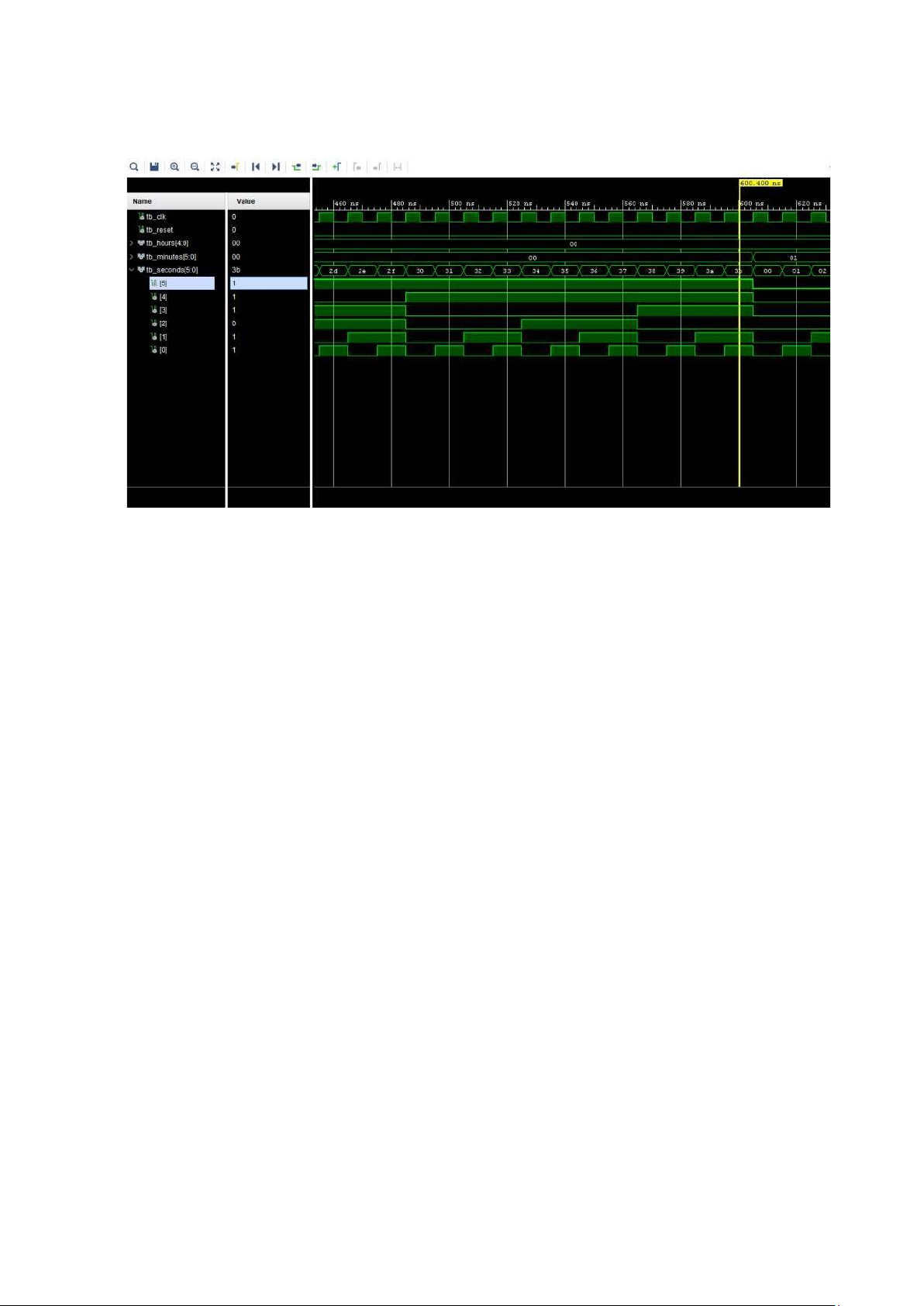

Bài 3 :Viết chương trình mô tả Mạch ồng hồ iện tử . Viết testbench ể kiểm tra hoạt ộng của mạch - Ý tưởng - Không có gì ặc biệt

Code VHDl library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all;

entity Clock is port ( reset : in std_logic; clk : in std_logic;

hours : out unsigned(4 downto 0); lOMoAR cPSD| 58815430

minutes : out unsigned(5 downto 0); seconds : out unsigned(5 downto 0) ); end entity Clock;

architecture Behavioral of Clock is signal hours_reg : unsigned(4 downto

0); signal minutes_reg : unsigned(5 downto 0); signal seconds_reg : unsigned(5 downto 0); begin

process(clk, reset) begin if reset = '1' then hours_reg <=

"00000"; minutes_reg <= "000000"; seconds_reg <= "000000";

elsif rising_edge(clk) then seconds_reg <= seconds_reg + 1; if

seconds_reg = "111011" then seconds_reg <= "000000";

minutes_reg <= minutes_reg + 1; if minutes_reg = "111011" then

minutes_reg <= "000000"; hours_reg <= hours_reg + 1; if hours_reg = "10111" then

hours_reg <= "00000"; end if; end if; end if; end if; end process;

hours <= hours_reg; minutes <= minutes_reg; seconds <= seconds_reg; end architecture Behavioral; Testbench

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity Clock_tb is lOMoAR cPSD| 58815430 end entity Clock_tb;

architecture testbench of Clock_tb is component Clock

port ( reset : in std_logic; clk : in std_logic;

hours : out unsigned(4 downto 0);

minutes : out unsigned(5 downto 0);

seconds : out unsigned(5 downto 0) );

end component; signal tb_clk :

std_logic := '0'; signal tb_reset : std_logic

:= '0'; signal tb_hours : unsigned(4 downto

0); signal tb_minutes : unsigned(5 downto

0); signal tb_seconds : unsigned(5 downto

0); begin dut: Clock port map (

reset => tb_reset, clk => tb_clk,

hours => tb_hours, minutes => tb_minutes, seconds => tb_seconds );

process begin tb_clk <= not tb_clk after 5 ns; wait for 5 ns; end process; stimulus: process begin

tb_reset <= '1'; wait for 10 ns; tb_reset <= '0'; wait for 100 ns; wait; end process; end architecture testbench; lOMoAR cPSD| 58815430 Kết quả