Preview text:

lOMoARcPSD| 36086670

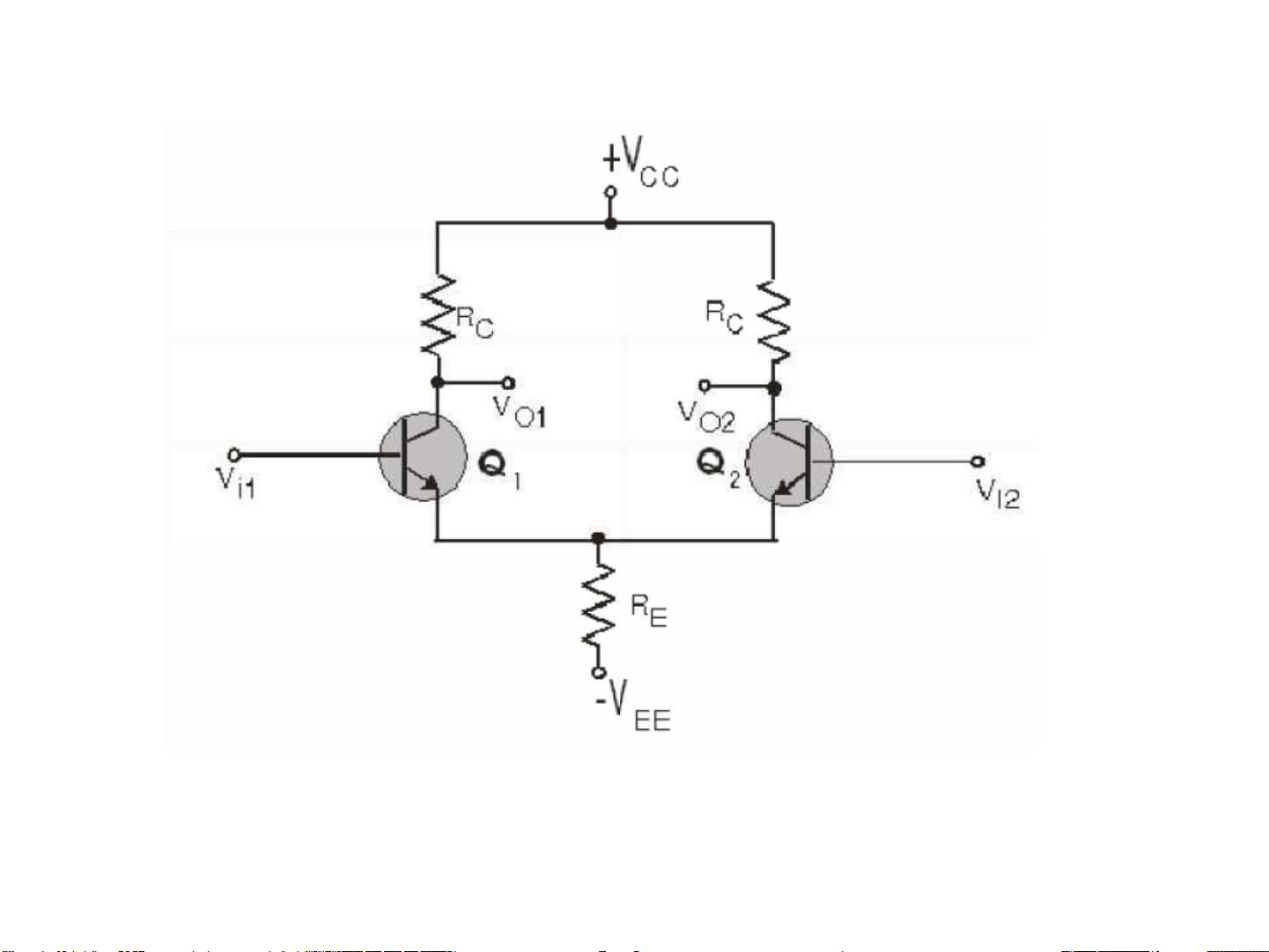

10.1 Cấu trúc mạch 10.1.1. giới thiệu lOMoARcPSD| 36086670 10.1.1. giới thiệu

Kí hiệu mạch khuếch ại lOMoARcPSD| 36086670 v lOMoARcPSD| 36086670 O h Rfe

10.1.2 Tầng khuếch ại vi C A Vd1 sai: vid1 hie

Xét tín hiệu AC – tín hiệu vi V fe h R O sai: C Vd 2 A V 2 h id ie lOMoARcPSD| 36086670

So sánh cách chung và vi sai:

Trong hoạt ộng với tín hiệu cách chung (

common mode): kết quả tín hiệu ở ngõ ra vi

sai bằng zero, vì tín hiệu ở hai cực collector

của hai transistor ối xứng nhau ối với tín hiệu này..

Và trong hoạt ộng với tín hiệu vi sai cho ộ lợi

lớn hơn rất nhiều so với tín hiệu cách chung..

10.1.2 Tầng khuếch ại vi sai: lOMoARcPSD| 36086670

10.1.2 Tầng khuếch ạiTỉ số triệt tín hiệu ồng

pha(CMRR: Common Mode Rejection Ratio)

Trong KĐVS thì một bộ KĐVS lý tưởng có AVC =

0, hay nói cách khác tín hiệu nhiễu tại mỗi ngõ ra

ơn cực phải bằng 0, nhưng thực tế khó ạt ược vì ể

AVC = 0 thì RE -> ∞. Để o lường sự sai lệch so

với lý tưởng người ta ịnh nghĩa một hệ số gọi là tỉ

số triệt tín hiệu ồng pha (CMRR): lOMoARcPSD| 36086670

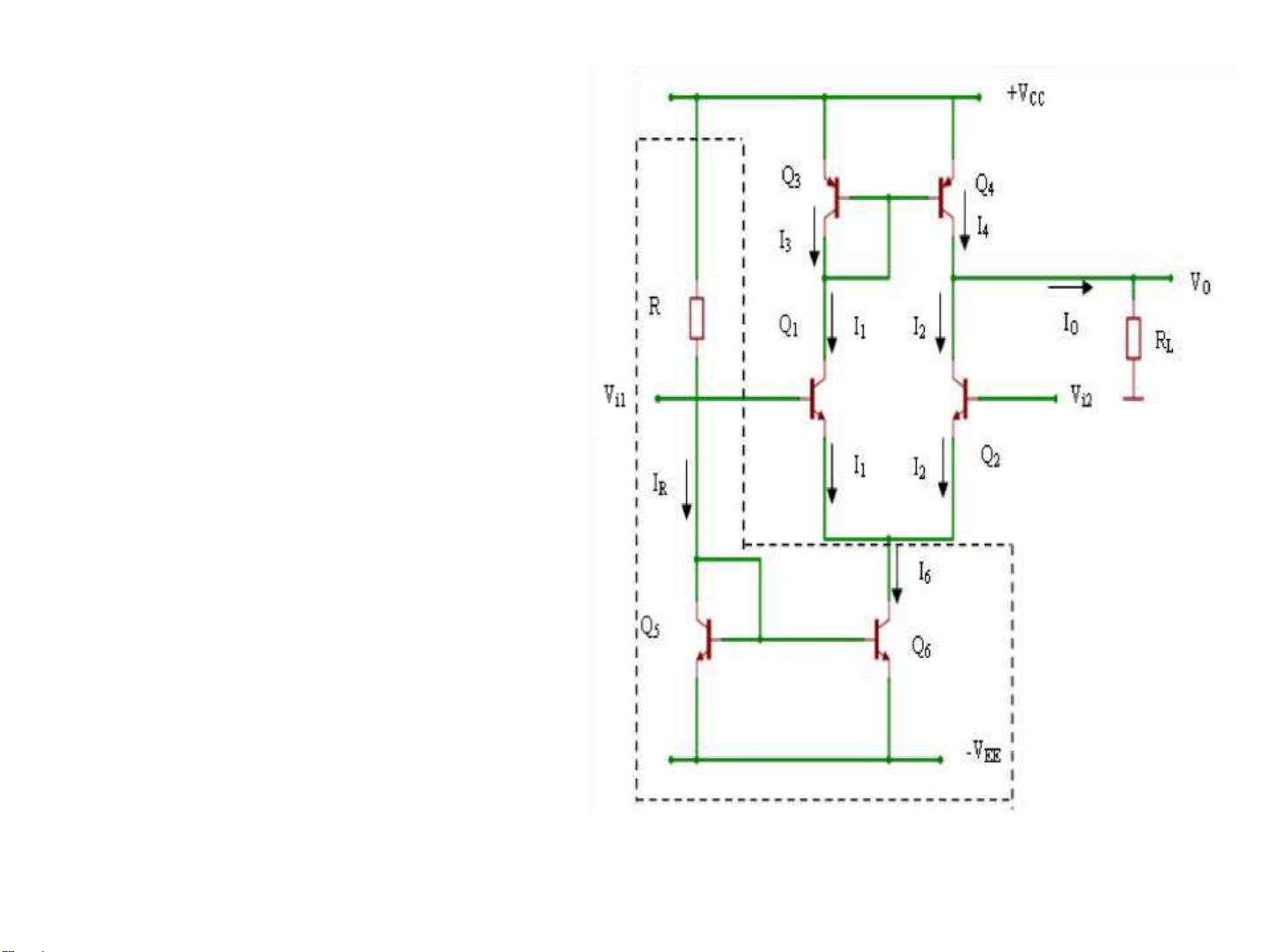

10.1.2 Tầng khuếch ại vi sai:

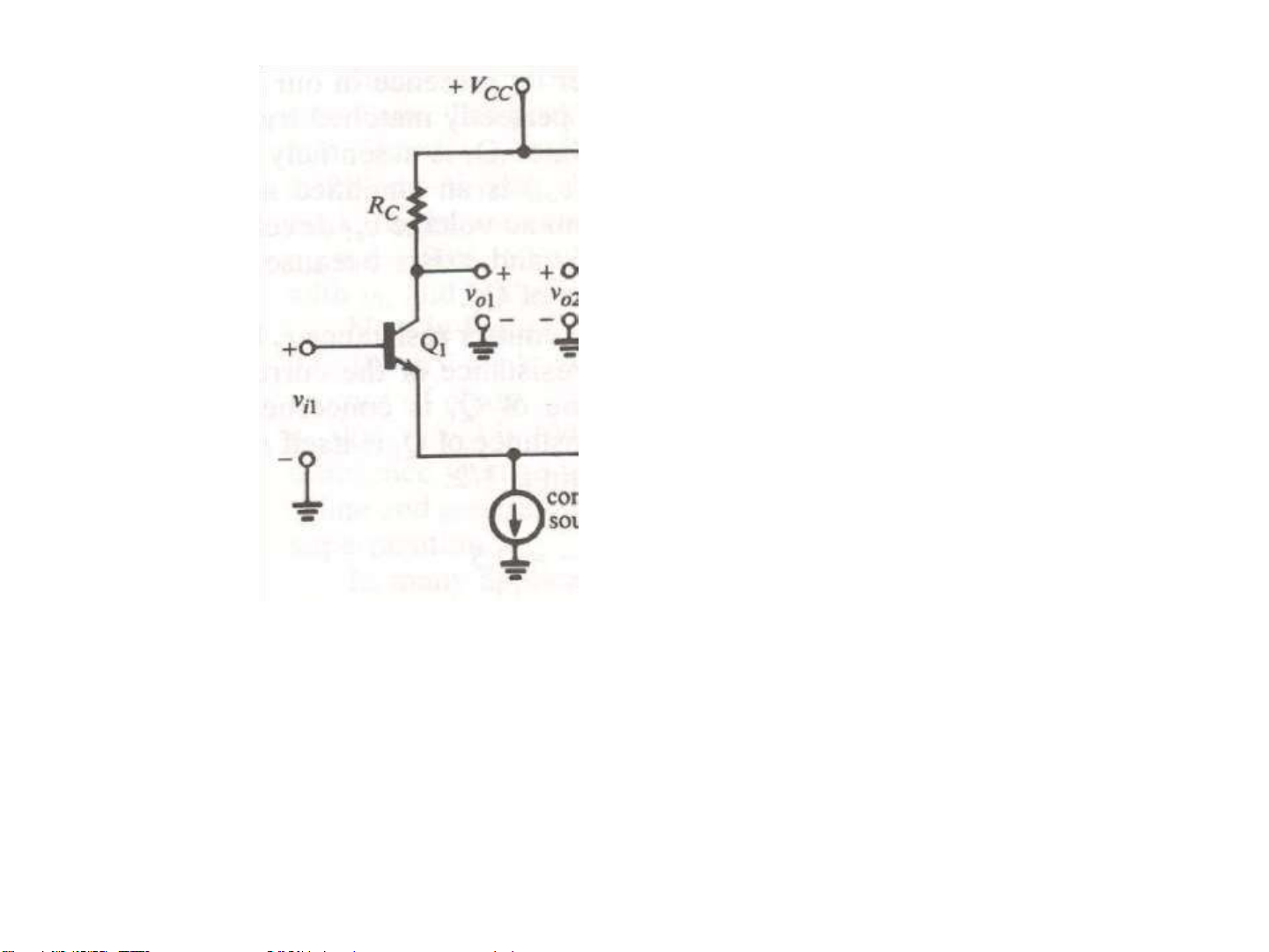

Biện pháp làm tăng hệ số CMRR

Để tăng CMRR biện pháp thường dùng là thay RE bằng một nguồn dòng. CMRR Ad AC lOMoARcPSD| 36086670

10.1.2 Tầng khuếch ại vi sai:

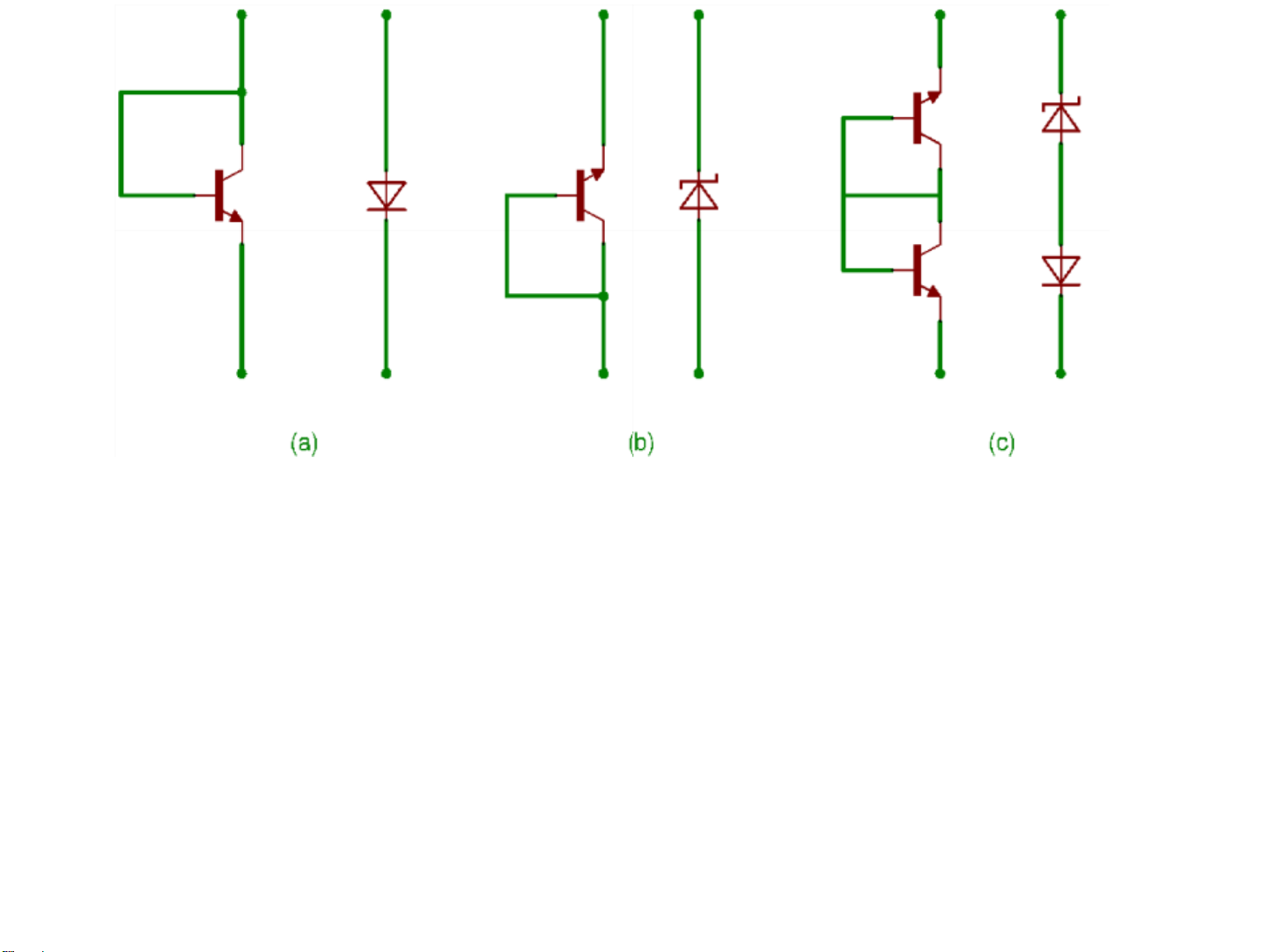

Gương dòng iện: lOMoARcPSD| 36086670

(giới thiệu gương dòng iện

cơ bản) Chức năng:

Tạo ra một nguồn dòng ổn ịnh tại cực thu của transistor.

Có iện trở ngõ ra rất lớn vì:

Nguồn dòng thường có giá

trị rất bé từ 10-100 ngõ ra

của gương dòng iện theo dạng

CB iện trở ngõ rarất lớn lOMoARcPSD| 36086670

Bus phân cực: lOMoAR cPSD| 36086670

Chính gương dòng iện cơ bản ã

tạo ra các dòng ổn ịnh có các thông số khác nhau.

Các dòng khác nhau này dựa

trên tính chất dòng iện cực

thu tỉ lệ với dòng iện bảo hòa

IS trong transistor ơn khối,

dòng iện bảo hòa tỉ lệ với

kích thước transistor và kích thước của vi mạch lOMoARcPSD| 36086670

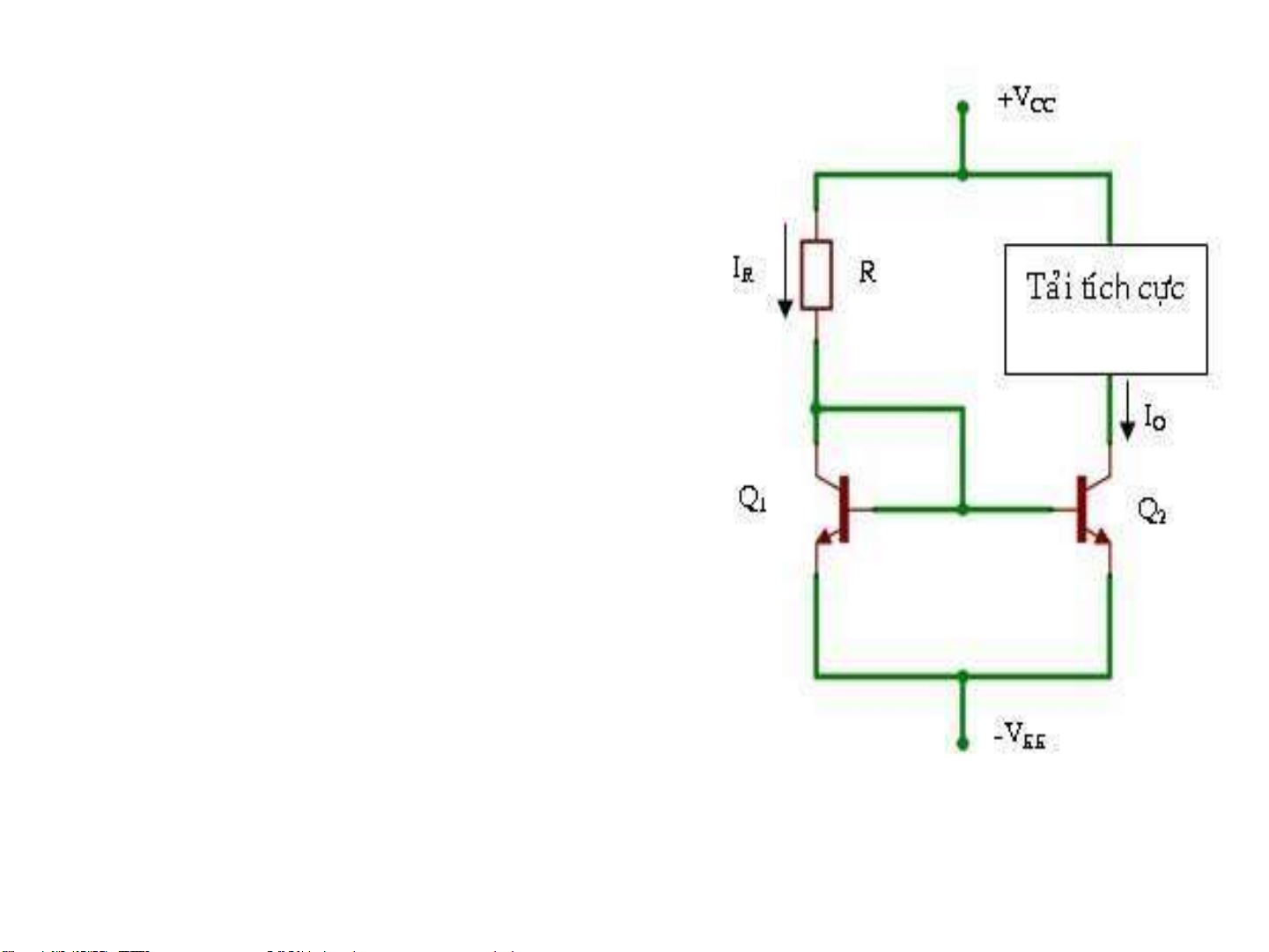

Tải tích cực: Thay vì dùng iện trở mắc nối tiếp với cực C của Q1 và Q2 trong mạch khuếch ại vi sai, người ta dùng transistor óng vai trò như iện trở ể lOMoARcPSD| 36086670

tạo thành tải tích cực

10.1.2 Tầng khuếch ại vi sai:

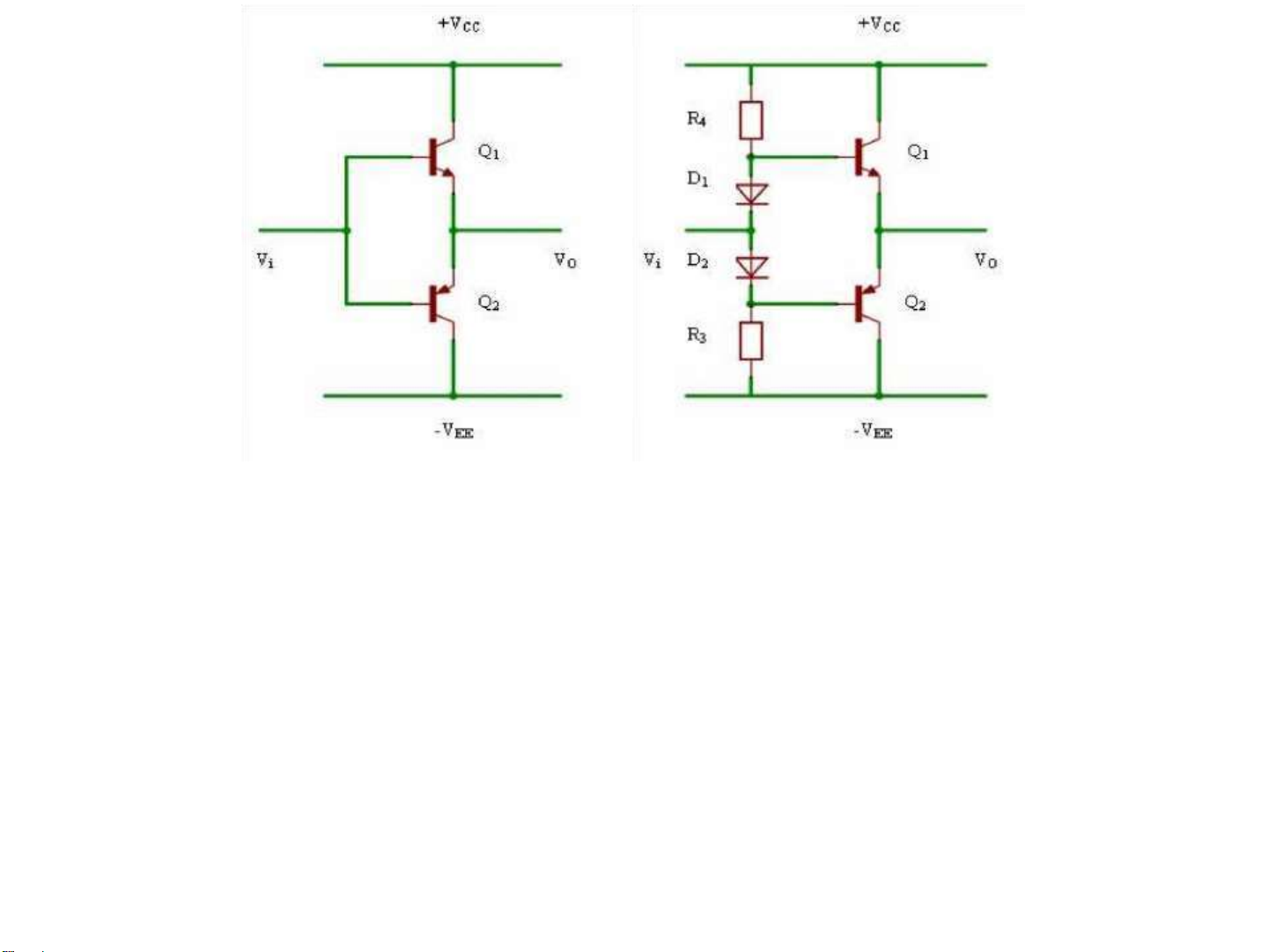

Tầng dời mức:

Tầng dời mức có chức năng là dịch mức iện áp DC tại cực

C của tầng KĐ vi sai xuống dưới mức iện áp thấp ể ngõ ra

của op-amp có mức iện áp 0VDC khi ngõ vàoVin = 0VDC . lOMoAR cPSD| 36086670

10.1.2 Tầng khuếch ại vi sai: Mạch xuất

tín hiệu ngõ ra:

Có nhiệm vụ khuếch ại dòng,có tổng trở ngõ ra nhỏ, có

khả năng cho tín hiệu AC lớn nhưng vẫn không bị lOMoAR cPSD| 36086670

méo. Các mạch xuất tín hiệu ngõ ra thường có dạng là

mạch KĐ công suất ẩy kéo.

10.1.3 Khảo sát sơ ồ nguyên lý của mạch Op-Amp lOMoAR cPSD| 36086670

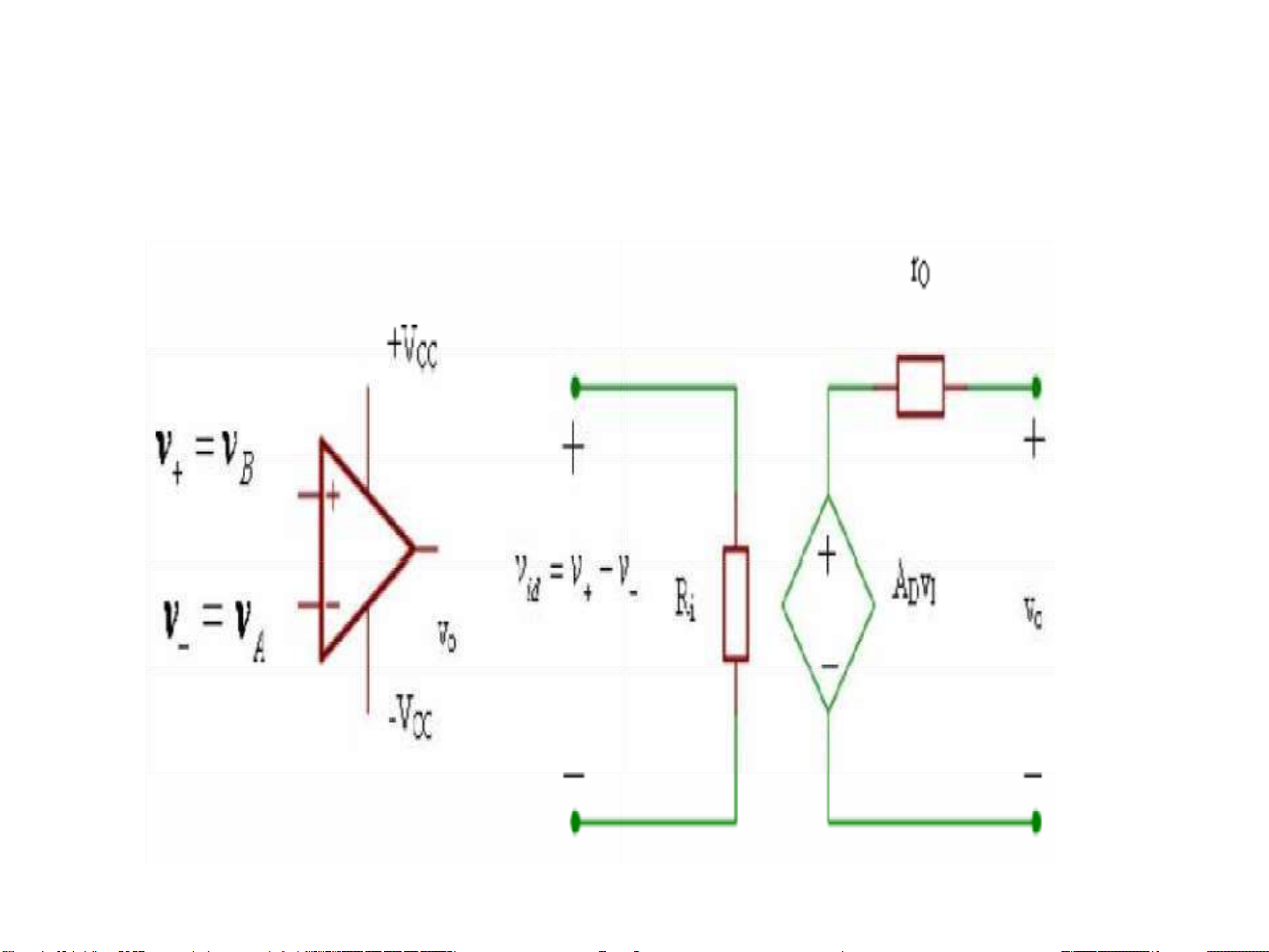

Đặc iểm của Opamp lý tưởng: lOMoAR cPSD| 36086670

Có ộ lợi áp lớn, một op- amp lý tưởng thì có ộ lợi bằng vô cùng.

Tổng trở ngõ vào lớn, lý tưởng bằng vô cùng.

Tổng trở ngõ ra bé,trường hợp lý tưởng bằng 0.

Điện áp ngõ ra bằng 0 khi iện áp vào bằng 0. lOMoAR cPSD| 36086670 lOMoARcPSD| 36086670

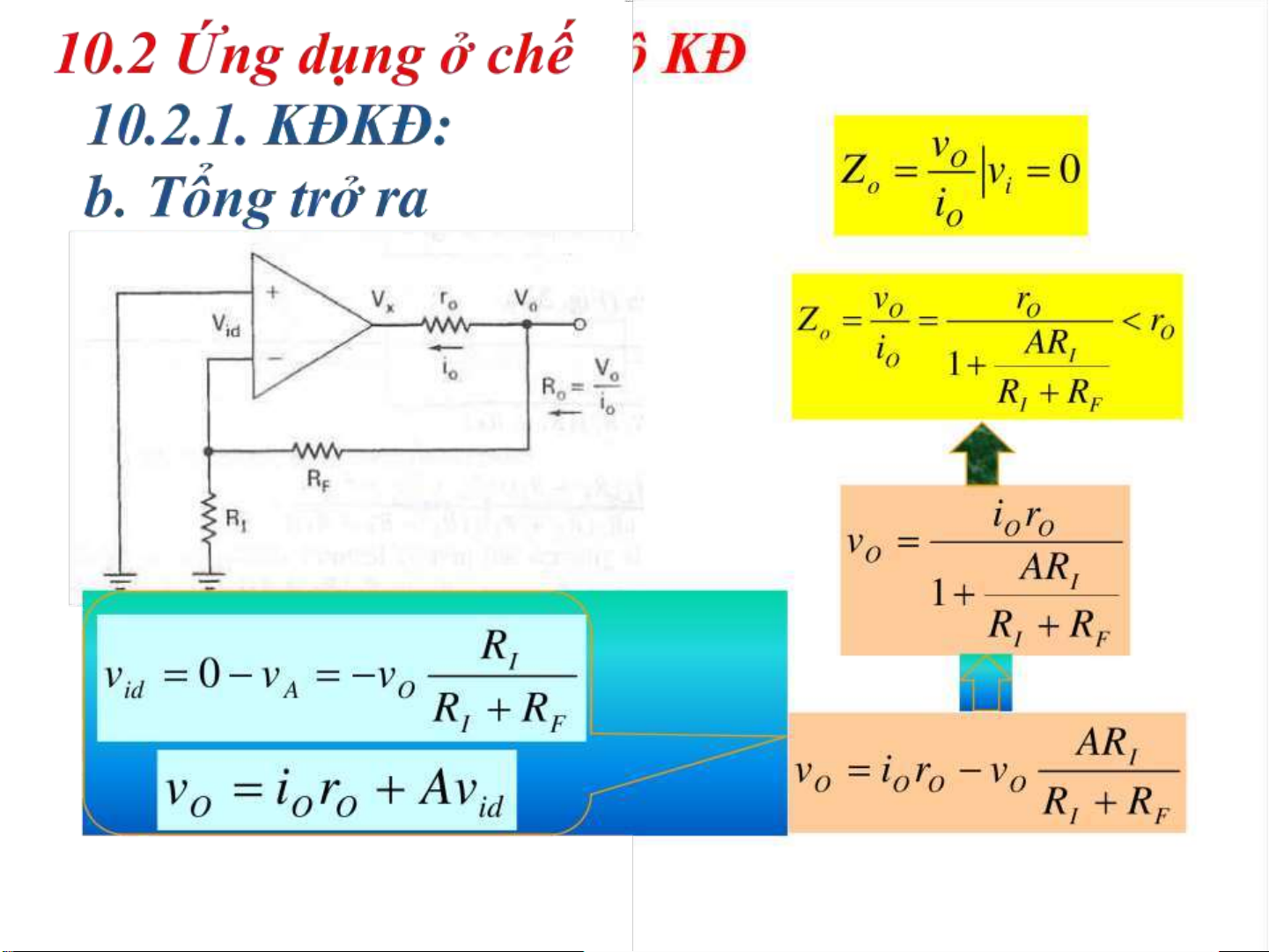

10.2 Ứng dụng ở chế ộ KĐ

10.2.2. Khuếch ại ảo: lOMoARcPSD| 36086670 Giả ịnh về dòng

iện: “ ối với op-amp lý tưởng

thì xem tổng trở vào Zi = ∞

nên có thể xem như không có

dòng iện chạy vào opamp”. 10.2 i id

v id v id 0 Ứng R i

dụng ở chế ộ KĐ

Hệ số ACLcủa KĐĐ lOMoARcPSD| 36086670

Cách 1: tính chính xácCách 2: tính gần úng

Theo giaûñònh veàaùp ta coù A CL v O

R F v i R I lOMoARcPSD| 36086670

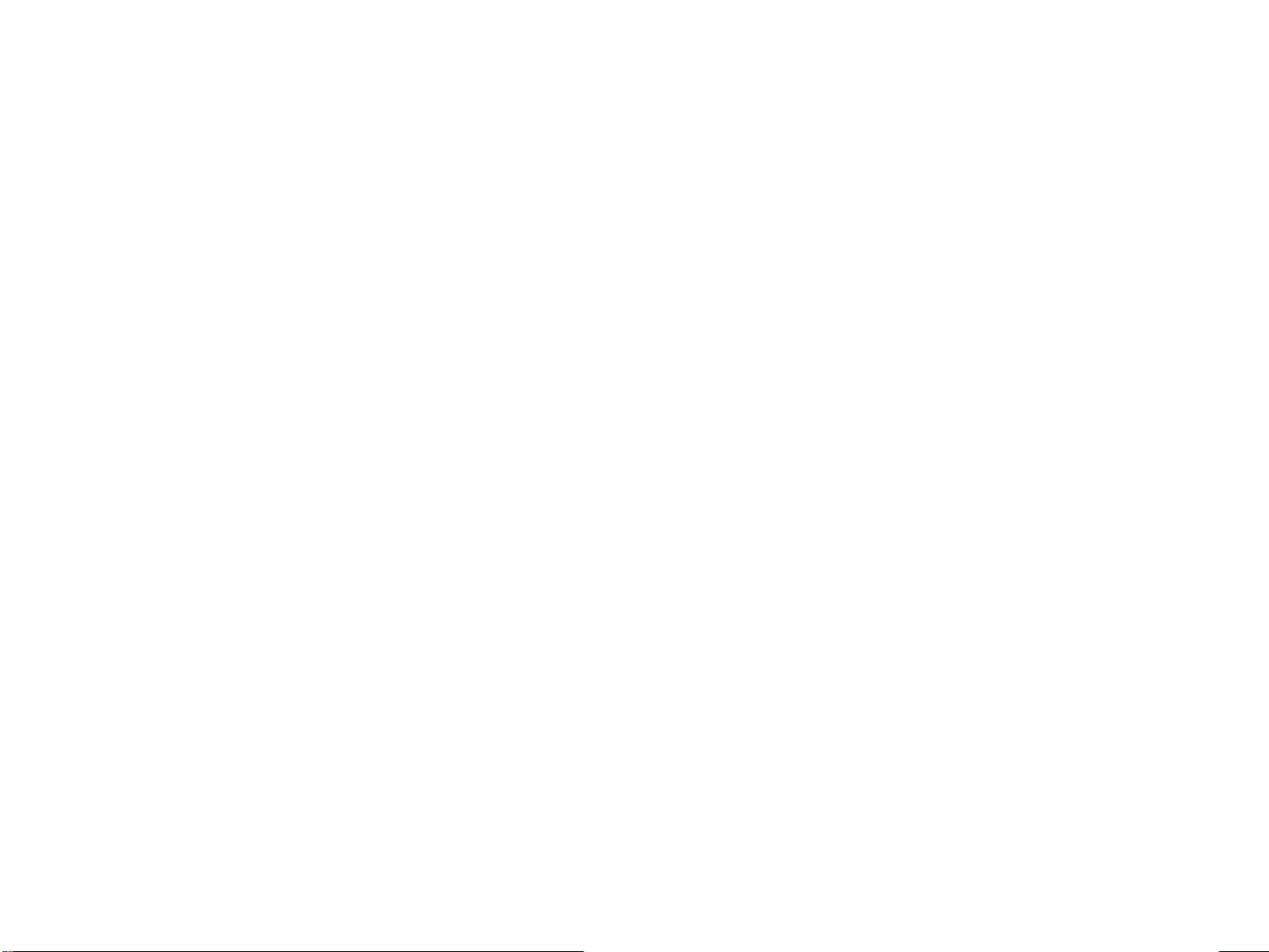

10.2.3.Mạch KĐKĐ ngõ vào cầu phân áp lOMoARcPSD| 36086670

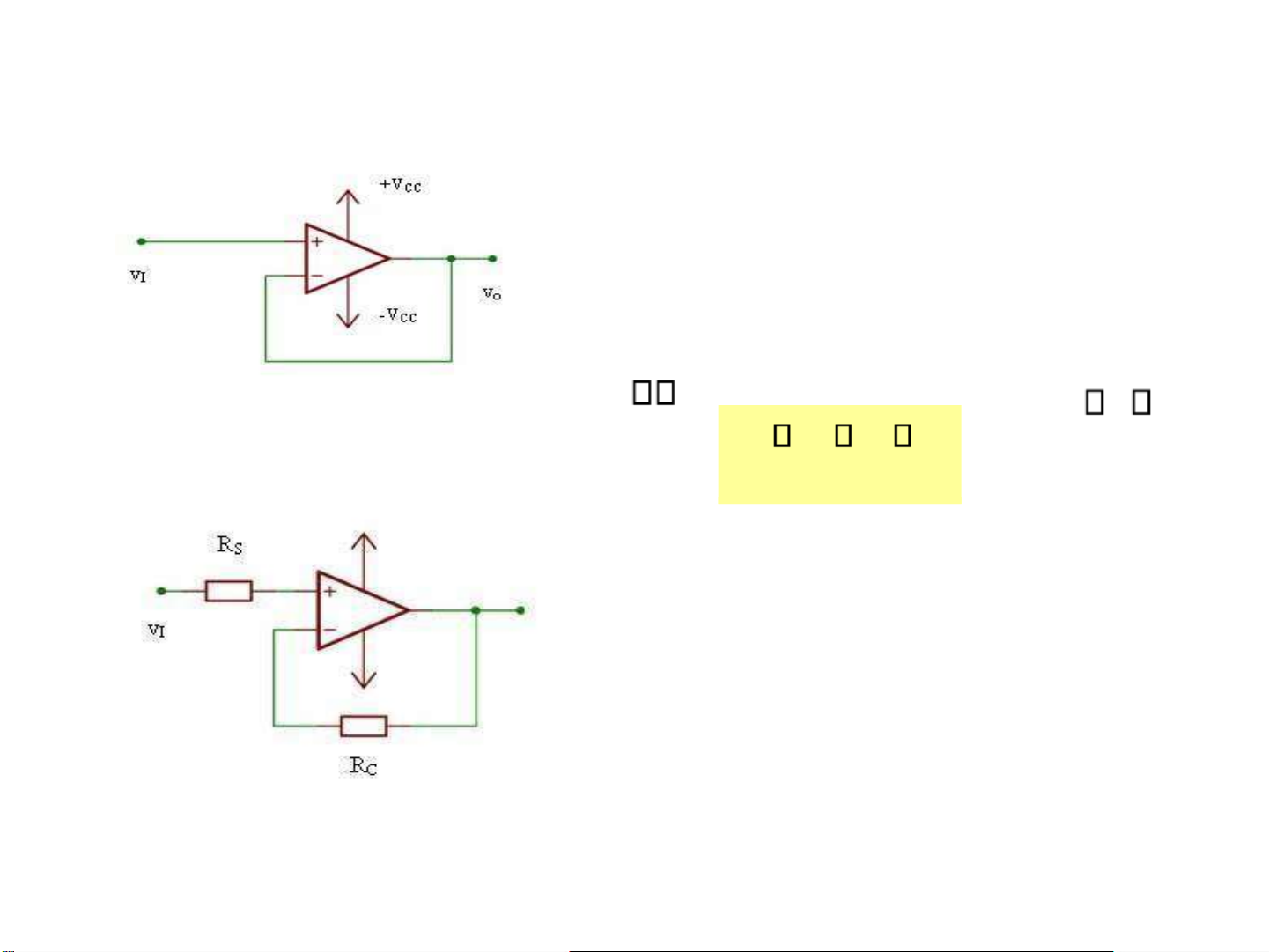

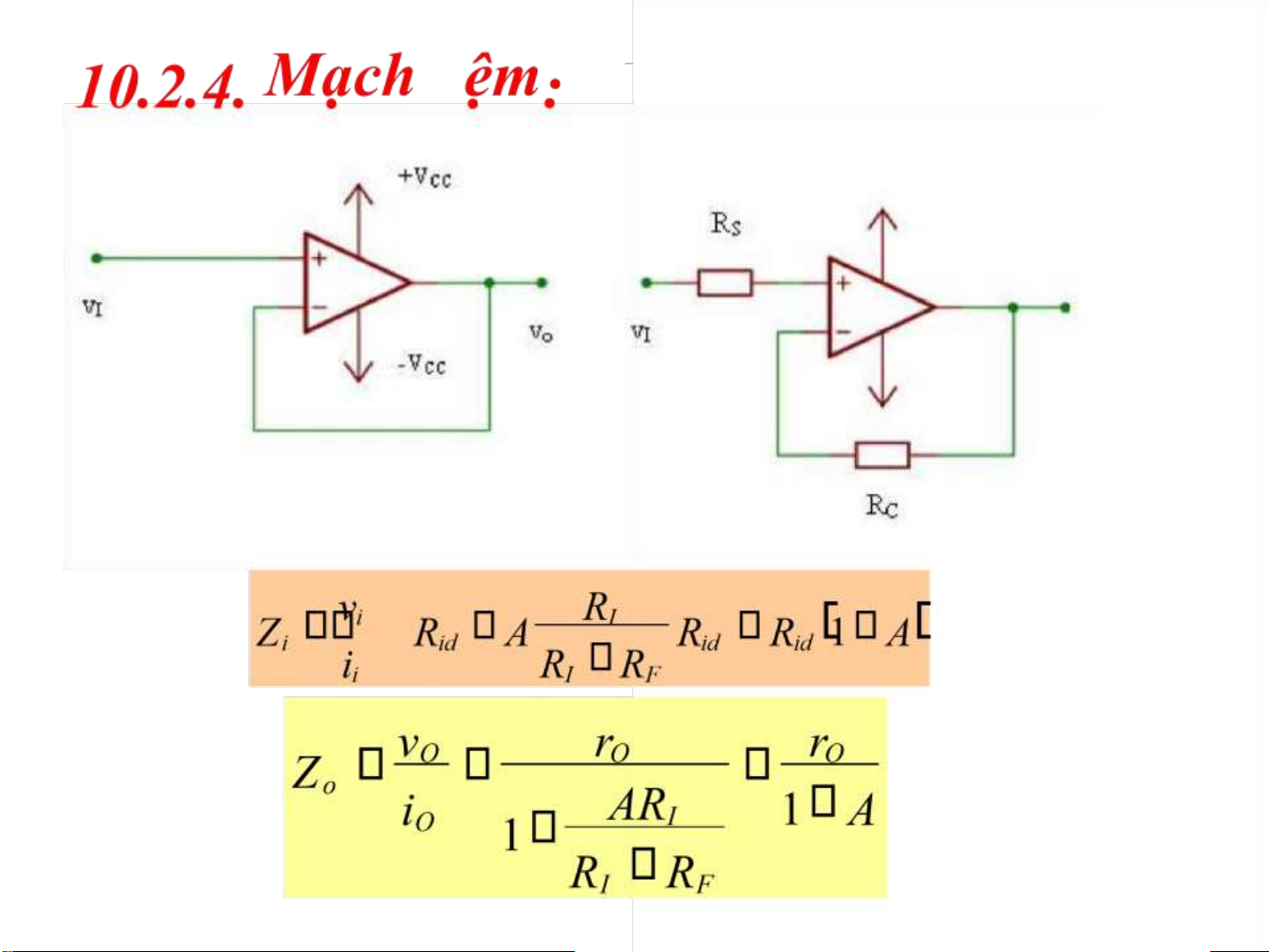

10.2.4. Mạch ệm:

Nếu tăng RI lớn hơn nhiều lần so

với RF và giảm nhỏ RF thì ta có F R RI R R RF I A v R v I CL O I 1 i I R I R có giá trị lớn nên xem như

hở mạch và RF nhỏ xem như ngắn mạch

Lúc ó mạch k k có ộ lợi =1 còn gọi là mạch KĐ ệm. lOMoARcPSD| 36086670 lOMoARcPSD| 36086670

10.2.5. Mạch cộng ảo: lOMoAR cPSD| 36086670

10.2.6. Mạch cộng không ảo trung bình

10.3. Đặc tính thực tế: lOMoAR cPSD| 36086670 Điện áp vào offset. Dòng offset

Các dòng phân cực và trôi offset.

Các yếu tố này thường xảy ra tầng khuếch ại vi sai.

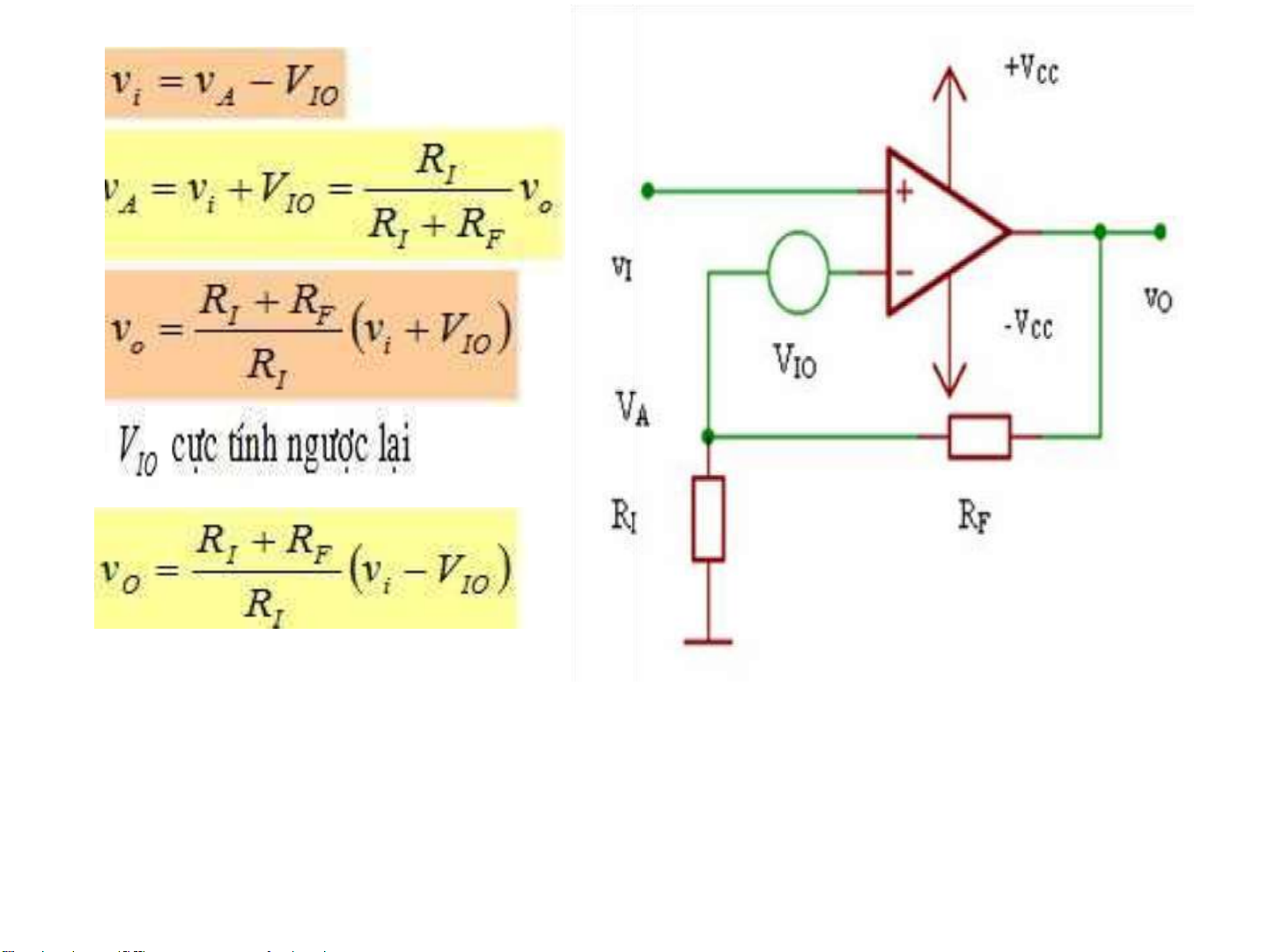

Điện áp offset: lOMoAR cPSD| 36086670

Điện áp offset ngõ ra: là iện áp chênh lệch so với iện áp ngõ ra

lý tưởng. Điện áp này có ược là do iện áp offset của ngõ vào tạo ra .

Điện áp offset ngõ vào: là do phân cực không cân bằng của

tầng KĐVS hay do 2 transistor của tầng KĐVS có các thông

số không giống nhau.Ngay khi cả hai ngõ vào nối mass(0V)

thì iện áp ngõ ra vẫn khác 0V – giá trị này ược gọi là iện áp

offset ngõ ra và ta xem như có một iện áp offset ở ngõ vào gây

ra Khảo sát ảnh hưởng Offset ngõ ra do iện áp Offset ngõ vào M ạchKĐ ảo lOMoAR cPSD| 36086670

Khảo sát ảnh hưởng Offset ngõ ra do iện áp Offset ngõ vào lOMoARcPSD| 36086670

Phương trình viếtlạinhư sau

Nếu ổicực tínhthì Mạch KĐ ảo

Khảo sát ảnh hưởng Offset ngõ ra do iện áp Offset ngõ lOMoARcPSD| 36086670 vào Mạch ảo KD không lOMoARcPSD| 36086670

Khảo sát ảnh hưởng Offset ngõ ra do iện áp Offset ngõ vào

Mạch KĐ không ảo lOMoAR cPSD| 36086670

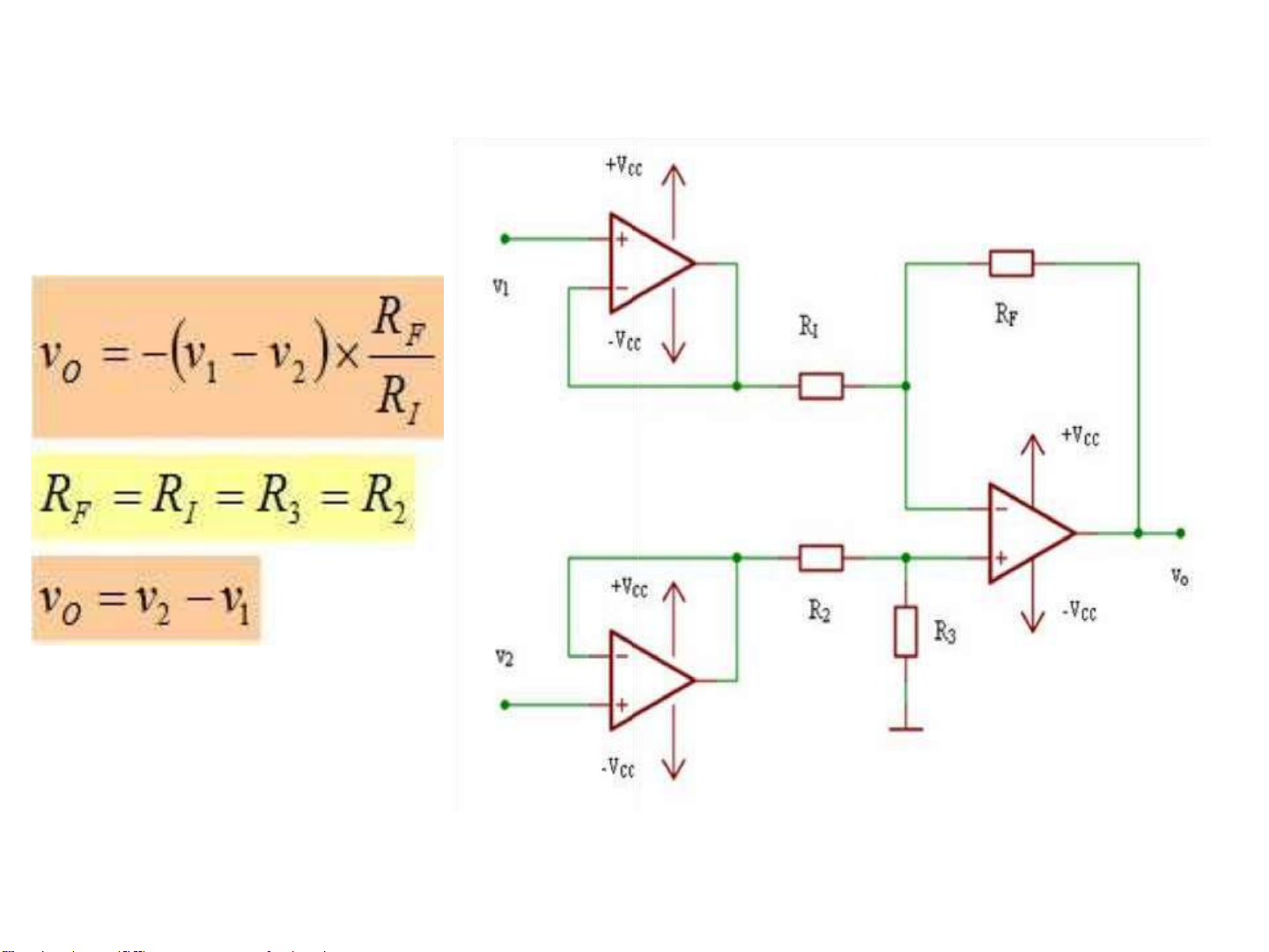

10.4. Ứng dụng Opamp ở chế ộ tuyến tính

10.4.1. Mạch KĐ vi sai-Mạch trừ lOMoARcPSD| 36086670 Nếu cho

Các mạch vi sai trong các thiết bị o lường: lOMoARcPSD| 36086670 a. dùng 3 op-amp lOMoARcPSD| 36086670 b.Dùng 2 op-amp

Điện ápraopamp thứ 1:

Điện ápraopamp thứ 2: lOMoARcPSD| 36086670

Các mạch vi sai trong các, thiết bị o lường: lOMoARcPSD| 36086670

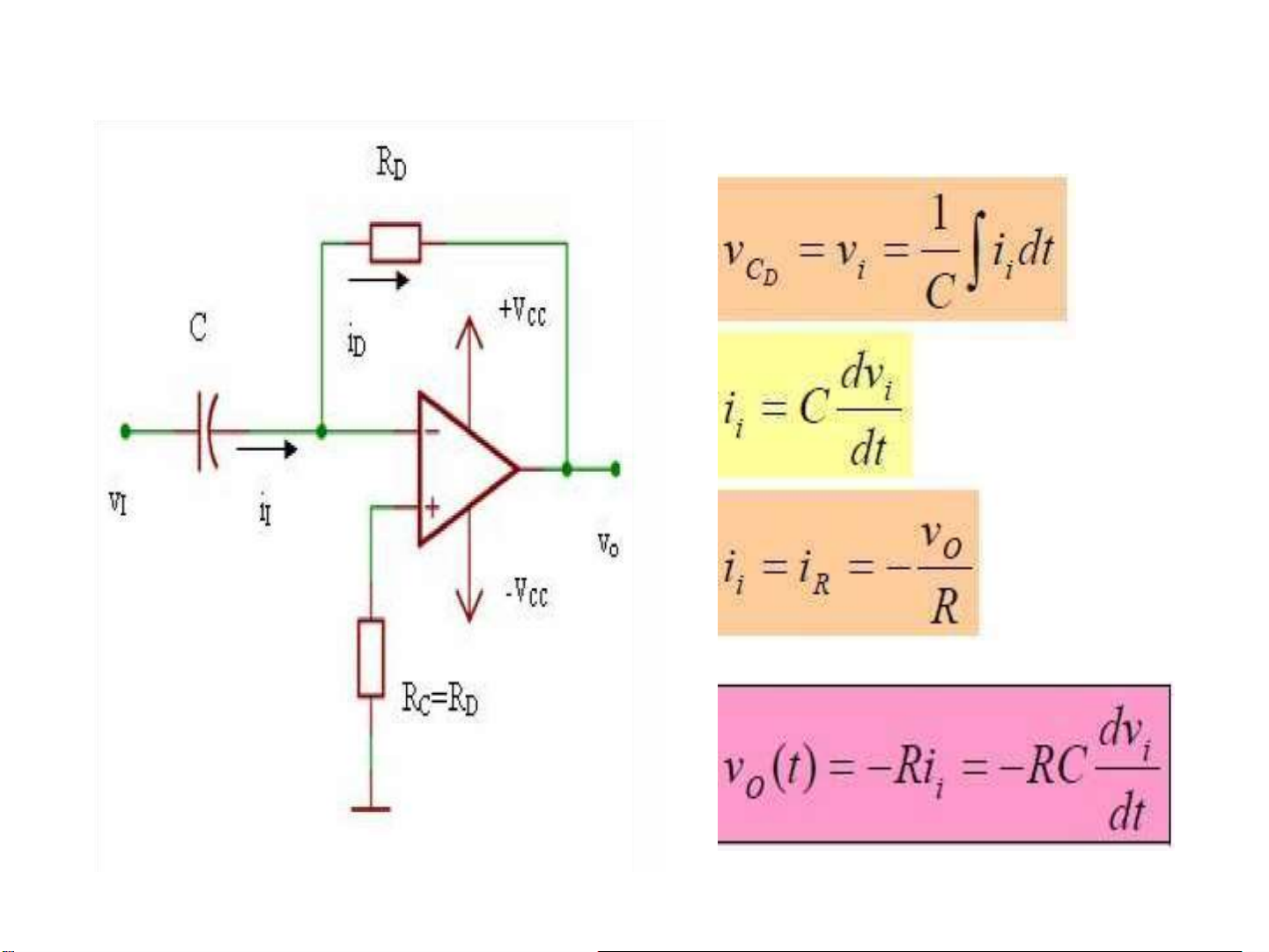

10.4.3. Mạch tích phân lOMoARcPSD| 36086670 lOMoARcPSD| 36086670

10.5. Ứng dụng op-amp trong mạch phi tuyến :

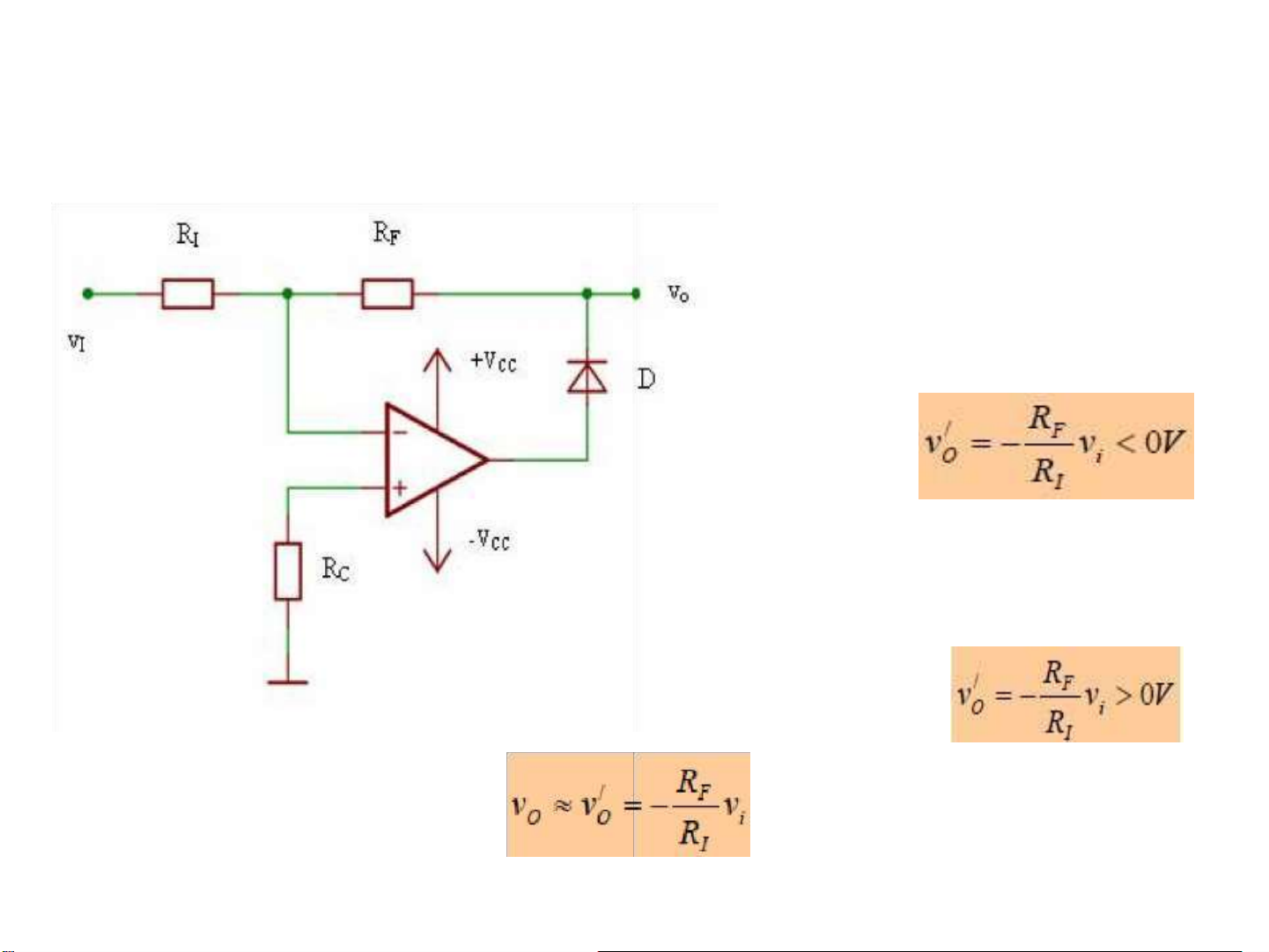

10.5.1 Chỉnh lưu bán kỳ:

Khi tín hiệu vào ở bán kỳ dương Khi tín

hiệu vào ở bán kỳ âm lOMoAR cPSD| 36086670 10.5. Ứng dụng op-

amp trong mạch phi tuyến :

10.5.2 Chỉnh lưu toàn kỳ: lOMoAR cPSD| 36086670 10.5. Ứng dụng op- :

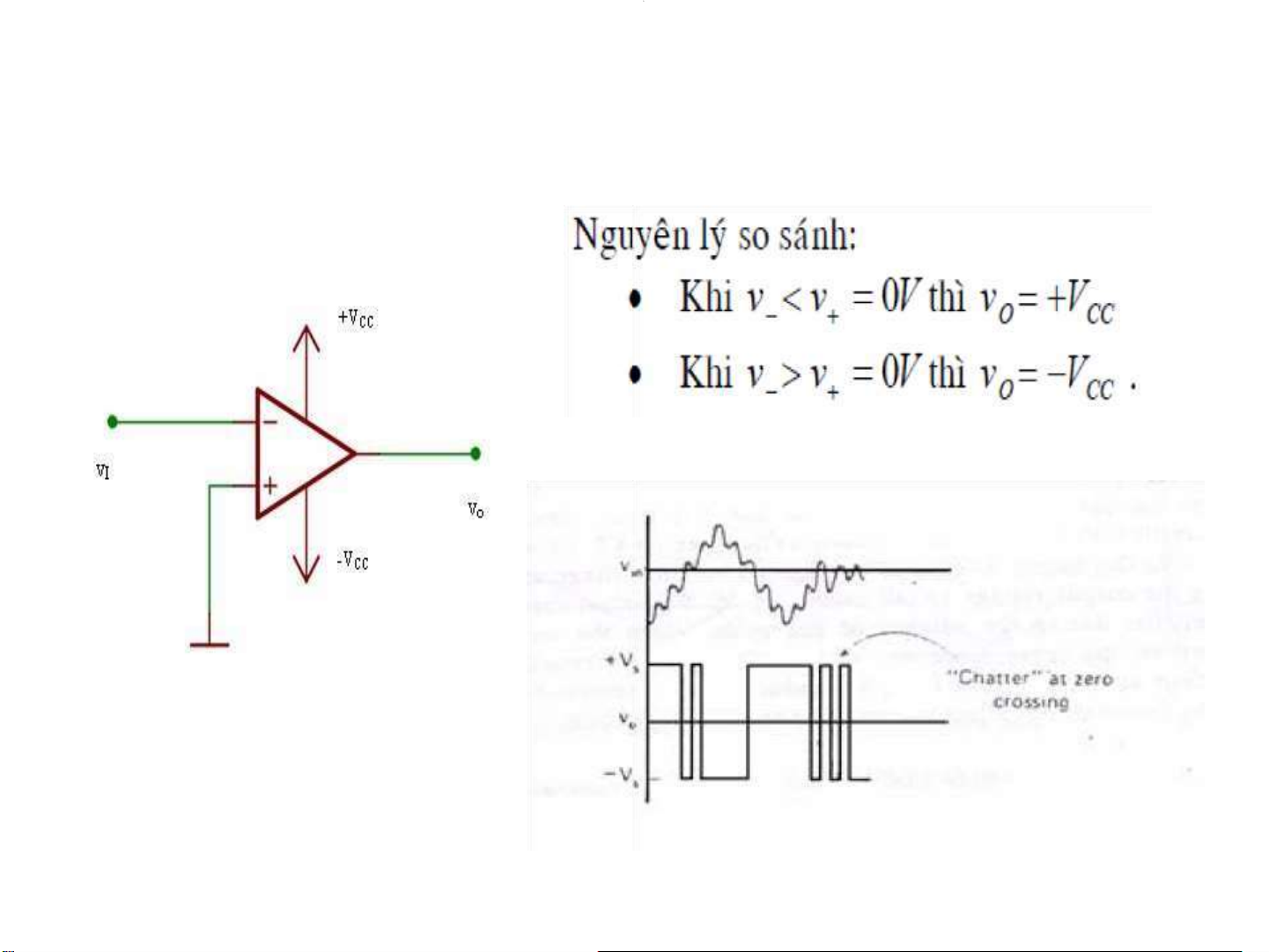

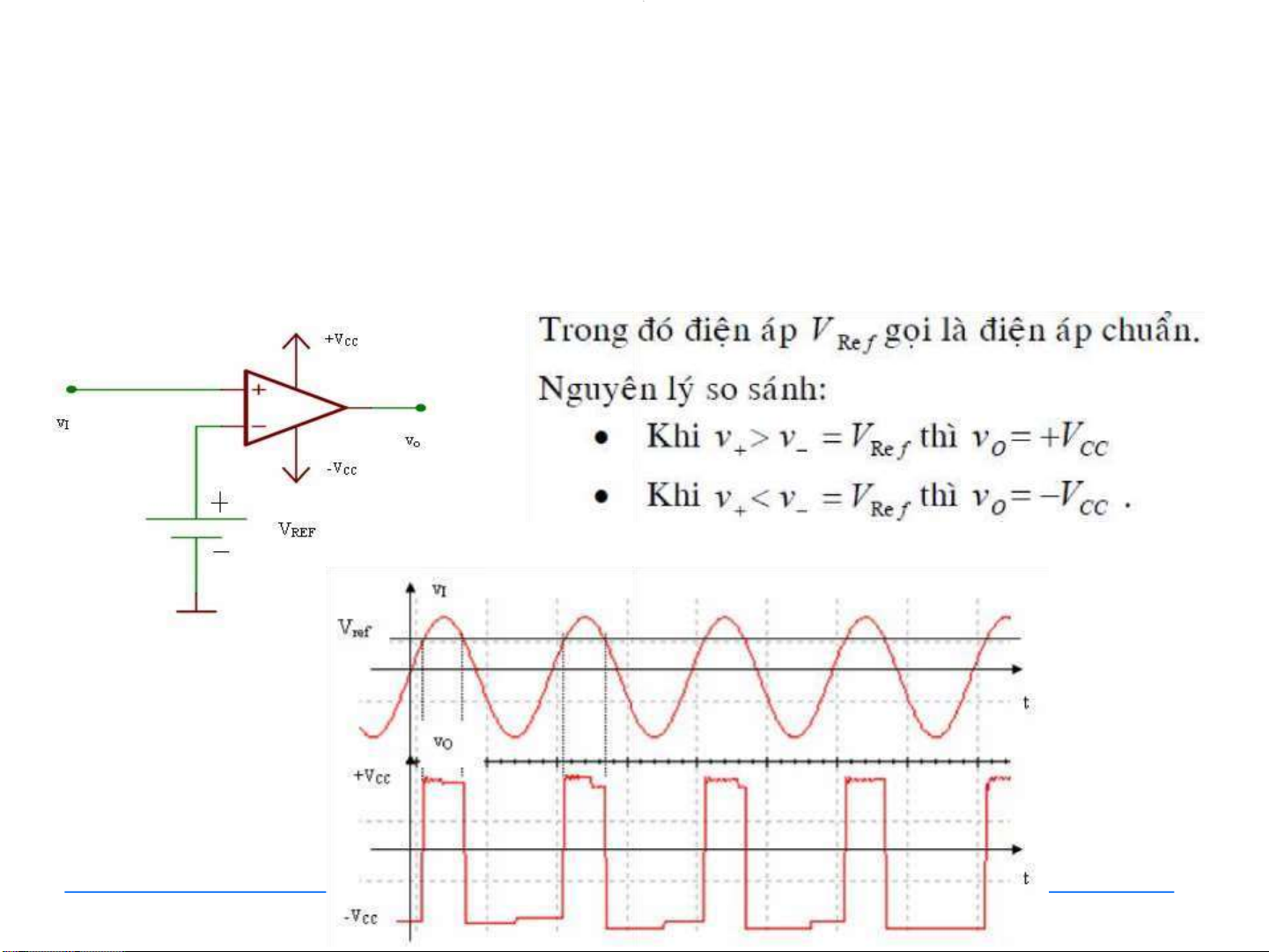

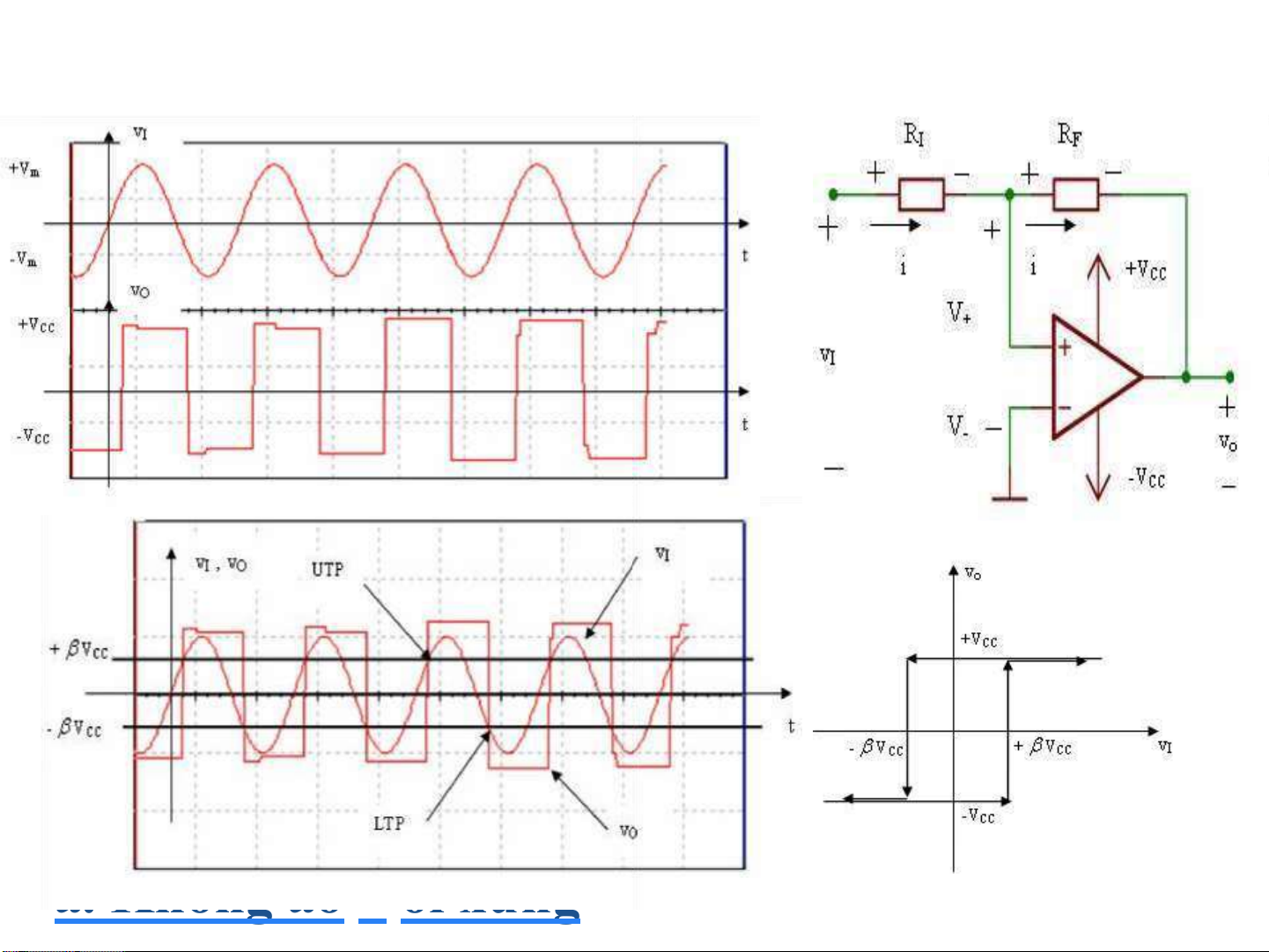

10.5.4. Mạch so sánh lOMoAR cPSD| 36086670 10.5. Ứng dụng op-

10.5.4. Mạch so sánh : lOMoAR cPSD| 36086670 10.5. Ứng dụng op-

10.5.4. Mạch so sánh lOMoAR cPSD| 36086670

10.5. Ứng dụng op-amp trong mạch phi tuyến :

10.5.4. Mạch so sánh 57 lOMoARcPSD| 36086670 lOMoARcPSD| 36086670 lOMoARcPSD| 36086670

a. Không ảo – ối xứng lOMoARcPSD| 36086670 lOMoARcPSD| 36086670